SOI晶圆片的结构特性及表征技术

描述

文章来源:学习那些事

原文作者:小陈婆婆

本文主要讲述SOI晶圆片结构及表征。

SOI晶圆片结构特性由硅层厚度、BOX层厚度、Si-SiO₂界面状态及薄膜缺陷与应力分布共同决定,其厚度调控范围覆盖MEMS应用的微米级至先进CMOS的纳米级。

除SIMOX工艺外,BOX层厚度可独立调节至纳米至微米量级,制造工艺通过表面制备步骤确保顶层硅平滑性——传统CMP工艺虽能实现减薄,但材料去除量达数十纳米易引发厚度非均匀性;而Eltran工艺采用的氢退火技术则可将SOI层厚度减少量控制在1nm以内,同时实现原子级平坦表面,厚度均匀性显著优于CMP工艺。

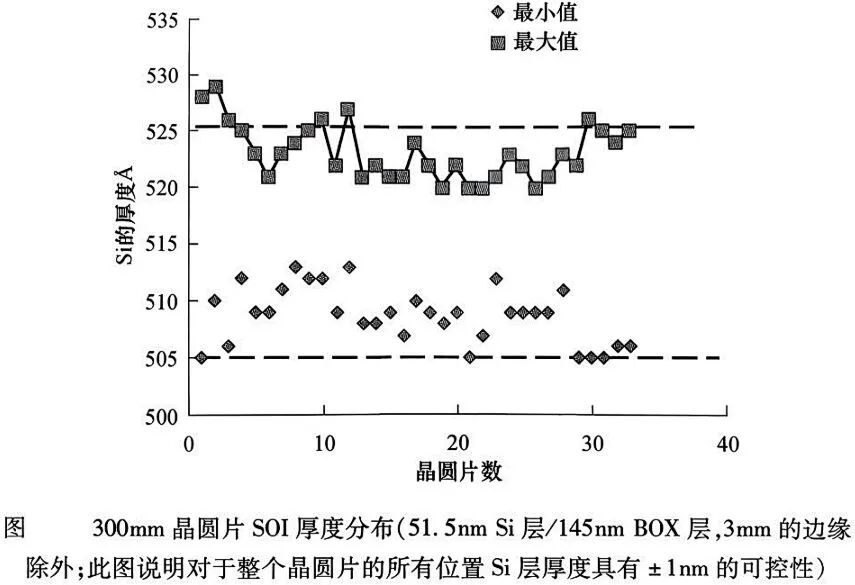

随着晶圆尺寸向大直径演进,20世纪90年代主流的100mm、150mm、200mm晶圆已逐步被300mm量产取代,450mm晶圆亦完成试产验证。以Smart CutTM工艺制备的300mm SOI晶圆片为例,其硅层厚度控制精度达±0.5nm,BOX层厚度150nm时,晶圆片内及片间厚度波动小于1nm,满足全耗尽SOI技术的大批量生产需求,这对测量技术提出更高要求——需实现亚纳米级重复性与精度以支撑工艺监控。

结构表征技术

结构表征方面,常规物理化学技术如椭偏仪、X射线衍射/反射、RBS、SIMS、FTIR、TEM及AFM广泛应用于在线/离线检测,其中AFM在1μm²面积测得的表面粗糙度有效值通常低于0.15nm。针对CMOS应用对膜层完整性的严苛要求,行业开发了专用表征技术:稀释Secco腐蚀通过缺陷周围应力优先腐蚀形成腐蚀坑,结合HF腐蚀暴露埋氧化层缺陷,实现缺陷密度光学测量;KLA-Tencor SP-DLS系统可扫描整个晶圆片表面,结合SEM验证缺陷穿透性,使智能剥离工艺制备的300mm SOI晶圆片HF缺陷密度降至0.05个/cm²以下。界面质量表征显示,低剂量SIMOX晶圆片经1320℃退火6小时后,顶硅-BOX界面呈现粗糙方形镶嵌图案,源于氧注入损伤与结晶硅层混合;延长退火时间可促使界面平滑化,形成螺旋/阶梯型图案,阶梯高度为硅晶格常数倍数。键合SOI晶圆片通过1100℃退火可获高质量顶硅-BOX界面,透射电镜观察证实其结构完整性。

电学性能表征

电学性能表征是SOI应用的核心,伪MOS晶体管技术通过测量顶层硅掺杂类型、载流子迁移率、界面陷阱密度及载流子复合寿命,补充霍尔效应、扩展电阻、光电导等标准方法。研究表明,智能剥离工艺制备的SOI晶圆片经高温退火后,氢完全扩散,单晶性质得以保留,载流子迁移率达电子650cm²/Vs、空穴240cm²/Vs,界面陷阱密度低于3×10¹¹ eV⁻¹·cm⁻²,载流子寿命超100μs,优于SIMOX工艺。300mm SIMOX与智能剥离SOI晶圆片已证实具备可靠性与可重复性,可满足高性能晶体管及试验器件制造需求,其顶层硅为高质量单晶,电学性能优异,埋氧化层与界面质量达应用要求。

当前,SOI晶圆片表征技术正朝着更高精度、非破坏性及智能化方向发展。例如,纳米束电子衍射(NBD)可实现亚纳米级缺陷定位,机器学习算法应用于缺陷分类与良率预测,显著提升检测效率。在绿色制造方面,Soitec通过供体晶圆重复利用与低能耗沉积工艺,将碳化硅基板生产碳排放降低四倍,契合半导体产业低碳化趋势。

新兴应用领域如量子计算中,SOI基硅锗异质结量子点阵列实现单量子比特操控保真度99.9%;5G/6G通信中,SOI基射频器件插入损耗较传统硅基器件降低30%,成为毫米波前端模块首选方案。这些进展共同推动SOI技术在射频、功率、光电子及量子计算等前沿领域的持续创新与价值重构。

-

晶圆的结构是什么样的?2011-12-01 10718

-

制备出国际一流的SOI晶圆片 王曦发布豪杰壮语2018-07-14 2623

-

Soitec与三星晶圆代工厂扩大合作 保障FD-SOI晶圆供应2019-01-22 962

-

晶圆结构_晶圆用来干什么2019-05-09 12949

-

SOI晶圆目前的发展现况与未来规划2019-06-19 10887

-

环球晶圆将为格芯供应12英寸的SOI晶圆2020-02-26 3722

-

上海微系统所在300mm RF-SOI晶圆制造技术方面实现突破2023-10-23 2459

-

国内第一片300mm射频(RF)SOI晶圆的关键技术2023-11-21 2918

-

浅谈SOI晶圆制造技术的四大成熟工艺体系2025-12-26 907

全部0条评论

快来发表一下你的评论吧 !