FPGA仿真方法及仿真程序的编写介绍

描述

一、概述

FPGA仿真方法:

(1)交互式仿真方法:利用EDA工具的仿真器进行仿真,使用方便,但输入输出不便于记录规档,当输入量较多时不便于观察和比较。

(2)测试平台法:为设计模块专门设计的仿真程序,可以实现对被测模块自动输入测试矢量,并通过波形输出文件记录输出,便于将仿真结果记录归档和比较。

二、仿真程序的设计方法

1 仿真的三个阶段

(1)行为仿真:目的是验证系统的数学模型和行为是否正确,对系统的描述的抽象程度较高。在行为仿真时,VHDL的语法语句都可以执行。

(2)RTL仿真:目的是使被仿真模块符合逻辑综合工具的要求,使其能生成门级逻辑电路。在RTL仿真时,不能使用VHDL中一些不可综合和难以综合的语句和数据类型。该级仿真不考虑惯性延时,但要仿真传输延时。

(3)门级仿真:门级电路的仿真主要是验证系统的工作速度,惯性延时仅仅是仿真的时候有用在综合的时候将被忽略。

2 仿真程序的内容

(1)被测实体的引入。

(2)被测实体仿真信号的输入。

(3)被测实体工作状态的激活。

(4)被测实体信号的输出

(5)被测实体功能仿真的结果比较,并给出辨别信息

(6)被测实体的仿真波形比较处理

3 仿真要注意的地方

(1)仿真信号可以由程序直接产生,也可以用TEXTIO文件产生后读入。

(2)仿真程序中可以简化实体描述,省略有关端口的描述。仿真程序实体描述的简化形式为:

ENTITY 测试平台名 IS

END 测试平台名;

(3)对于功能仿真结果的判断,可以用断言语句(ASSORT)描述。

(4)为了比较和分析电子系统的功能,寻求实现指标的最佳结构,往往利用一个测试平台对实体的不同结构进行仿真,一般是应用配置语句为同一被测实体选用多个结构体。

CONFIGURATION 测试平台名 OF 被测实体名 IS

FOR 被测实体的A的结构体名

END FOR;

END 测试平台名;

同样,若选用结构体B,则配置语句可写为:

CONFIGURATION 测试平台名 OF 被测实体名 IS

FOR 被测实体的B的结构体名

END FOR;

END 测试平台名;

4 VHDL仿真程序结构

测试平台仅仅是用于仿真,因此可以利用所有的行为描述语言进行描述,下表表示了一个测试平台所包含的部分,典型的测试平台将包括测试结果和错误报告结果。

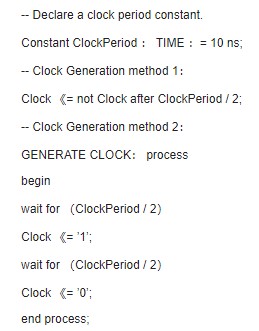

(1)产生时钟信号

(2)提供仿真信号

提供仿真信号可以有两种方法:绝对时间仿真和相对时间仿真。在绝对时间仿真方法中,仿真时间只是相对于零时刻的仿真时间。在相对时间仿真方法中,仿真的时间首先提供一个初值,在后继的时间设置中相对于该初始时间进行事件动作。

绝对时间仿真:

MainStimulus: process begin

Reset 《= ’1’;

Load 《= ’0’;

Count_UpDn 《= ’0’;

wait for 100 ns;

Reset 《= ’0’;

wait for 20 ns;

Load 《= ’1’;

wait for 20 ns;

Count_UpDn 《= ’1’;

end process;

相对时间仿真:

Process (Clock)

Begin

If rising_edge(Clock) then

TB_Count 《= TB_Count + 1;

end if;

end process;

SecondStimulus: process begin

if (TB_Count 《= 5) then

Reset 《= ’1’;

Load 《= ’0’;

Count_UpDn 《= ’0’;

Else

Reset 《= ’0’;

Load 《= ‘1’;

Count_UpDn 《= ‘1’;

end process;

FinalStimulus: process begin

if (Count = “1100”) then

Count_UpDn 《= ‘0’;

report “Terminal Count

Reached, now counting down.”

end if;

end process;

(3)显示结果

VHDL提供标准的std_textio函数包把输入输出结果显示在终端上。

5 简单的仿真程序

library IEEE;

use IEEE.std_logic_1164.all;

entity testbench is

end entity testbench;

architecture test_reg of testbench

component shift_reg is

port (clock : in std_logic;

reset : in std_logic;

load : in std_logic;

sel : in std_logic_vector(1 downto 0);

data : in std_logic_vector(4 downto 0);

shiftreg : out std_logic_vector(4 downto 0));

end component;

signal clock, reset, load: std_logic;

signal shiftreg, data: std_logic_vector(4 downto 0);

signal sel: std_logic_vector(1 downto 0);

constant ClockPeriod : TIME := 50 ns;

begin

UUT : shift_reg port map (clock =》 clock, reset =》 reset,

load =》 load, data =》 data,

shiftreg =》 shiftreg);

process begin

clock 《= not clock after (ClockPeriod / 2);

end process;

process begin

reset 《= ’1’;

data 《= “00000”;

load 《= ’0’;

set 《= “00”;

wait for 200 ns;

reset 《= ’0’;

load 《= ’1’;

wait for 200 ns;

data 《= “00001”;

wait for 100 ns;

sel 《= “01”;

load 《= ’0’;

wait for 200 ns;

sel 《= “10”;

wait for 1000 ns;

end process;

end architecture test_reg;

6 TEXTIO建立测试程序

在由仿真程序直接产生输入信号的方法中,测试矢量是仿真程序的一个部分,如果系统比较复杂,测试矢量的数目非常大,修改测试矢量时就必须修改程序,重新编译和仿真。工作量大。因此,在测试矢量非常大的时候可以用TEXTIO的方法来进行仿真。

TEXTIO仿真方法:测试矢量从仿真程序中分离出来,单独存于一个文件中(即TEXTIO文件),在仿真时,根据定时要求按行读出,并赋予相应的输入信号。这种方法允许采用同一个测试平台,通过不同的测试矢量文件进行不同的仿真。值得注意的是,测试矢量文件的读取,需要利用TEXTIO程序包的功能。在TEXTIO程序包中,包含有对文本文件进行读写的过程和函数。

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

LIBRARY ieee;

USE IEEE.STD_LOGIC_TEXTIO.ALL;

USE STD.TEXTIO.ALL;

ENTITY testbench IS

END testbench;

ARCHITECTURE testbench_arch OF testbench IS

COMPONENT stopwatch

-

FPGA入门必备:Testbench仿真文件编写实例详解2024-04-29 3985

-

【玩转多核异构】飞凌嵌入式AM6254核心板M核程序的启动、编写和仿真2023-03-31 3570

-

【玩转多核异构】M核程序的启动、编写和仿真——飞凌嵌入式2023-02-10 1292

-

FPGA仿真程序的设计方法,有什么注意事项?2021-04-29 1568

-

使用FPGA实现电子琴设计的程序与仿真资料免费下载2021-01-18 1291

-

使用FPGA实现自动售货机的VHDL程序与仿真资料2020-12-21 1267

-

FPGA仿真的学习课件和工程文件免费下载2020-12-10 1303

-

FPGA仿真有什么方法?其仿真程序该怎么设计?2019-08-30 2314

-

基于Altera FPGA的软硬件协同仿真方法介绍2019-07-04 3000

-

使用51单片机进行流水灯闪烁使用proteus仿真和keil编写程序资料说明2019-05-07 2553

-

如何使用QuartusⅡ软件来编写FPGA?2018-05-18 16704

-

基于Xilinx FPGA和VHDL的数字秒表设计与仿真实现2012-12-25 7208

-

LED控制VHDL程序与仿真2008-06-27 1683

全部0条评论

快来发表一下你的评论吧 !