半导体集成电路“晶圆测试(CP)技术”的详解;

半导体集成电路“晶圆测试(CP)技术”的详解;

描述

【博主简介】本人“爱在七夕时”,系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵。当前在各网络平台上均以此昵称为ID跟大家一起交流学习!

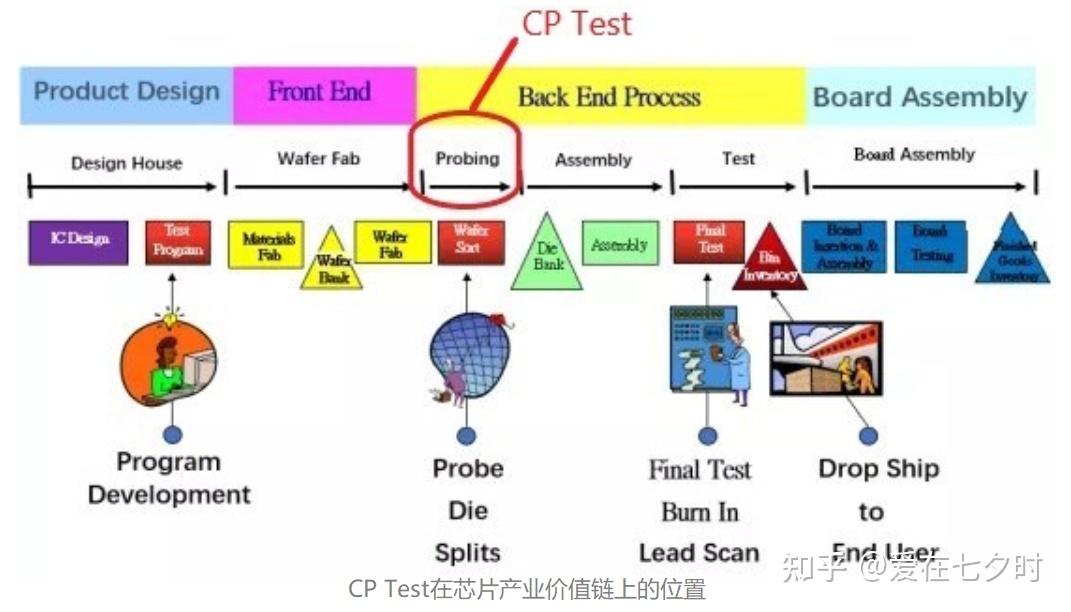

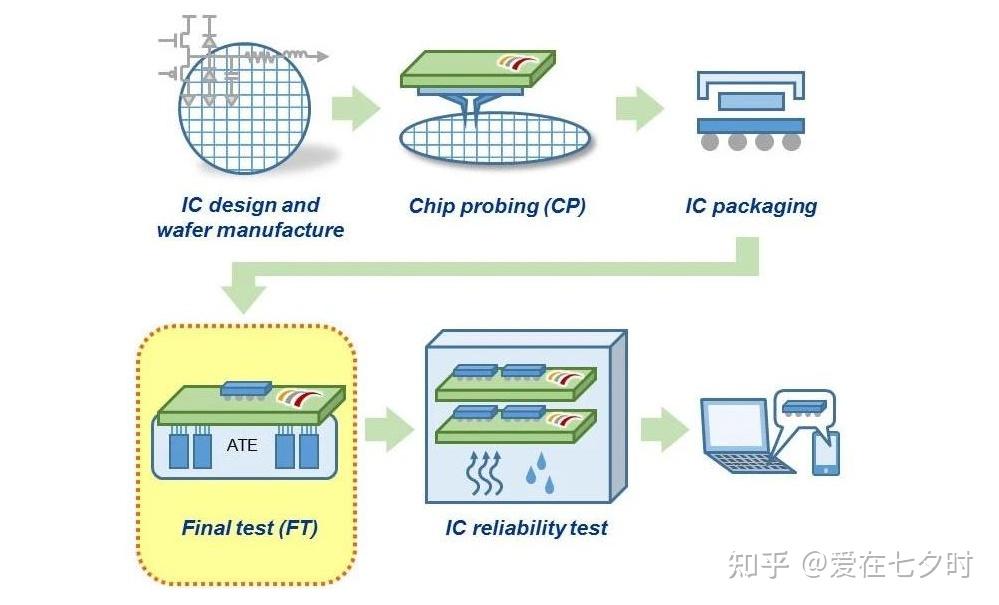

半导体行业内的朋友都知道:要实现整个集成电路的芯片测试过程,必须要采用不同的手段和方法。这其中包括扳机测试方法,晶圆测试手段,还有最后成品之后的封装测试,LT测试,各个方面的质量可靠性测试,只有每个步骤都合理安排下来,才可以让整个的芯片测试达到一个完美的效果。

而晶圆测试是在性能测试当中一个重要的步骤,要想看到芯片在使用过程中是否会出现故障,会出现哪些故障,出现故障是否可以自我修复。这就需要涉及到其中的故障芯片的问题了。晶圆测试其实就是把信号输入到相应的信号当中,对芯片做出响应和抓取,我们可以测试仪器仪表的针台,也可以制作相关的探视性的针头。那具体来说什么是“晶圆测试”、测试的主要参数有哪些、会用到哪些设备等等,这就是本章节要跟大家分享的主题。

一、晶圆测试的定义

晶圆测试,又称作:晶圆针测,英文全称:Chip Probing,简称:CP,它是对晶片上的每个晶粒进行针测,在检测头装上以金线制成细如毛发之探针(probe),与晶粒上的接点(pad)接触,测试其电气特性,不合格的晶粒会被标上记号,而后当晶片依晶粒为单位切割成独立的晶粒时,标有记号的不合格晶粒会被洮汰,不再进行下一个制程,以免徒增制造成本。

在晶圆制造完成之后,晶圆测试(CP)是一步非常重要的测试。这步测试是晶圆生产过程的成绩单。在测试过程中,每一个芯片的电性能力和电路机能都被检测到。晶圆测试也就是芯片测试(die sort)或晶圆电测(wafer sort)。

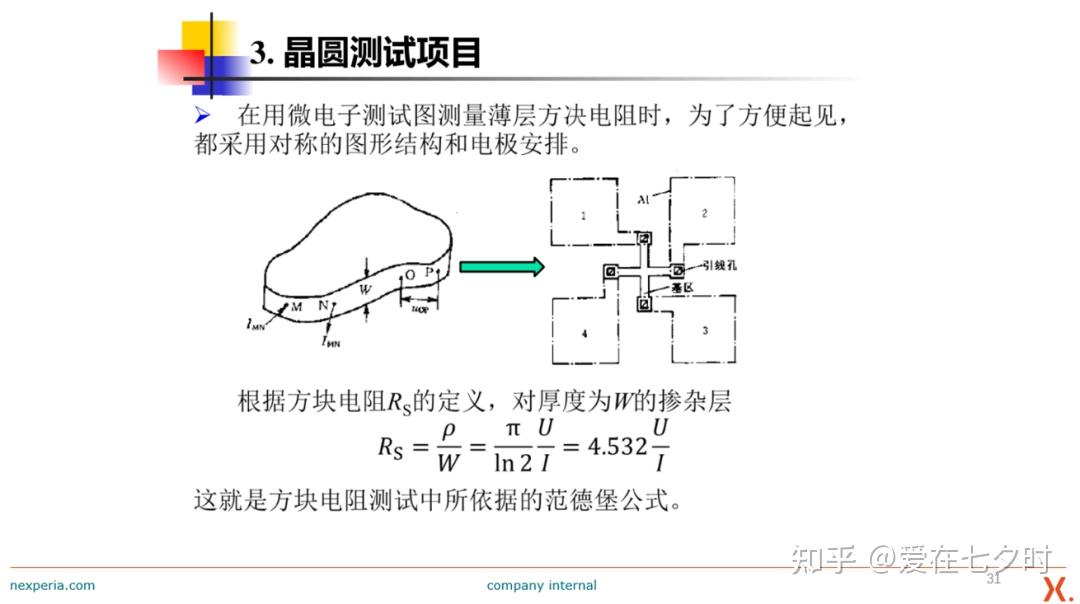

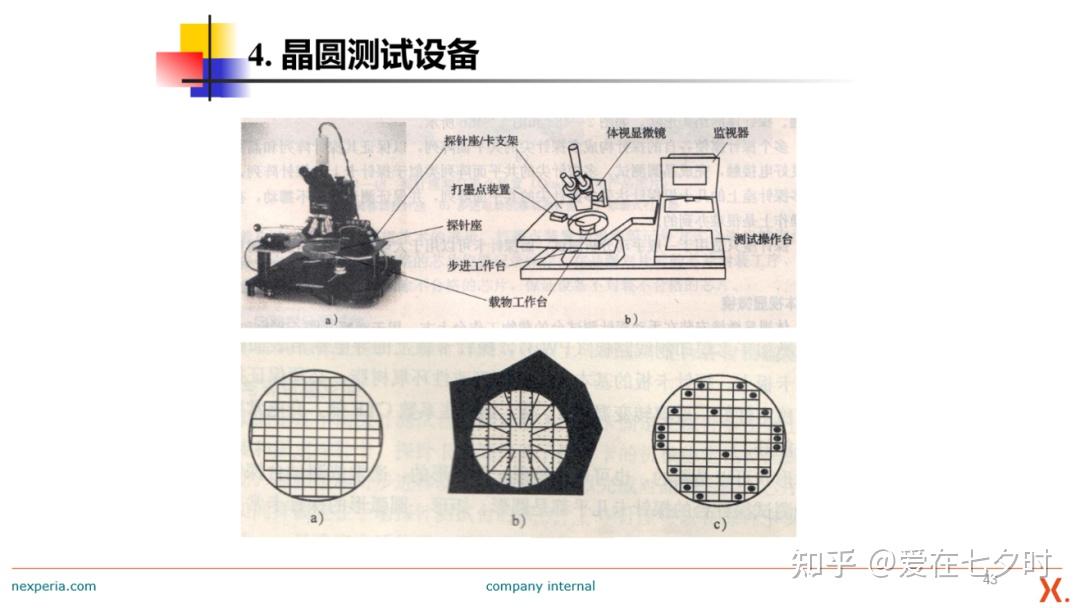

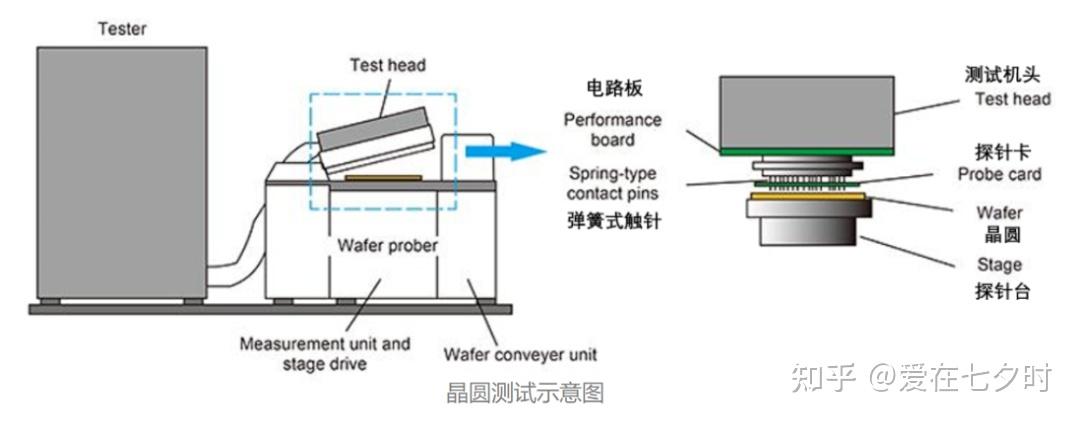

在测试时,晶圆被固定在真空吸力的卡盘上,并与很薄的探针电测器对准,同时探针与芯片的每一个焊接垫相接触(图4.18)。电测器在电源的驱动下测试电路并记录下结果。测试的数量、顺序和类型由计算机程序控制。测试机是自动化的,所以在探针电测器与第一片晶圆对准后(人工对准或使用自动视觉系统)的测试工作无须操作员的辅助。

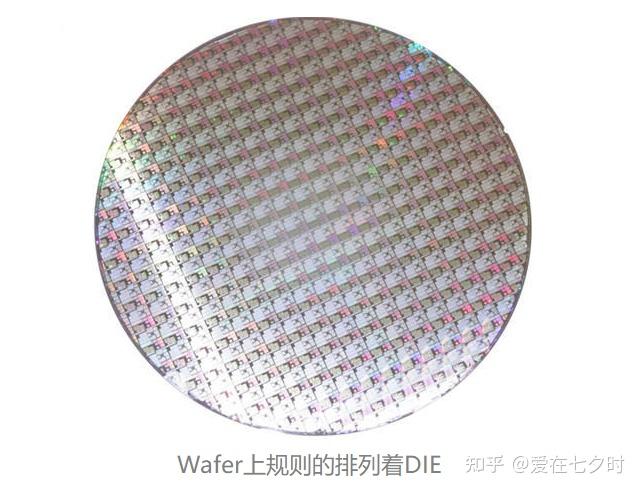

而晶圆测试(CP)的具体操作是在晶圆制作完成之后,成千上万的裸DIE(未封装的芯片)规则的分布满整个Wafer。由于尚未进行划片封装,只需要将这些裸露在外的芯片管脚,通过探针(Probe)与测试机台(Tester)连接,进行芯片测试就是晶圆测试(CP)。

二、晶圆测试(CP)的分类

晶圆测试(CP)主要分为以下几类:

1、DC测试

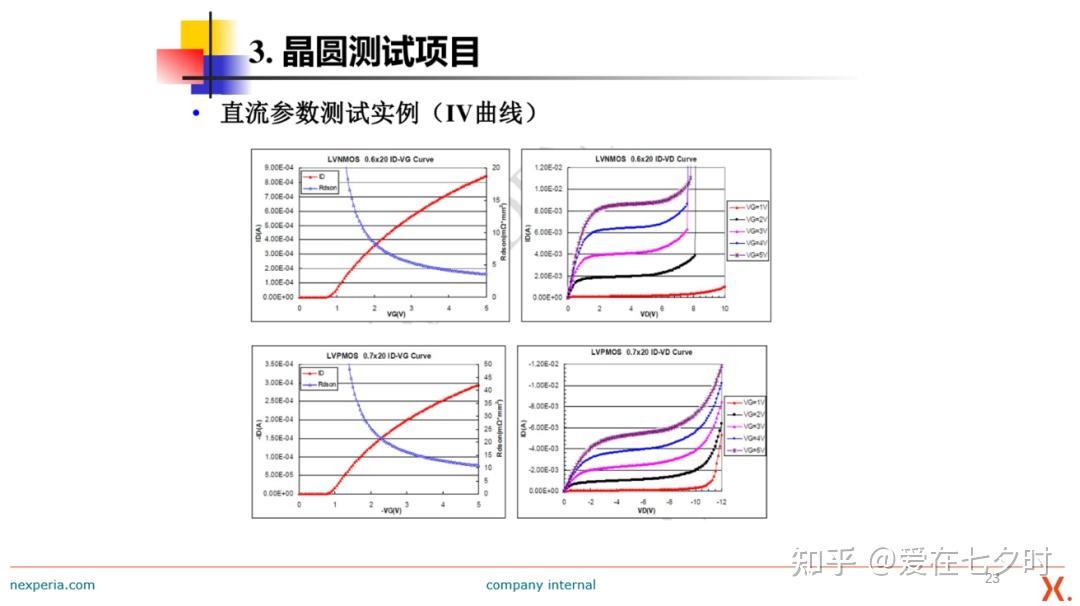

即直流测试。这种测试主要用来测试芯片的基本性能,包括开短路测试、漏电流测试、电源电流测试等,检查芯片引脚和基础电气特性是否正常。例如,检测芯片的导通电阻、源漏击穿电压等参数,确保其在规定范围内。

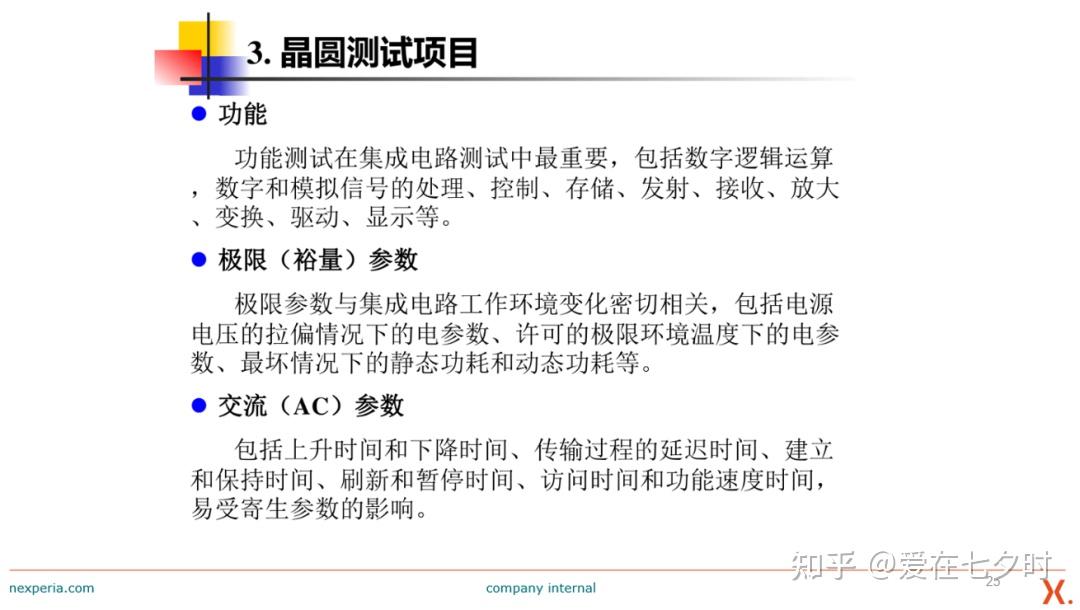

2、AC测试

即交流测试。这种测试主要用来测试芯片的高频性能,如频率响应和滤波器等。

3、功率和功能测试

功率测试主要是评估芯片的发热和功耗,而功能测试主要是通过输入测试向量(Test Pattern),验证芯片的逻辑功能是否正确。可以利用芯片内部集成的自测试电路,对存储器(RAM/ROM)等模块进行测试,提高测试效率。

4、可靠性测试

这种测试主要是测试芯片的寿命和稳定性,以确保芯片可以在预期的条件下长期运行。

5、其他参数测试

还涵盖电压、电流、时序及基本功能测试,如阈值电压(Vt)等。

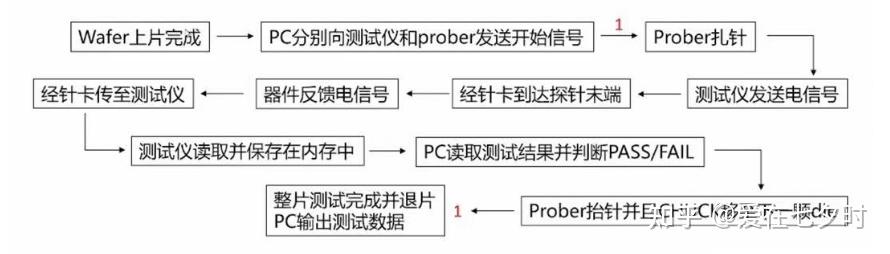

三、晶圆测试(CP)的操作流程

半导体制程中,晶圆测试(CP)制程只要换上不同的测试配件,便可与测试制程共享相同的测试机台(Tester)。所以一般测试厂为提高测试机台的使用率,除了提供最终测试的服务亦接受芯片测试的订单。

一般来说,晶圆级测试的流程包括以下几个主要步骤:

1、对准

利用光学或其他对准技术,将晶圆上的测试点与探针卡精确对齐。

2、探针卡检测

使用探针卡探测每一个裸芯片的电气接触点,进行功能性测试。

3、记录和分析

将测试数据记录并传输到后台系统,通过分析得到每个裸芯片的性能数据。

a. 晶圆测试(CP)并作产品分类(Sorting)

晶圆测试(CP)的主要目的是测试晶圆中每一颗晶粒的电气特性,线路的连接,检查其是否为不良品,若为不良品,则点上一点红墨水,作为识别之用。除此之外,另一个目的是测试产品的良率,依良率的高低来判断晶圆制造的过程是否有误。良品率高时表示晶圆制造过程一切正常,若良品率过低,表示在晶圆制造的过程中,有某些步骤出现问题,必须尽快通知工程师检查。

b. 雷射修补(Laser Repairing)

雷射修补的目的是修补那些尚可被修复的不良品(有设计备份电路在其中者),提高产品的良品率。当晶圆测试(CP)完成后,拥有备份电路的产品会与其在晶圆测试(CP)时所产生的测试结果数据一同送往雷射修补机中,这些数据包括不良品的位置,线路的配置等。雷射修补机的控制计算机可依这些数据,尝试将晶圆中的不良品修复。

4、失效芯片标记

在检测出缺陷芯片后,将其标记为不合格,以便在后续的晶圆切割和封装过程中排除。

5、加温烘烤

加温烘烤(Baking)是测试流程中的最后一项作业,加温烘烤的目的有二:

a. 将点在晶粒上的红墨水烤干。

b. 清理晶圆表面。经过加温烘烤的产品,只要有需求便可以出货。

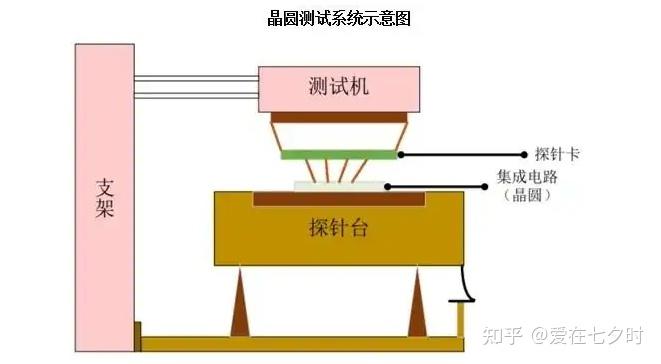

四、晶圆测试(CP)系统的组成

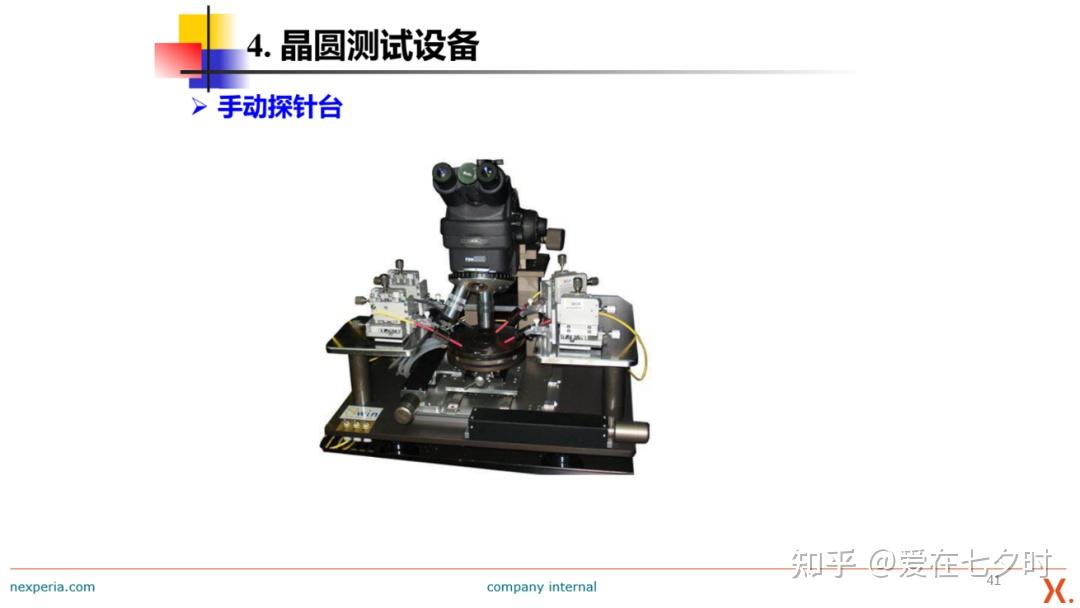

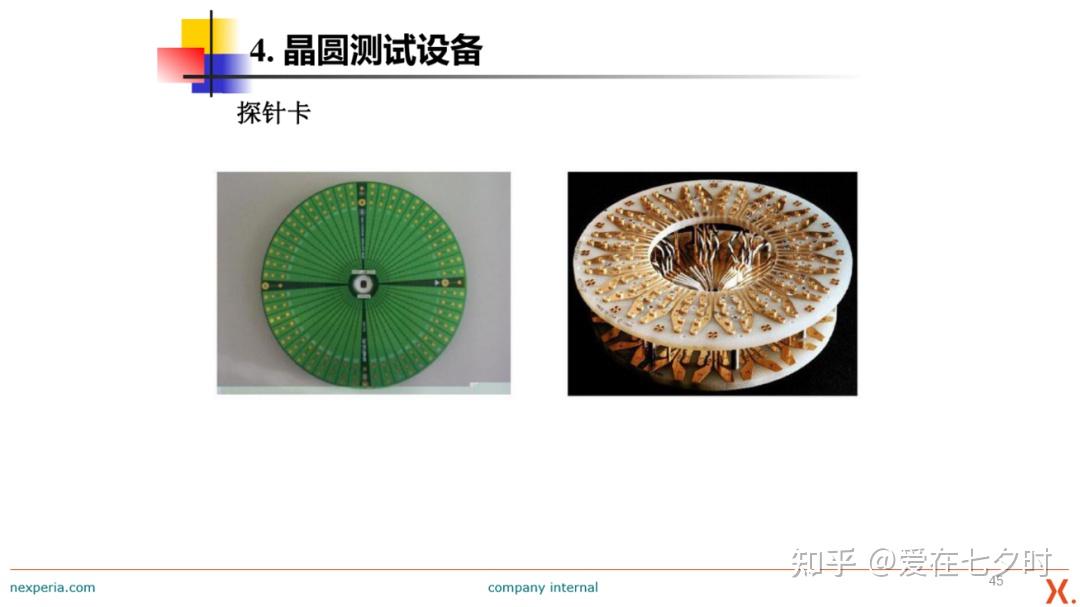

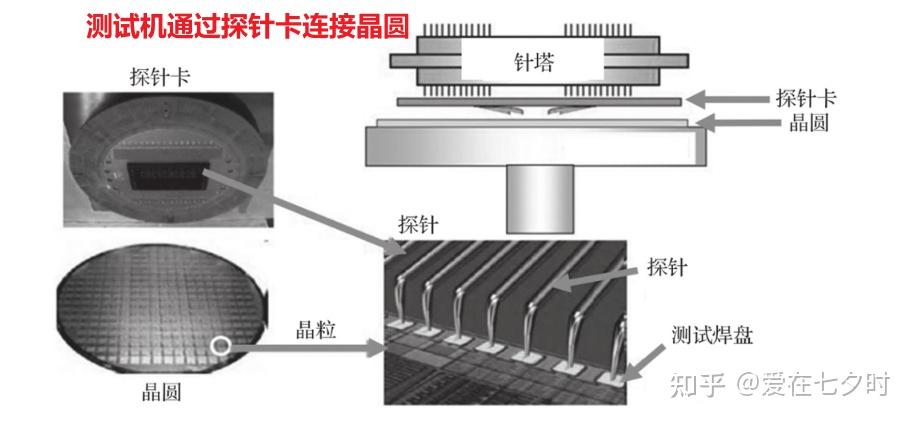

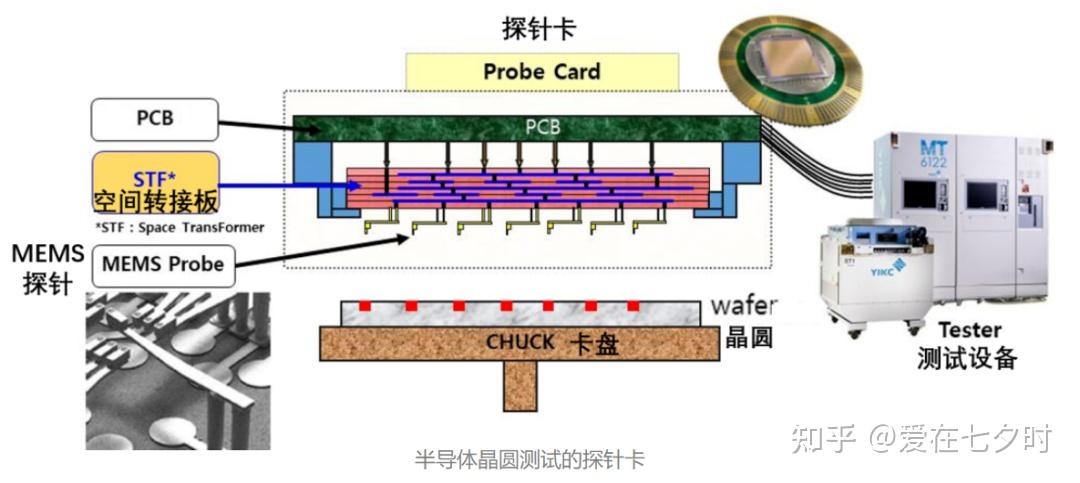

晶圆测试(CP)系统通常由支架、测试机、探针台、探针卡等组成,探针机主要由Prober(探针台)和Prober Card(探针卡)组成。探针台主要作用是承载晶圆,并不断移送UT,使得探针卡上的探针可以和芯片管脚连接,最终记录测试结果;探针卡是测试机和晶圆之间的连接介质,主要材质为铸铜或镀铜,一般具有高强度、导电性能良好及不易氧化等特性,由于DUT的独特性,所以不同批次的芯片需要对应不同型号的探针卡。示意图如下:

五、晶圆测试(CP)的基础知识分享

这一部分关于“集成电路晶圆测试(CP)基础知识”是重点要跟大家分享的内容,如有遗漏或是不足之处,还希望大家多多指正:

http://weixin.qq.com/r/QhAjO9TE64mUrZBY90VQ (二维码自动识别)

因为本培训资料章节太多,完整版如有朋友有需要,可私信我邀请您加入我“知识星球”免费下载PDF版本。注意:此资料只可供自己学习,不可传阅,平台有下载记录,切记!欢迎加入后一起交流学习。

六、晶圆测试(CP)的意义

因为通常在芯片封装阶段时,有些管脚会被封装在芯片内部,导致有些功能无法在封装后进行测试,因此晶圆中进行晶圆测试(CP)最为合适。

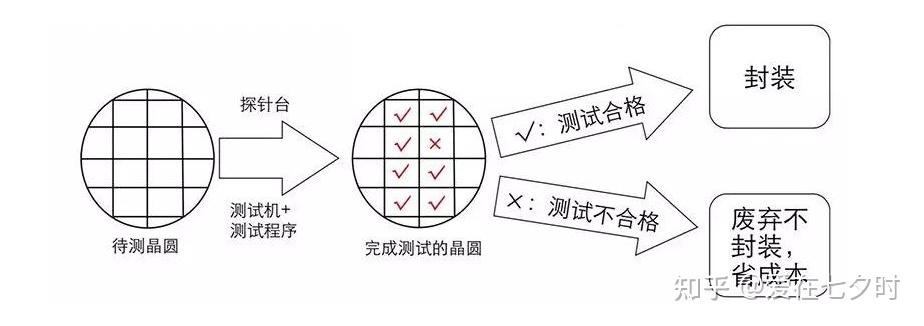

而且晶圆制作完成之后,由于工艺偏差、设备故障等原因引起的制造缺陷,分布在晶圆上的裸DIE中会有一定量的残次品。晶圆测试(CP)的目的就是在封装前将这些残次品找出来(Wafer Sort),同时还可以避免被封装后无法测试芯片性能,优化生产流程,简化步骤,同时提高出厂的良品率,缩减后续封装测试的成本。

具体来讲,晶圆测试(CP)主要是为了以下三个目标:

第一,在晶圆送到封装工厂之前,鉴别出合格的芯片。

第二,器件/电路的电性参数进行特性评估。工程师们需要监测参数的分布状态来保持工艺的质量水平。

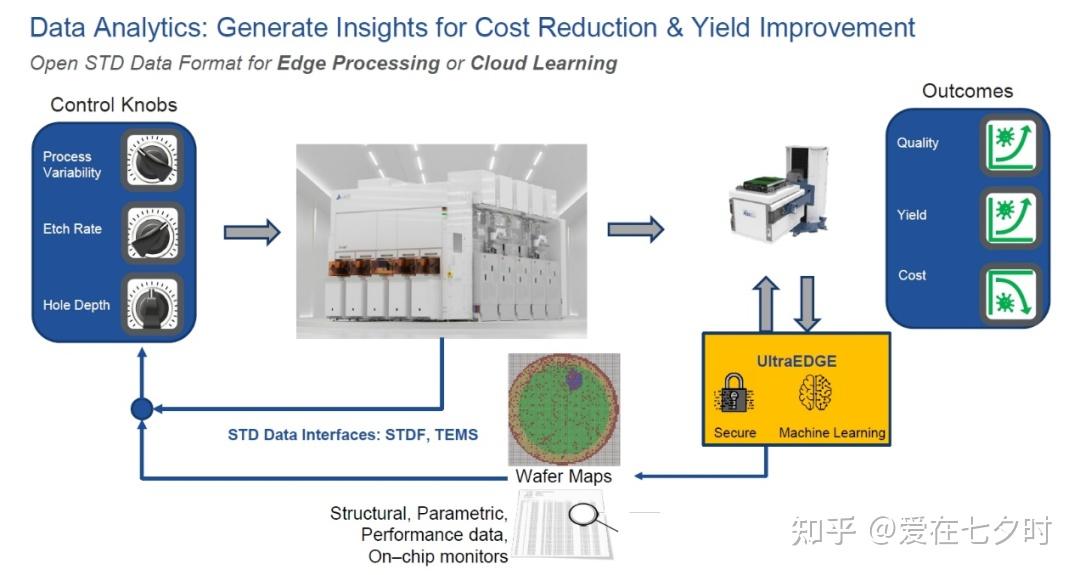

第三,芯片的合格品与不良品的核算会给晶圆生产人员提供全面业绩的反馈。合格芯片与不良品在晶圆上的位置在计算机上以晶圆图的形式记录下来。从前的旧式技术在不良品芯片上涂下一墨点。

晶圆测试(CP)是主要的芯片良品率统计方法之一。随着芯片的面积增大和密度提高使得晶圆测试的费用越来越大。这样一来,芯片需要更长的测试时间以及更加精密复杂的电源、机械装置和计算机系统来执行测试工作和监控测试结果。视觉检查系统也是随着芯片尺寸扩大而更加精密和昂贵。芯片的设计人员被要求将测试模式引入存储阵列。测试的设计人员在探索如何将测试流程更加简化而有效,例如在芯片参数评估合格后使用简化的测试程序,另外也可以隔行测试晶圆上的芯片,或者同时进行多个芯片的测试。

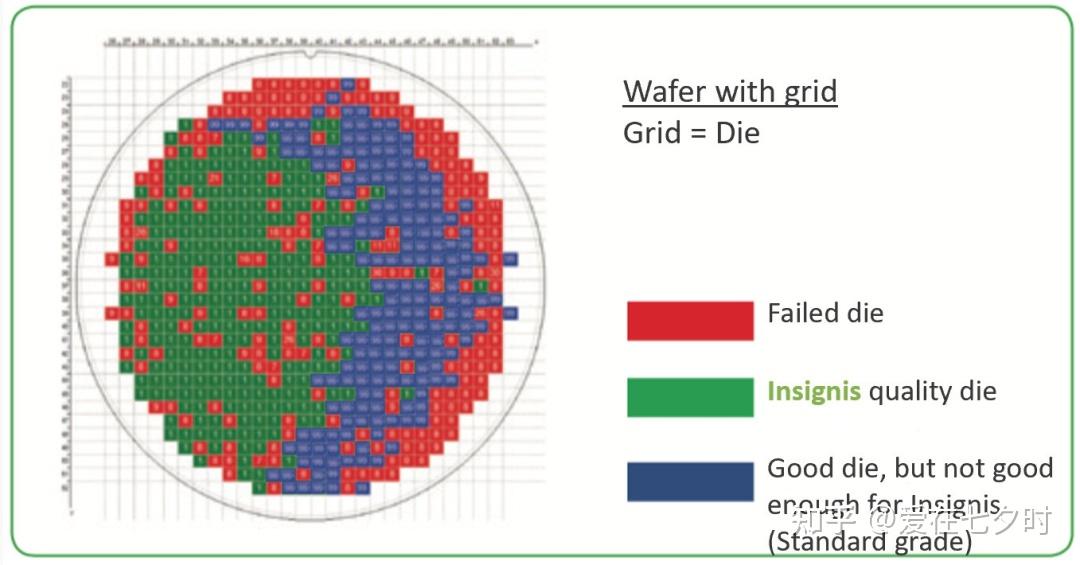

另外,也有些公司会根据晶圆测试(CP)的结果,将芯片划分等级,将这些产品投入不同的市场,购买者需要注意这一点。

七、晶圆测试(CP)的主要内容

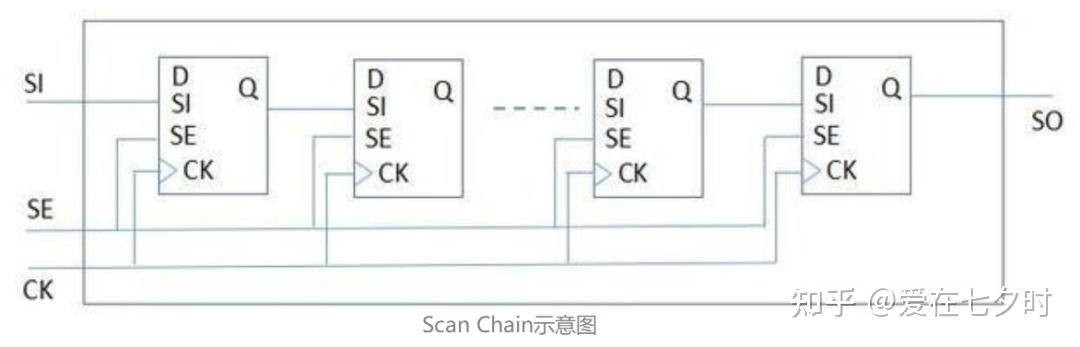

1、SCAN

SCAN用于检测芯片逻辑功能是否正确。DFT设计时,先使用DesignCompiler插入ScanChain,再利用ATPG(Automatic Test Pattern Generation)自动生成SCAN测试向量。SCAN测试时,先进入Scan Shift模式,ATE将pattern加载到寄存器上,再通过Scan Capture模式,将结果捕捉。再进入下次Shift模式时,将结果输出到ATE进行比较。

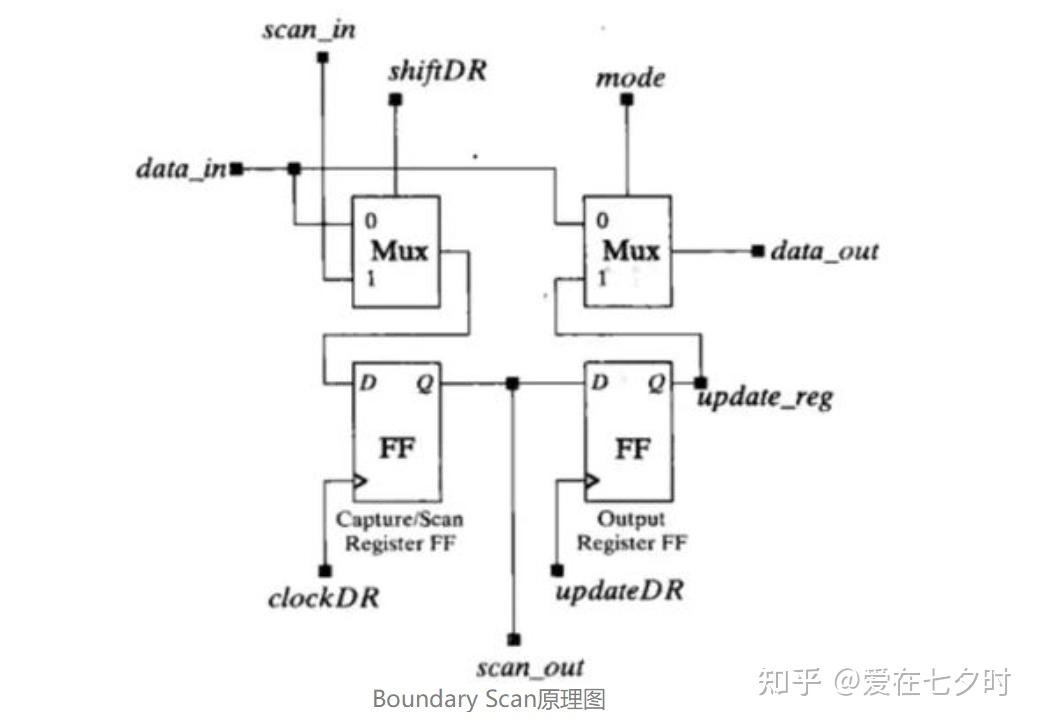

2、Boundary SCAN

Boundary SCAN用于检测芯片管脚功能是否正确。与SCAN类似,Boundary SCAN通过在IO管脚间插入边界寄存器(Boundary Register),使用JTAG接口来控制,监测管脚的输入输入出状态。

八、晶圆测试(CP)的方法

1、DC/AC Test

DC测试包括芯片Signal PIN的Open/Short测试,电源PIN的PowerShort测试,以及检测芯片直流电流和电压参数是否符合设计规格。AC测试检测芯片交流信号质量和时序参数是否符合设计规格。

2、RF Test

对于无线通信芯片,RF的功能和性能至关重要。晶圆测试(CP)中对RF测试来检测RF模块逻辑功能是否正确。

3、存储器

存储器测试数量较大,因为芯片往往集成着各种类型的存储器(例如ROM/RAM/Flash),为了测试存储器读写和存储功能,通常在设计时提前加入BIST(Built-In SelfTest)逻辑,用于存储器自测。芯片通过特殊的管脚配置进入各类BIST功能,完成自测试后BIST模块将测试结果反馈给Tester。

a. ROM(Read-Only Memory)通过读取数据进行CRC校验来检测存储内容是否正确。

b. RAM(Random-Access Memory)通过除检测读写和存储功能外,有些测试还覆盖DeepSleep的Retention功能和Margin Write/Read等等。

c. Embedded Flash除了正常读写和存储功能外,还要测试擦除功能。

d. Wafer还需要经过Baking烘烤和Stress加压来检测Flash的Retention是否正常。

e. 还有Margin Write/Read、Punch Through测试等等。

4、其他Function Test

芯片其他功能测试,用于检测芯片其他重要的功能和性能是否符合设计规格。

九、晶圆测试(CP)的技术优势

1、成本节约

通过CP测试,可以只对那些“好的”芯片进行后续的封装,避免了在坏掉的芯片上浪费封装成本,封装是芯片制造成本中非常昂贵的一环。

2、工艺反馈

CP测试会产生大量的测试数据,这些数据可以帮助芯片设计公司和制造厂分析设计缺陷和工艺问题,从而改进下一代产品设计和优化制造工艺,监控晶圆制造的工艺良率,为生产线提供实时数据反馈,提高整体良品率。

3、性能分档

对于像CPU、GPU等复杂芯片,即使在合格的芯片中,其性能(如最高工作频率、功耗)也存在差异,CP测试可以对芯片进行等级划分,以适应不同市场需求。

十、晶圆测试(CP)中需要注意的细节和技巧

在晶圆测试(CP)中应该注意哪些步骤和问题呢?在晶圆测试(CP)过程中,为了获得完美的测试结果,操作者需要了解科学的操作步骤,需要注意一些必要的问题。

1、操作人员的安全准备

在进行晶圆测试(CP)时,操作员需要戴口罩。面罩是为了确保呼气不影响检测的准确性。另外,左手要戴指尖,这也是为了保证操作的顺畅。

2、在晶圆测试(CP)前,检查设备的细节,包括夹子的方向以及夹子是否磨平。

如果打磨平整,请立即更换卡子并拧紧卡子。拧紧可以确保晶圆不会损坏。当然,在检测过程中,也要保证相应产品的检测程序齐全。

3、注意不要打破光盘

晶圆测试(CP)需要按照一定的测试程序来完成。晶圆的晶片号和型号需要准确,画面的水平距离需要调整。在试验过程中,当屈服率发生变化时,操作人员需要立即停止操作,由相应的责任工程师向组长报告。

4、酒精清洗过程可以在晶圆测试(CP)的中间进行

如果有细砂要加工,可以用细砂纸加工。测试之后,数据的准确记录自然是关键。这包括机器的型号、批号、枕卡号,以及相应的检测日期等。保存需要科学,防止任何不规范的操作行为。还有取出晶圆的问题。取出晶圆之前,需要清空真空。只有当真空完全释放时,才能取出晶圆,否则很容易压碎晶圆。那么整个行动就变得毫无意义了。

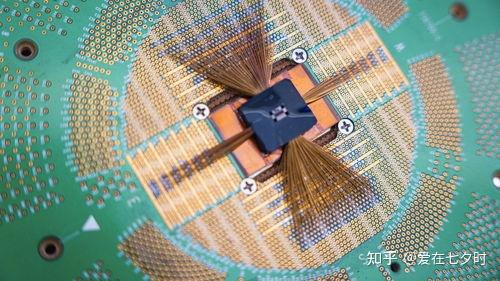

十一、晶圆测试(CP)探针卡的概述

晶圆测试(CP)的方式主要是通过测试机和探针台的联动,在测试过程中,测试机台并不能直接对待测晶圆进行量测,而是透过探针卡(Probe Card)中的探针(Probe)与晶圆上的焊垫(Pad)或凸块(Bump)接触而构成电性接触,再将经由探针所测得的测试信号送往自动测试设备(ATE)做分析与判断,因此可取得晶圆上的每颗晶粒的电性特性测试结果。

探针卡是半导体晶圆测试(CP)过程中需要使用的重要零部件,被认为是测试设备的“指尖”。由于每一种芯片的引脚排列、尺寸、间距变化、频率变化、测试电流、测试机台有所不同,针对不同的芯片都需要有定制化的探针卡,目前市场上并没有哪一种类型的探针卡可以完全满足测试需求。同时,对于一个成熟的产品来说,当产量增长时,测试需求也会增加,而对探针卡的消耗量也将成倍增长。

十二、晶圆测试(CP)技术的难点与挑战

1、探针卡的制作

在晶圆测试(CP)中,探针卡的设计和制作是一个重要的技术挑战。探针卡需要与晶圆上的每个Die精确对接,同时要保证测试的速度和精度。如果探针卡设计不当,会导致测试的干扰问题,甚至会损坏晶圆上的Die。

2、并行测试的干扰

在进行晶圆测试(CP)时,往往会采用并行测试技术,即一次测试多个Die。这种并行测试虽然可以提高测试效率,但容易引起信号干扰,影响测试结果的准确性。

3、大电流测试的限制

由于探针的电流限制,晶圆测试(CP)无法进行大电流测试(例如功率MOSFET的测试)。这部分只能留到FT测试中进行。

十三、总结一下

晶圆测试(CP)的核心任务是剔除不合格的Die,减少后续封装和最终测试(FT)的成本,同时监控晶圆制造工艺的良率。而最终测试(FT)则主要是对封装后的芯片进行功能和可靠性测试,确保最终产品能够在不同环境下正常工作。

简单来讲:我们可以将晶圆测试(CP)比作初步筛选水果,而最终测试(FT)则是对包装后的水果盒进行检测。两者在测试目标、测试项目和测试设备上都有很大的不同。

虽然有些公司选择跳过晶圆测试(CP)以节省成本,但这并不适用于所有产品。对于高成本和高可靠性的产品,晶圆测试(CP)仍然是不可或缺的一步。最终,晶圆测试(CP)和最终测试(FT)共同确保了集成电路产品的质量和性能,二者缺一不可。

另外、晶圆测试(CP)与最终测试(FT)还是第三代半导体量产化的关键保障,两者的协同优化可显著提升碳化硅(SiC)/氮化镓(GaN)芯片的良率与可靠性。未来,随着8英寸和12英寸碳化硅(SiC)晶圆的普及与测试设备智能化,第三代半导体的应用边界将进一步扩展。

http://weixin.qq.com/r/QhAjO9TE64mUrZBY90VQ (二维码自动识别)

免责声明

【我们尊重原创,也注重分享。文中的文字、图片版权归原作者所有,转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时私信联系,我们将第一时间跟踪核实并作处理,谢谢!】

审核编辑 黄宇

-

仿真技术在半导体和集成电路生产流程优化中的应用2009-08-20 3217

-

集成电路晶圆测试基础教程ppt2011-12-02 73930

-

射频集成电路半导体和CAD技术讨论2019-07-05 2574

-

芯片,集成电路,半导体含义2020-02-18 6496

-

半导体集成电路是什么2020-03-24 2733

-

芯片,半导体,集成电路,傻傻分不清楚?2020-04-22 7998

-

《炬丰科技-半导体工艺》超大规模集成电路制造技术简介2021-07-09 3776

-

什么是半导体晶圆?2021-07-23 4291

-

集成电路与半导体2021-09-15 3020

-

半导体集成电路教程2011-11-09 1425

-

晶圆测试探针台的组成以及晶圆测试的重要性和要求2021-10-14 10630

-

半导体集成电路和晶圆有何关系?半导体晶圆制造工艺介绍2023-01-11 6766

-

半导体集成电路封装流程|划片工艺详解2023-02-02 6081

-

半导体晶圆制造流程介绍2025-04-15 3839

-

半导体行业知识专题九:半导体测试设备深度报告2026-01-23 2375

全部0条评论

快来发表一下你的评论吧 !