RISC-V异常中断机制全解析

RISC-V异常中断机制全解析

电子说

描述

RISC-V 作为开源、模块化的精简指令集架构,其异常中断机制是保障系统可靠运行、响应外部事件与处理内部错误的核心支撑。不同于 x86、ARM 等闭源架构的复杂设计,RISC-V 异常中断机制遵循“精简、灵活、可扩展”的设计理念,通过模块化特权级、标准化控制寄存器与可配置的处理流程,适配从嵌入式微控制器到高性能服务器的全场景需求。本文将从核心概念、分类体系、处理流程、关键寄存器及实际应用等维度,对 RISC-V 异常中断机制进行全面解析。

一、核心概念:异常与中断的定义及本质区别

在 RISC-V 架构中,“异常(Exception)”与“中断(Interrupt)”均属于“异常事件”的范畴,本质是打破处理器正常指令执行流的特殊事件,但二者的触发源、触发时机与处理目标存在明确差异,这是理解 RISC-V 异常中断机制的基础。

1.1 异常(Exception)

异常是由处理器内部执行过程触发的事件,通常与当前执行的指令直接相关,属于“同步事件”(与指令执行时钟同步)。其核心特征是“执行错误或特殊需求”,需要处理器暂停当前任务,转入异常处理程序修正错误或完成特殊操作后,再返回原执行流(或终止执行)。

常见异常类型包括:非法指令异常(执行未定义指令)、访存错误异常(访问未授权内存、对齐错误)、断点异常(执行 EBREAK 指令,用于调试)、系统调用异常(执行 ECALL 指令,用户态向特权态切换)、页故障异常(虚拟内存地址未映射)等。

二、RISC-V 异常中断的分类体系

RISC-V 对异常中断的分类采用“原因码(Cause Code)”标准化定义,通过核心控制寄存器 mcause(机器模式原因寄存器)、scause(监督模式原因寄存器)等存储事件类型,不同特权级对应独立的原因码空间。分类体系可从“特权级维度”和“事件类型维度”双重划分。

2.1 特权级维度分类

RISC-V 支持 4 种特权级(从高到低:M 模式、S 模式、H 模式、U 模式),其中 H 模式(Hypervisor 虚拟化模式)为扩展特权级,嵌入式场景常用 M 模式(机器模式)和 S 模式(监督模式)。异常中断的处理特权级由事件类型和系统配置决定:

- M 模式专属事件 :涉及处理器核心硬件的关键事件,如复位异常、硬件错误异常、M 模式定时器中断等,只能在 M 模式下处理(最高特权级,不可剥夺)。

- S 模式专属事件 :涉及操作系统层面的事件,如虚拟内存页故障、S 模式系统调用、外设中断(由 M 模式委托给 S 模式)等,由操作系统内核处理。

- U 模式触发事件 :用户态程序触发的事件(如 U 模式系统调用、非法指令),需陷入更高特权级(S 或 M 模式)处理。

核心规则:低特权级事件可通过“委托机制”(Delegation)交由高特权级处理,高特权级事件不可委托给低特权级。

2.2 事件类型维度分类(标准原因码)

RISC-V 标准定义了 32 位原因码(部分位为扩展预留),其中最高位(第 31 位)用于区分“中断”与“异常”: 最高位为 1 表示中断,为 0 表示异常 ;低 31 位为具体事件的原因码编号。以下是常用标准原因码:

| 原因码(低31位) | 事件类型(最高位=0:异常;=1:中断) | 说明 |

|---|---|---|

| 0 | 异常:指令地址对齐错误 | 访问指令地址非指令长度对齐(如32位指令地址未对齐 4 字节) |

| 2 | 异常:非法指令 | 执行未定义的RISC-V指令 |

| 3 | 异常:断点 | 执行EBREAK调试指令触发 |

| 8 | 异常:环境调用(ECALL)- U 模式 | 用户态程序执行ECALL触发系统调用 |

| 9 | 异常:环境调用(ECALL)- S 模式 | 监督态程序执行ECALL触发更高特权级调用 |

| 11 | 异常:环境调用(ECALL)- M 模式 | 机器态程序执行ECALL触发(通常保留) |

| 12 | 异常:页故障(指令访问) | 虚拟指令地址未映射或权限不足 |

| 13 | 异常:页故障(数据写访问) | 虚拟数据地址写访问未映射或权限不足 |

| 14 | 异常:页故障(数据读访问) | 虚拟数据地址读访问未映射或权限不足 |

| 16 | 中断:外部中断(M模式) | 外部设备触发的机器态中断 |

| 17 | 中断:软件中断(M模式) | 软件触发的机器态中断(如多核心通信) |

| 18 | 中断:定时器中断(M模式) | 机器态定时器(mtime)溢出触发 |

| 20 | 中断:外部中断(S模式) | 外部设备触发的监督态中断(由M模式委托) |

三、RISC-V 异常中断的核心处理流程

RISC-V 异常中断处理流程遵循“标准化、可配置”的设计思路,核心流程分为 5 个阶段: 事件触发与识别 → 上下文保存 → 异常入口跳转 → 事件处理 → 上下文恢复与返回 。不同特权级的处理流程基本一致,差异主要体现在控制寄存器的使用和权限检查上。以下以最常用的 M 模式(机器模式)为例,详细拆解处理流程。

3.1 阶段 1:事件触发与识别

当异常(如非法指令)或中断(如定时器溢出)发生时,处理器首先完成当前指令的执行(异常为同步触发,中断为异步触发,需等待当前指令执行完毕),随后进行事件识别:

- 处理器自动检测事件类型,将“中断/异常标识”(最高位)和“原因码”写入mcause 寄存器;

- 记录当前指令的下一条指令地址(异常时为出错指令地址,中断时为当前执行完毕指令的下一条地址)到 mepc(机器模式异常程序计数器)寄存器,用于后续返回;

- 检查事件对应的特权级和使能状态:通过 mie(机器模式中断使能寄存器)检查中断是否被使能,通过 mstatus(机器模式状态寄存器)的 MIE 位(全局中断使能)检查全局中断开关,若未使能则忽略该事件。

3.2 阶段 2:上下文保存

为了在事件处理完成后能够恢复原任务的执行状态,处理器需要保存当前的“上下文”(即处理器核心寄存器状态)。RISC-V 架构 未规定硬件自动保存上下文 ,而是将上下文保存交由软件实现(灵活性更高,适配不同场景的资源需求):

- 保存的核心上下文包括:通用寄存器(x0~x31,x0 恒为 0 可省略)、程序计数器(PC,已由硬件保存到 mepc)、状态寄存器(mstatus)等;

- 保存位置:通常为当前特权级的栈空间(如 M 模式栈),或专用的上下文保存缓冲区(嵌入式场景常用,减少栈操作开销);

- 注意事项:上下文保存需保证“原子性”,避免在保存过程中被更高优先级事件打断(可通过关闭全局中断实现,即清除 mstatus.MIE 位)。

3.3 阶段 3:异常入口跳转

上下文保存完成后,处理器需要跳转到对应的异常处理程序入口。RISC-V 通过 mtvec(机器模式异常向量表基地址寄存器)配置入口地址和跳转模式,支持两种跳转模式:

- 直接模式(Direct Mode) :mtvec 寄存器低 2 位为 00,所有异常中断都跳转到 mtvec 高 30 位指定的基地址。该模式适用于简单系统(如嵌入式微控制器),处理流程统一,实现简单,但灵活性低;

- 向量模式(Vectored Mode) :mtvec 寄存器低 2 位为 01,不同类型的异常中断跳转到不同的入口地址。入口地址计算规则为:mtvec 基地址 + 4 × 原因码。该模式适用于复杂系统(如操作系统),可针对不同事件快速跳转到专用处理函数,提升处理效率。

跳转完成后,处理器自动将当前特权级切换到 M 模式(若当前为低特权级),并关闭全局中断(mstatus.MIE 清 0),避免处理过程中被打断。

3.4 阶段 4:事件处理(核心业务逻辑)

跳转至异常处理程序后,软件根据 mcause 寄存器的原因码,执行对应的处理逻辑。不同事件的处理逻辑差异较大,典型场景如下:

- 非法指令异常 :打印错误日志,终止当前任务或复位系统;

- 系统调用异常 :根据系统调用号(通常存储在 a7 寄存器),执行对应的内核服务(如文件读写、进程调度);

- 定时器中断 :更新系统时钟,触发任务调度(RTOS 核心逻辑);

- 外设中断 :读取外设状态寄存器,处理数据(如 UART 接收数据存入缓冲区),清除中断标志位。

处理过程中需注意:若存在中断嵌套需求,可在处理低优先级事件时,重新开启全局中断(设置 mstatus.MIE 为 1),允许更高优先级中断打断当前处理。

3.5 阶段 5:上下文恢复与返回

事件处理完成后,需要恢复之前保存的上下文,并返回原任务继续执行:

- 从栈或缓冲区中恢复通用寄存器、mstatus 等上下文信息;

- 执行 mret 指令(机器模式返回指令):处理器自动将mepc 寄存器中的地址加载到 PC,跳回原任务的下一条指令;同时恢复之前的全局中断使能状态(mstatus.MPIE 位的值传递给 mstatus.MIE)。

至此,整个异常中断处理流程完成,处理器恢复原任务的正常执行流。

四、关键控制寄存器解析

RISC-V 异常中断机制的核心是一系列特权级控制寄存器,用于配置使能、记录事件信息、存储上下文地址等。以下是 M 模式和 S 模式下最关键的寄存器,以及其核心功能:

4.1 状态寄存器:mstatus / sstatus

用于记录和控制处理器的特权级状态、中断使能状态等,核心位定义如下(以 mstatus 为例):

- MIE(位 3):机器模式全局中断使能位,1=使能,0=禁用;

- MPIE(位 7):机器模式中断使能保存位,用于在异常发生时保存 MIE 的值,恢复时通过 mret 指令恢复;

- MPP(位 11~12):机器模式之前特权级,记录异常发生前的特权级(00=U 模式,01=S 模式,11=M 模式),用于返回时恢复特权级;

- SIE(位 1)、SPIE(位 5)、SPP(位 8~9):对应 S 模式的中断使能位、保存位、之前特权级,功能与 M 模式类似。

4.2异常入口寄存器:mtvec / stvec

用于配置异常中断的入口地址和跳转模式,格式为:

- 低 2 位:跳转模式(00=直接模式,01=向量模式,10/11=预留);

- 高 30 位:异常向量表基地址。

4.3 原因与程序计数器寄存器:mcause / scause、mepc / sepc

- mcause / scause:存储异常中断的原因码,最高位区分中断(1)与异常(0),低 31 位为具体原因码;

- mepc / sepc:存储异常中断发生时的下一条指令地址,用于返回原执行流。

4.4 读取方式:

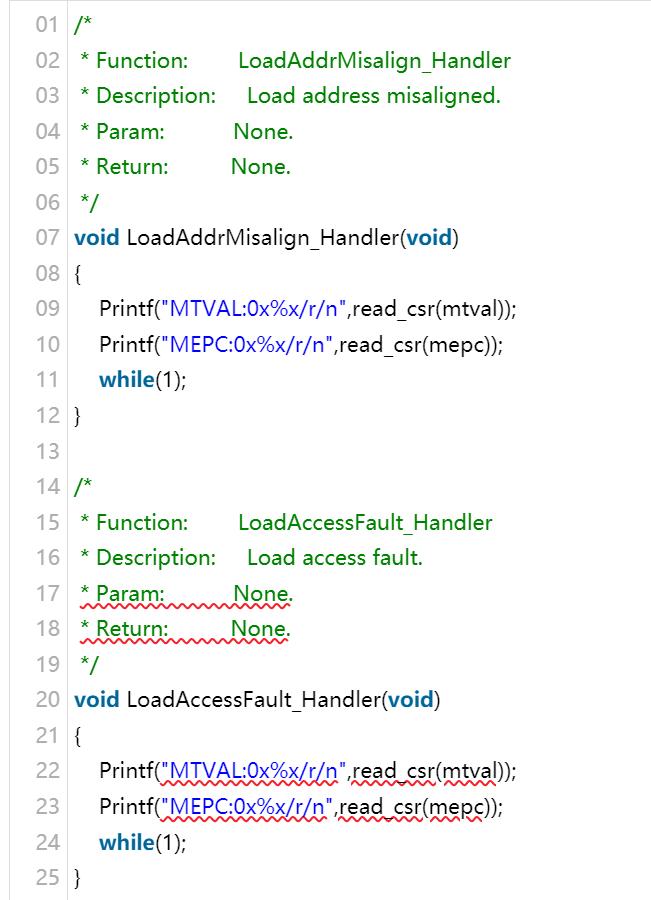

例:

五、实际应用场景与注意事项

**5.1 **程序中全局数组地址为奇数地址,未四字节对齐

打印内容:

"MTVAL:0xeeeeeeee/r/n MEPC :0xeeeeeeee/r/n"

修改方式:

typedef** attribute ((aligned(4))) uint16_t AlignedUint16_IAR;**

void****MapADCTempResultsToArray( AlignedUint16_IAR Set_74HC4067_Channel[TEMP_SENSOR_COUNT])

**5.2 **内存访问异常场景

// 数组越界触发硬件异常的测试函数

voidtest_array_out_of_bounds(void) {

int****arr[3] = {1, 2, 3};

// 合法访问:索引2

printf("合法访问arr[2]:%dn", arr[2]);

// 越界访问:

int****arr[3] = val; // 读越界,触发加载访问故障

(void)val;

}

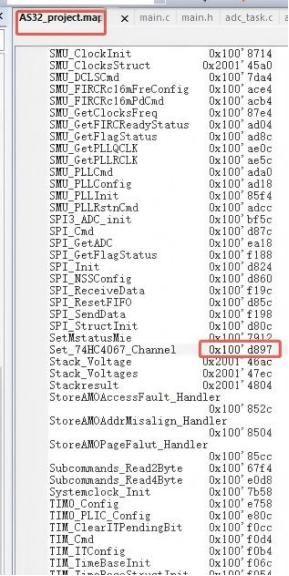

打印内容

"MTVAL:0x10084dc/r/n MEPC :0x100f46/r/n"

MTVAL显示 “LoadAccessFault_Handler”对应的地址;MEPC: 0x100f46 显示出错的非对齐地址

六、总结

RISC-V 异常中断机制以“精简、灵活、可扩展”为核心设计理念,通过标准化的原因码、可配置的处理流程和特权级隔离,实现了对各类异常和中断事件的高效管理。其核心优势在于:模块化的特权级设计适配全场景需求,软件可控的上下文保存提升灵活性,标准化的控制寄存器降低开发复杂度。

理解 RISC-V 异常中断机制的关键在于厘清“异常与中断的本质区别”、掌握“标准化处理流程”和“核心控制寄存器的功能”,并结合具体应用场景(嵌入式/操作系统)优化配置。随着 RISC-V 架构的不断普及,深入掌握其异常中断机制将成为嵌入式开发、处理器架构设计等领域的核心能力。

-

RISC-V指令异常调试实例2023-06-08 3803

-

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析2025-11-08 8037

-

ARM异常中断处理流程分析2020-08-28 3153

-

有没有深度解析RISC-V的文章2023-03-22 994

-

RISC-V的异常处理机制复杂吗?2023-04-21 993

-

ARM体系中的异常中断及其应用2017-09-22 634

-

ARM微处理器编程模型之异常中断处理分析2017-10-18 1159

-

Thumb指令集之异常中断产生指令解析2017-10-19 1651

-

ARM S3C4510B系统的异常中断机制解析2018-02-03 2272

-

ARM中异常中断问题详情分析总结2018-04-05 1736

-

ARM异常中断的原因及处理措施2020-06-17 9449

-

当ARM异常中断发生时的处理措施2020-08-27 3376

-

RISC-V CPU调试机制的设计原理2022-10-18 3216

-

ARM微处理器对异常中断的响应过程2023-10-18 1753

-

ARM中的异常中断是如何实现进入中断程序的?如何进入呢?2023-10-19 1966

全部0条评论

快来发表一下你的评论吧 !