3G-SDI串行数字接口的特征性能及应用实例分析

描述

SDI接口是数字串行接口(serial digital interface)的首字母缩写。 串行接口是把数据字的各个比特以及相应的数据通过单一通道顺序传送的接口。由于串行数字信号的数据率很高,在传送前必须经过处理。早在上世纪80年代,随着科学技术的不断发展,SDI得到了快速发展并对其标准作出了定义。SDI是串行数字接口,被用来传送无压缩的数字视频信号。3G-SDI中的3G是指SDI信号的数据传输率为3Gbit每秒。由于HDTV可以支持每秒30帧的逐行扫描1920×1080的分辨率格式,而3G能够支持比HD视频信号最高帧扫描频率高一倍的频率,即3G可以支持每秒60帧的HD信号,这在观看动态视频时的差别是很大的。

SMPTE424M定义了3G-SDI的物理层及这类电信号的特征性能。传送的信号应该有800mV的电压摆幅,上升和下降时间必须小于135ps,允许有一些过冲的存在,但不可以超过10%,即80mV。在SMPTERP184中规定了时钟抖动和调整抖动的定义,它们需要的抖动参数分别小于2UI和0.2UI,调整抖动参数实际上要求是0.3UI,但是SMPTE强烈推荐使用0.2UI的参数要求,因此本文将使用0.2UI的参数要求。接收器中,在10Hz到297MHz的频带内,输入抖动容限,从2UI到0.2UI。发送器的输出与接收器的输入都应该被优化以保证回波损耗。

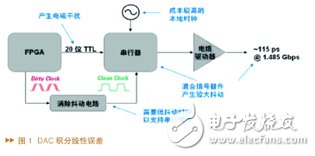

在发送器中,大部分抖动来自于串行器,电缆驱动器也会增加一些抖动。图1所示为目前正在使用的发送器的典型框图,它可以工作到HD、SDI,但是它不支持3G-SDI。由于20位的数字视频总线已经在HD中制造了EMI问题,而在3G中该时钟频率加倍,因此EMI问题在3G中将更加严重。此外,PCB的布线也不是一项简单的工作,工程师将要面对在148.5MHz工作下的20条印制线。FPGA产生的时钟信号也包含很多抖动,因此这些时钟是不适合直接用于串行器的,由于会增加串行器的输出抖动,从而需要加入抖动消除电路或Genlock电路以消除抖动。此外,有一些串行器也要求一个干净的本地时钟,这些抖动和本地时钟不仅增加了系统成本,也占用了 PCB的面积。最后,串行器是一个模拟信号器件,包含了数字处理单元以及模拟串行单元,因此产生低抖动的模拟数字信号很困难。以HD信号为例,最小可以实现的输出抖动大约为115ps或0.17UI,因此如果要支持3G,必须要采用全新的结构。

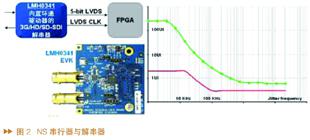

NS的SDI串行器和解串器产品创新的结构为SDI-3G提供了低辐射、低成本、低抖动和高性能的解决方案,在FPGA和串行器或解串器之间采用了LVDS技术,从而去除了TTL连接。由于LVDS具有非常低的EMI辐射和功率损耗,因此非常适合应用在手持产品中。另外,PCB的印刷线也从20根减少到10根,使得PCB的设计更加容易。由于芯片内部设计了高性能PLL锁相环,不再需要外置本地时钟及抖动消除电路,因此系统成本得到了明显的降低,同时节约了电路板的面积。因为FPGA已经存在于系统中,不需要额外的费用,因此大部分数字信号处理工作可以由FPGA完成,如CRC及行号插入、光栅、ANC和EDH插入等。事实上,由于最困难的串行工作现在已经由串行器来完成了,因此可以降低FPGA的等级。这种串行由于采用了优秀的模拟技术工艺和高精度的锁相环,因此可以提高解串器的抖动容限,最低可以达到0.6UI。和串行器类似,我们在解串器中也可以集成类似的环路,它可以简化设计和减小空间,所以这样的解串器不需要本地的时钟,它是一个微小空间的7×7毫米的LLP封装,如图2所示。

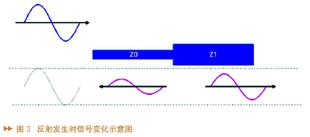

当信号从一种介质传送到另外一种新的介质时,一部分信号将会被反射,剩余的信号将穿过这个介质。声光和电磁波都有类似的特性,这是因为当介质改变时介质的密度和特性会发生变化。在传输线的原理中,印制电路线的宽度和其特性阻抗成正比,所以信号在两个不同阻抗的印制电路线间传输时反射就会发生,反射的发生会减小信号的能量,影响接收器的处理,同时信噪比也会减小。另外当信号朝着源的方向被反射回来时,它会和原始的信号相混合叠加,降低信号的完整性,如图3所示。

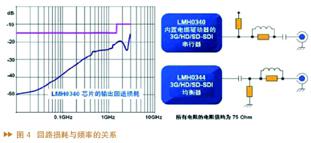

回送损耗可以用来衡量两种阻抗匹配的优劣。通常的BNC连接器、电路板走线、电缆驱动器,输出阻抗或均衡器的阻抗都各不相同,所以在实际的应用中需要考虑SMPTE严格的回送损耗指标要求。回路损耗是和频率相关的参数,当频率升高时,寄生电容和电感变得更加的明显,它会使回路损耗变差。

NS的SDI系列产品都有很好的输入输出回路损耗特性,只需要使用一个简单的小网络就可以实现和BNC连接器的匹配。最普通的网络可以通过将一个小小的电感和一个 75Ω的电阻并联来实现,这个匹配网络在直流特性时应该看起来象一个短路线,允许由终端电阻来提供传输线阻抗;在很高的工作频率条件下寄生电容的阻抗值将会占主要的部分,这时回路损耗补偿网络可以提供75Ω的阻抗作为终端电阻,如图4。

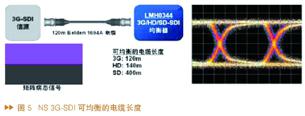

即使你的系统可以满足前面所述的指标要求,但也不能确定系统是稳定可靠的。与模拟系统不同的是,数字系统性能不会缓缓下降,而是无误差地工作直到系统彻底损坏。通常采用音律测试方法对系统的稳定性进行评价,即改变数字信号一个或多个参数直到使该数字系统失效,最直接的音律测试方法是加入电缆进行音律测试。在电缆传输中,由于电缆的频率响应特性,信号会产生损失和相移等失真,均衡器可以为失真信号提供补偿,我们可以通过加入更长的电缆对接收端的均衡范围、噪声性能等特性作出评价。这种音律测试特别在使用SDI的病态信号时是非常有意义的,因为它基本上模拟了真实的状况。串行数字系统对病态信号的处理是很困难的,在这种低频的极差图形中,其中一区用于测试均衡器,另一区可以用来检查接收器的锁相环的性能。NS的3G-SDI均衡器有能力在3G时均衡120米电缆长度的距离,从图5可以看出使用NS的3G-SDI产品,是很容易满足SMPTE的指标的。

SDI信号经过长距离传输时信号质量会变差,为了补偿长距离传输的损耗并重建视频信号的幅度,需要加入一个额外的电缆均衡器。然而均衡器无法去除信号中固有的抖动与噪声,因此为了不使整个信号链路的抖动被堆积,不建议采用均衡器输出做多点传输,推荐在分传前利用时钟恢复器重新产生干净的信号,需要注意的是时钟恢复器需要均衡器在再次产生数据之前重建信号的幅度并打开眼图。有时候信号在系统间传输时,传输的介质可能是背板而不是电缆,这种情况下使用另外的电缆均衡器也可以补偿信号的损失,但是无法达到成本最优化。由于背板不会太长,因此无源均衡器是更为理想的方案,它具有很低的价格且不消耗功率。

时钟恢复器及电缆驱动器均广泛应用于路由器中,以大型路由器为例,两者的功耗可占总功耗的40%左右。有时候在应用时并不是每个输出通道都是激活的,如果能够关断这些空闲或未使用的通道,则可以有效地减少功耗。NS的LMH0303电缆驱动器具有输入信号丢失告警和输出电缆检测功能,使系统设计更加容易。当输入信号丢失时,LOS(Loss of Signal)将输出一个信号通知系统,由其决定是否关断这个设备的通道。同样,通过输出的告警信号可以了解输出电缆是否没有连接或不可靠。这类电缆驱动器和时钟恢复器都能处于深功率节省方式,分别能节约3mW和10mW的功耗。

应用实例

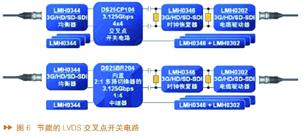

交叉点开关是一个标准的模块,它经常在开关电路和复用器中使用,例如在汽车娱乐和导航系统中,多个不同的视频信号输入源和多个不同的显示设备,需要在任意的显示设备上显示任意输入源,运行和休眠的时钟需要分配到不同的目的。图6显示的第一个实例是一个小型视频路由器、2.97G串行视频数据信号被分配到不同的位置。DS25CP104是LVDS交叉点开关系列中的一员,它可以处理直流到3.125Gbps的高速信号,具有非常低的抖动和很低的功耗,而且每个通道都可以通过SM总线监控和读取LOS的状态,LOS可以用来关断无用的通道。由于具有非常简单的SDI设备的接口、非常低的抖动和宽范围的数据率,使它广泛应用在开关和布线应用中。另外器件封装很小,是6×6mm的管脚排列。第二个例子是DS25BR204的应用,这个是非常简单的从2个可选的输入去复制4路信号的方法,同样具有LOS功能,可以实现功率的优化。

对于这类快速出现的用于3G- SDI传送的SMPTE424M标准,美国国家半导体公司是业界完整方案的最早的供应商,产品包括自适应均衡器、时钟恢复器、电缆驱动器、串行器、解串器、交差点开关等,这些产品满足SDI的每个应用,适用于各式各样的SDI系统。一个大型的布线系统,可能会需要所有的产品。在功耗要求越来越高的今天,一些产品的关断功耗可以只有3mW,信号丢失告警和电缆连接检测大大地简化了系统的设计。

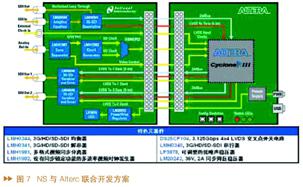

美国国家半导体公司和Altera公司合作完成了工业第一个3G/HD/SD-SDI系统的视频开发平台,它是基于Altera Cyclone III FPGA来实现的。该方案采用NS高性能的3G-SDI信号路径、视频时钟、电源管理器产品和Altera公司的FPGA产品,组成了标准的可扩展的开发平台。它包括了许多有特色的产品,例如3G-SDI产品、多视频格式的同步分离器、时钟产生器、交叉点开关、LDU和DC/DC转换器等等。

除了Altera公司以外,美国国家半导体公司也和Xilinx公司合作提供了类似的开发平台,美国国家半导体公司和Xilinx提供了联合方案,采用低价FPGA进入高端AVB市场的方法,它支持SD、HD和3G专业视频的应用。

-

11- 什么是串行数字接口 (SDI) ?EE_Voky 2022-09-15

-

关于SDI Video SFP光模块,你要了解这些2018-05-22 2568

-

升级至4K超高清12G-SDI接口时要考虑的三个问题2018-08-30 8710

-

高性能3G-SDI解决方案2019-05-06 4095

-

4K超高清12G SDI接口时研究需要考虑的三件事2019-06-24 4718

-

何为SDI?3G-SDI有哪些应用实例?2021-05-14 3990

-

串行数字视频信号传输系统-SDI接口2009-08-01 1547

-

可用于汽车娱乐和导航系统的3G-SDI解决方案2010-02-04 1089

-

美国半推出LMH0394串行数字接口(SDI)电缆均衡器2010-09-07 1942

-

SDI数字分量串行接口详解_王杰2016-05-18 1434

-

串行数据HD-SDI信号的特征及监测方法分析2018-09-04 17525

-

hd-sdi转hdmi转换器常见故障有哪些2020-04-21 4289

-

LCC262 SDI高清视频采集编码卡(H264编码)2023-05-26 792

-

串行数字接口SDI采集与H.264编码⼀体化采集卡LCC262数据手册2024-04-12 572

-

sdi接口和hdmi哪个好2024-08-20 5671

全部0条评论

快来发表一下你的评论吧 !