基于FPGA通过link口加载TigerSHARC信号处理系统的设计

描述

TigerSHARC系列处理器是ADI公司推出的高性能数字信号处理器,包含ADSP TS101、ADSP TS201、ADSP TS202、ADSP TS203。TigerSHARC系列处理器的link 口为处理器提供了快速、独立的通信机制。link口的特点是点对点通信、协议比较简单、数据率较高,因而可以通过link口实现多片处理器构成处理器系统。

TS101的link口和TS20X系列处理器的link口有所不同。TS101的link口采用8位双向数据线和三根控制线构成,采用TS101 link协议可实现双工通信;而TS20X系列处理器的link口采用LVDS技术(4 bit收、4 bit发),实现全双工通信。

尽管TS101的link口和TS20X的link口在物理和协议方面都不一样,但在应用上都可以实现数据的通信以及处理器的加载功能。

1 信号处理系统结构

典型的采用TigerSHARC处理器的信号处理板连接方式为:板(簇)内采用CLUSTER总线实现处理器连接,板间采用link口实现处理器连接。

采用FPGA实现与TigerSHARC处理器link口的连接可提高信号处理系统与其他系统连接的灵活性。FPGA通过link口与信号处理系统连接,简化了信号处理板卡的设计;同时由于FPGA灵活性及丰富的接口资源,可以很方便实现与其他系统的连接。

采用FPGA加载信号处理系统,只需修改与FPGA连接的Flash中的程序就可以实现配置信号处理器系统中各处理器的程序。在加载完后,FPGA还可以作为信号处理系统的接口板,使系统设计更加简单、高效。

本文介绍一种基于FPGA通过link口加载由TS101构成的信号处理系统的方法。

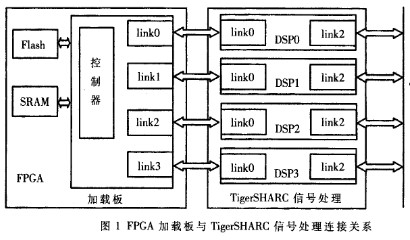

FPGA加载板和TigerSHARC信号处理系统连接关系如图1所示。

加载板采用EP2S60芯片作为处理器,外接128 MB Flash和36 MB SRAM。Flash用于存储处理器的加载程序,SRAM作为缓存。FPGA的4个link分别与TigerSHARC信号处理板上4个DSP的link0相连,信号处理板上4个DSP的link2分别与下一个信号处理器的4个DSP的link0相连。采用这种方法连接多块信号处理板构成一个信号处理系统。

TigerSHARC处理器每个link口都可以作为加载的端口,只需在Kernel程序中将LINK号改成对应的link口。

2 加载文件结构

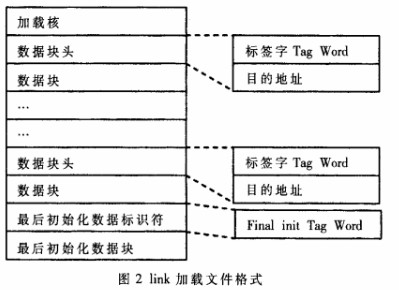

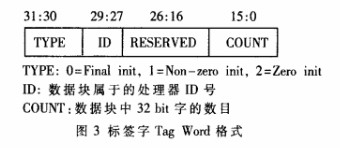

TigerSHARC处理器link口加载文件结构如图2所示。加载文件由加载核、若干Zero init或Non-zero init加载数据块及Final init数据块构成。加载核没有数据块头信息,Zero init 和Non-zero init数据块头都有1个标签字和1个目的地址,Final init数据块只有1个标签字。标签字各数据位的意义如图3所示。由于link口的连接特点,link加载核不支持多处理器加载,因而link加载方式中不使用ID。标签字的TYPE和COUNT指示了该块数据的类型和长度。TigerSHARC加载文件以32 bit word为单位构成(本文的word即指32 bit word)。

3 加载状态机的设计与实现

由于Flash的读写周期较长,设计中采用系统时钟16分频作为FPGA中Flash控制器的时钟。直接从Flash中读取数据无法保证DSP加载核(BOOT Loader Kernel)对程序数据的数据率要求,因而在设计中先将Flash中的数据转存到与FPGA相连的SRAM中。SRAM读出数据为32 bit,读写SRAM的数据率可以大大超过link口的吞吐率。FPGA中开辟2块RAM作为乒、乓RAM缓存从SRAM中读取数据,以保证FPGA发送link的数据保持在就绪状态,DSP加载核在任何时候取数,FPGA link都能提供有效数据。

FPGA发送到link模块的信号为TxWrite、TxData、TxBP。加载状态机根据TxBP信号来判断link口缓冲当前状态是忙还是空闲,只要为空闲状态就往link缓冲中写数据,从而保证了DSP加载核总能获取有效数据。

3.1 加载状态机的设计

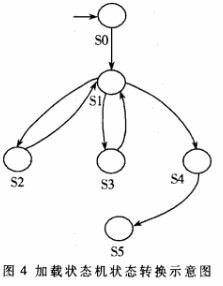

FPGA中加载有限状态机状态转换示意图如图4所示。

状态说明:

S0:BootLoader Kernel State;S1:数据块类型判断;S2:Non-zer init State;S3:Zero init State;S4:Final init State;S5:结束。

当需要加载时复位加载状态机,在复位时设置计数器值。复位后,状态机就进入了S0状态。

S0状态为发送DSP Boot Loader Kernel给需要加载的DSP,长度为256 words。在该状态下,link口需要发送DSP Boot Loader Kernel给需要加载的DSP,数据发送完后(数据块计数器count_packet为0),状态转入S1。

S1状态为上一数据块结束,下一数据块将要开始发送的一个中间过渡状态。在该状态下判断下一数据块的类型,并计算下一数据块的长度。根据标签字Tag Word的TYPE值转换到S2、S3、S4中的某个状态。

当S1状态下TYPE为1时,状态机转入S2。DSP收到这块数据后,进入Non-zero init模式。S2状态只需发送该数据块,不需要对数据进行Non-zero init处理。该模式下,link口需要发送的数据为该数据块标签字的COUNT值加上数据块头的长度即2 words。该数据块发送完后(数据块计数器count_packet为0),状态转入S1。

当S1状态下TYPE为2时,状态机转入S3。DSP收到这块数据后,进入Zero init State模式。该模式下加载程序数据块只有数据块头,即标签字和目的地址2 words,后面即为下一个数据块头。此时,状态机只需发送这个数据块头,不需要进行Zero init处理。该数据块发送完后(数据块计数器count_packet为0),状态转入S1。

当S1状态下TYPE为0时,状态机转入S4。相应地,DSP进入到Final init模式,完成加载核的自我覆盖。此时状态机要发送的有效数据长度为257 words,即1 word Final init标签字和256 words加载核自我覆盖程序。当发送完Final init加载数据,有效的加载程序已经发送完。需要注意的是,加载核在取link口数据是启动DMA传输的,而link口至内/外部存储器的DMA是以4字组方式传输,因而当程序不是4字对齐时,发送的加载程序长度须以4字补齐。加载状态机会根据加载文件自动完成4字补齐,发送的长度为将程序4字补齐后的长度,以满足link口DMA的时序要求。

当S4状态下数据块计数器count_packet为0时,状态机转入S5,加载1个DSP结束。

当状态机转入S5时,FPGA 的加载状态机已实现了通过link口对DSP的加载过程。为了实现信号处理系统中所有板卡的加载,第一块信号处理板要完成对第二块信号处理板卡的加载。link板卡的级联关系见图1,FPGA加载完第一块板的DSP后,等待DSP运行起来,而后通过link口发送第二块板的加载程序给第一块板。第一块板收到第二块板的加载程序后,可以实现对第二块板的加载。采用同样的方法就可以实现级联的每块板卡的每个DSP的加载功能。

3.2 Signal Tap采集加载过程

采用Signal Tap采集加载开始、中间状态转换和加载结束的结果分别如图5“7所示。图中各信号的意义如下:

boot_dsp0_en、boot_dsp1_en:分别是加载第一块信号处理板DSP0、DSP1的使能信号。

txdata、txwrite_ba_int、txbp:分别是link模块控制端输入数据、写控制信号、缓冲满信号count_packet的数据块计数器。

TAG_COUNT、TAG_TYPE:分别是标签字的COUNT和TYPE值。

STATE_FSM:状态机的当前状态。

rst_state:状态机复位控制信号。

l0_lxdata、l0_lxclkout、l0_lxclkin:分别是FPGA的link0端口接口数据、时钟/应答输出、时钟/应答输入。

图中采样时钟为link模块输入时钟,1个周期link口发送1 B数据。由于状态机采用的是边发送link数据边解译加载数据的方法,因而状态机状态转换过程要滞后发送数据4个周期(1 word),通过在发送DSP Boot Loader Kernel这个状态计数值多4个字而在Final Init过程计数值少4个字来实现对齐。

图5为加载开始,STATE_FSM状态为0,此时FPGA发送DSP Boot Loader Kernel给TigerSHARC DSP。加载开始时计数值为0x403 bytes,共发送0x404 bytes数据。如前所述,在发送DSP Boot Loader Kernel时比其实际长度0x400 bytes多4 bytes。

图6为加载中间加载过程,STATE_FSM状态依次为3、1、3、1、2。当STATE_FSM为第一个1时,TAG_TYPE为2、TAG_COUNT为3,标志下一个状态为Zero init State。此状态下FPGA需要发送2 words, 因而count_packet为0x6(count_packet为0占了2个周期)。当STATE_FSM为第二个1时,TAG_TYPE为1、TAG_COUNT为4,标志下一个状态为Non-zero init State,此状态下FPGA需要发送4 words数据和2 words数据块头,因而从此时count_packet为0x16(count_packet为0占了2个周期)。

如图7所示,当STATE_FSM为4且计数值为0时,STATE_FSM转为5、boot_dsp0_en从1变为0,此时加载DSP0结束。DSP0加载结束后FPGA产生一个状态复位信号rst_state使状态机复位,而后boot_dsp1_en从0变为1,开始加载DSP1。采用同样的方法就可以实现加载DSP2、DSP3。

本文介绍了一种采用FPGA加载TigerSHARC DSP的方法。在FPGA中设计的FSM可根据加载文件的结构自动实现加载功能,通过TigerSHARC DSP link互联关系可实现对整个信号处理系统的加载。此外,还介绍了加载状态机的设计方法,并采用Signal Tap采集加载状态机几个典型的加载过程,验证了加载状态机的设计。

-

基于FPGA+DSP弹载SAR信号处理系统设计2021-12-27 850

-

为什么采用FPGA去加载TigerSHARC DSP?2021-04-28 712

-

EE-200: ADSP-TS20x TigerSHARC®处理器的启动加载内核运行2021-03-21 778

-

基于FPGA控制的多DSP并行处理系统2019-05-21 2197

-

FPGA信号处理系统的散热解决方案介绍2019-04-23 4836

-

FPGA视频教程之使用FPGA进行嵌入式信号处理系统设计视频资料免费下载2019-03-29 1248

-

基于FPGA的振动信号采集处理系统设计并实际验证2017-11-18 4798

-

基于FPGA和DSP的高速图像处理系统2017-10-19 1087

-

基于FPGA的通用传感器信号处理系统设计_李辉2017-03-19 766

-

基于FPGA的雷达信号处理系统设计2015-10-30 1047

-

6U VME TigerSHARC201&FPGA信号处理机-LT-TS201-FPGAT2011-02-28 539

-

基于FPGA和DSP的光纤信号实时处理系统2009-06-19 842

-

基于FPGA 的交流信号采集与处理系统2009-05-16 702

全部0条评论

快来发表一下你的评论吧 !