在FPGA系统上实现自动检验功能的栈空间管理器的设计

描述

航空航天、工业控制、汽车电子和核电站建设等领域的高速发展,对嵌入式操作系统实时性的要求越来越高。同时,由于FPGA的集成度和速度的不断提高,使嵌入式操作系统硬件化实现成为发展趋势。硬实时操作系统中的堆栈管理对系统的实时性和可靠性起着至关重要的作用,而传统操作系统内核是将每个任务的堆栈空间直接进行最大化处理,导致大量存储空间浪费,另外采用通用RAM寻址方式也不能满足对被切换任务信息的快速保护。

基于上述问题,本文提出了一种堆栈空间结构,设计了一款具有自动检验功能的栈空间管理器,并在Xilinx公司的集成开发环境FPGA系统上实现。

1 堆栈空间结构

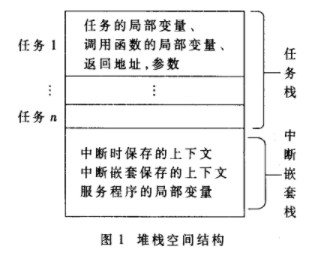

堆栈空间是按先进后出(LIFO)原则分配的连续存储器空间,可以满足保护任务切换信息和中断响应时保护处理器状态和任务参数数据的需要,且对每个任务分配一个单独的任务栈和一个响应系统中断任务的中断嵌套栈。如图1所示,栈空间划分为n个任务栈和1个中断嵌套栈。

任务栈主要保护被切换任务的信息。它存放的数据有:任务代码首地址、任务参数、任务中定义的局部变量、被调用函数的参数和局部变量及任务中各个函数的返回地址。中断嵌套栈存放被中断任务的数据,包括发生中断时需要保存的上下文、中断嵌套时需要保存的上下文和中断服务程序的局部变量。

在硬实时操作系统中,当发生中断或中断嵌套时,堆栈地址指针从任务栈切换到中断嵌套栈。当所有的中断服务程序全部执行完成后,堆栈地址指针从中断嵌套栈切换到任务栈,继续执行该被中断的任务。这种管理方式同以往操作系统采用被中断任务的数据保存到相应任务堆栈的方法相比,更有效节约了堆栈空间开销。

2 栈空间管理器总体结构

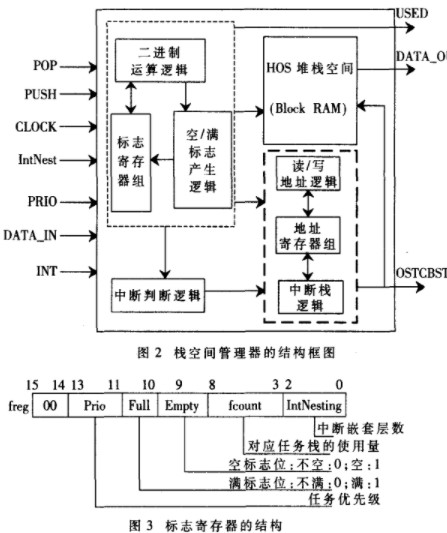

为了节约RAM开销,从总体结构上构建了一款具有LIFO及自检功能的栈空间管理器。栈空间管理器结构包括一个双端口存储单元、状态控制逻辑模块、地址产生逻辑模块、中断判断逻辑。其中状态控制逻辑模块由空/满标志产生逻辑、二进制运算逻辑和标志寄存器组3部分组成;地址产生逻辑模块由读/写地址逻辑、中断栈逻辑和地址寄存器组3部分组成。

由图2可知,状态控制逻辑模块的工作过程为:从标志寄存器组中读出当前任务栈的使用量fcount信号值,fcount信号值传送至二进制运算逻辑。在读/写控制信号有效的情况下,二进制运算逻辑有效,修改fcount信号值,修改后的值作为USED的输出值,同时写回到标志寄存器的对应fcount位中。修改后的信号值也作为空/满标志产生逻辑的输入信号,空/满标志产生逻辑生成Full/Empty标志,并把该标志位写回到标志寄存器对应位Full/Empty中。其中标志寄存器freg的结构如图3所示,初始值为0000001000000000B。

中断判断逻辑由输入信号INT与标志寄存器位IntNesting值决定是否有效。如果有中断发生,则中断栈逻辑有效,中断栈逻辑生成读/写地址,否则读/写地址逻辑有效,生成相应的读/写地址。

在读/写控制信号有效的情况下,从堆栈地址寄存器组中读出当前任务的地址,经过读/写地址逻辑或中断栈逻辑产生堆栈地址指针,作为HOS堆栈空间的入栈/出栈地址。执行入栈时,在同步时钟和入栈控制信号有效的情况下,中断判断逻辑判断是否存在中断或中断嵌套,如果没有,则由写地址逻辑生成入栈地址;否则由中断栈逻辑生成写地址。同理,执行出栈时,在同步时钟和出栈控制信号有效的情况下,中断判断逻辑判断是否存在中断或中断嵌套,如果没有,则读地址逻辑生成出栈地址;否则中断栈逻辑生成出栈地址。

3 栈空间管理器设计

为了快速、有效地保护被切换任务的信息,并满足自动检验功能的要求,在栈空间管理器设计中设计了2个逻辑模块,分别为状态控制逻辑模块和地址产生逻辑模块。状态控制逻辑模块主要生成入栈/出栈控制信号和Used信号,地址产生逻辑模块主要生成有效的入栈/出栈地址。基于对栈空间管理器总体结构工作过程的阐述,在Xilinx公司设计的XUPVirtexIIPro系列的芯片上设计一个模拟栈空间管理器,模拟管理8个任务,任务栈的深度为64,宽度为16bit,中断嵌套栈的深度为128,宽度为16bit,容量为10KB的堆栈空间。在设计管理器中,保证管理器快速综合,使占用FPGA的资源尽可能少,存储单元的选择是关键,该系统采用的是FPGA上一个18KB的BlockRAM资源,使用ISE8.2i提供的双端口RAM存储模块的IP核。如果选择其他方法,如用触发器和寄存器搭建存储单元,则综合时间长,且占用大量FPGA的Slices资源。

在实际嵌入式系统应用中,根据系统要求,可计算出栈空间深度和宽度,具体的深度和宽度在VHDL代码中修改即可。

3.1状态控制逻辑模块设计

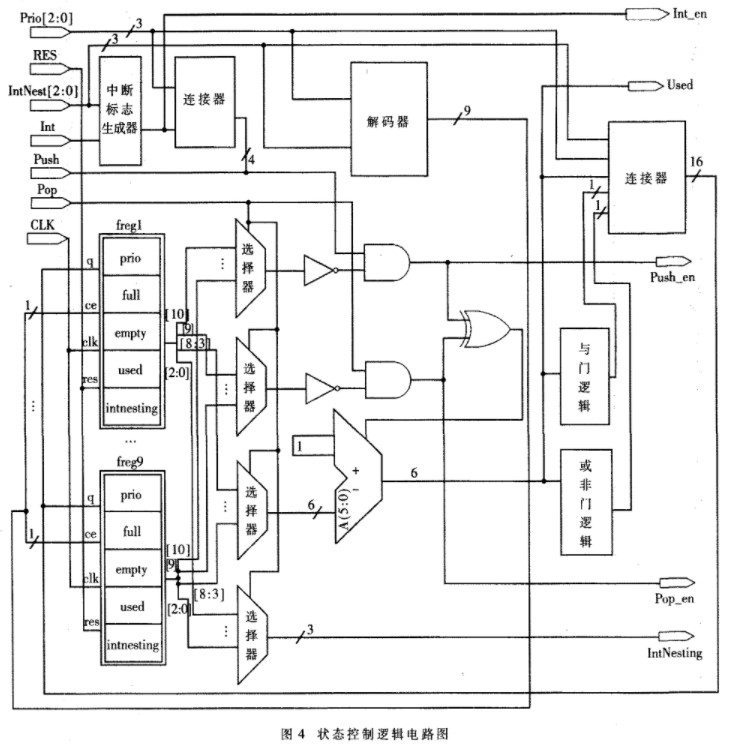

由于状态标志寄存器的空/满状态标志位决定栈空间入栈/出栈操作,所以如何设计空/满状态标志位是关键。为了保护的数据能正确入栈与出栈,防止存储器出现向上溢出或向下溢出,保证在满的情况下,不能进行push操作;在空的状态下,不能进行pop操作。控制信号的产生过程如图4所示。

在状态控制逻辑模块设计时,prio_int信号驱动4个多路选择器,选择对应状态标志寄存器组中的各位段,分别有full信号值、empty信号值、fcount信号值和intNesting信号值。empty/full信号和push/pop信号作为组合逻辑输入信号产生相应的push_en/pop_en有效控制信号,该控制信号决定栈空间是否执行入栈/出栈操作。

在push_en/pop_en控制信号有效的情况下,驱动二进制运算逻辑加/减1,输出运算结果。输出的信号值有3个用途:(1)作为空/满标志状态产生逻辑的输入信号,该信号逻辑产生empty/full信号;(2)写回到fregx对应的fcount位中;(3)作为Used输出信号值,表示当前任务栈或中断嵌套栈的使用情况。

在产生empty、full信号逻辑模块设计时,采用了对输入信号的每一位进行组合逻辑判断的方法,使该信号分两路,一路作为与门组合逻辑的输入信号产生full信号。如果输入信号的每一位都为1,则full信号置1,其他情况置0;另一路作为或门非组合逻辑的输入信号产生empty信号。如果输入信号的每一位都为0,则empty置1,其他情况置0。在整个逻辑模块设计中,采用组合逻辑设计,目的是缩短工作时延,提高系统工作频率。

3.2地址产生逻辑模块设计

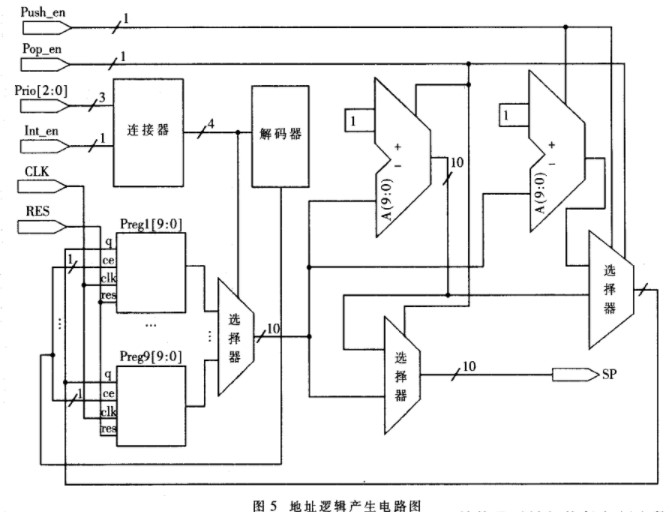

堆栈地址指针SP决定了堆栈空间单元的数据正确入栈和出栈,堆栈地址指针SP的获得在于如何驱动读/写逻辑模块和中断栈模块。为了确保被保护数据的有效性和实时性,防止出现不确定状态,须在时序同步的状态下,对数据进行操作,如图5所示。

在地址产生逻辑设计时,先对堆栈地址寄存器组赋初值,该模拟系统管理8个任务,有9个堆栈地址寄存器,分别为8个任务堆栈地址寄存器和1个中断嵌套栈堆栈地址寄存器。

当任务优先级Prio信号和中断使能int_en信号同时驱动多路选择器时,堆栈地址指针SP从堆栈地址寄存器组中选择存放在Pregx中的当前任务的地址,在设计的栈空间管理器中,SP指向栈空间的下一个存储单元的地址。如果入栈控制信号有效,则SP作为栈空间的寻址地址,写入数据,SP加1;如果出栈控制信号有效,则SP减1,改变后的SP值作为栈空间的寻址地址,读出数据。操作完成后,改变后的SP值写回到对应的堆栈地址寄存器组Pregx中。

4 仿真结果分析

本栈空间管理器容量为10KB,宽度为16bit。在ISE8.2i开发软件中进行了综合和仿真,设计中使用了294个Slices芯片、396个触发器芯片、274个inputLUTs、60个boundedIOBs、1个块BRAMs。

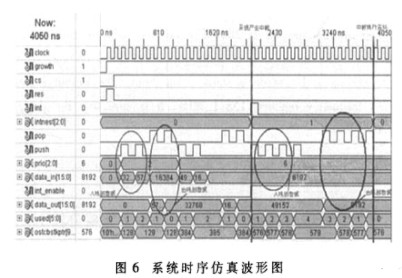

仿真时,输入十进制数的数据,图6为系统时序仿真波形图。

(1)当INT无效时,即系统中不存在中断或中断嵌套。在push有效的情况下,置prio信号值为2,data_in信号值分别为32768、57908。仿真时,输出结果为:used信号值分别为1、2,而ostcbstkptr信号值分别为128、129;同理,在pop有效情况下,置prio信号值为2,观察仿真结果为:dout_out信号值分别为32768、57908,used的信号值分别为1、0,ostcbstkptr信号值分别为129、128。由此可得,在无中断处理的条件下,根据任务的优先级prio,按LIFO原则在任务栈中写入和读出数据,并且每次的有效操作同时修改当前任务的used和ostcbstkptr信号值。

(2)当INT有效时,即系统中产生中断或存在中断嵌套。在push有效的情况下,置prio信号值为6及data_in信号值为8192,观察仿真结果为:used信号值依次为1、2、3、4,ostcbstkptr信号值依次为576、577、578、579;同理,在pop有效情况下,置prio为6,此时的仿真结果:data_out信号值为8192,used信号值依次输出4、3、2、1,ostcbstkptr信号值依次输出579、578、577、576。由此可得,当系统中产生中断或存在中断嵌套,按LIFO原则在中断嵌套栈中写入和读出数据,并且每次有效操作同时修改中断嵌套栈的used和ostcbstkptr的值。

由以上结果分析可知,该实验验证了栈空间管理器的正确性,符合系统设计的要求。

本文分析了堆栈空间结构及对被切换任务相应数据信息的保护,并对堆栈空间进行了合理的结构划分。实验数据表明了该系统的可行性和稳定性。栈空间管理器能有效节约硬实时操作系统分配堆栈空间的时间,减少RAM存储空间。从硬件角度上看,简化了设计,降低了成本,具有一定的使用价值。目前只在实验平台上仿真,下一步拟将栈空间管理器的IP核应用于硬实时操作系统,以提高操作系统的运行效率。

-

关于如何在LV中实现资源管理器2013-03-08 2263

-

光电测径仪在自动检测中的应用2018-08-28 3388

-

怎么在仪器管理器上显示查找仪器2019-03-18 1170

-

MCU堆空间和栈空间的相关资料分享2021-11-03 1321

-

雷达故障自动检测系统2009-07-15 676

-

啤酒生产线的啤酒瓶自动检验设备相关文档及源2009-08-03 424

-

基于FPGA的栈空间管理器的研究和设计2010-11-11 521

-

提高系统可靠性的电压管理器选2006-05-13 761

-

频宽管理器的防火墙功能2010-01-08 877

-

为MAX16046可编程系统管理器增加自动重启功能2012-04-07 1702

-

基于TCP/IP通信技术在Xilinx FPGA上的实现2017-09-04 990

-

封装下载管理器实例教学2017-09-26 706

-

数据库的项目管理器是什么?项目管理器详细资料总结2018-09-18 1899

-

为MAX16046 EEPROM可编程系统管理器添加自动重启功能2023-02-07 1307

-

负载管理器的主要功能2024-10-10 1250

全部0条评论

快来发表一下你的评论吧 !