基于PE3240 PLL芯片实现L波段频率源的设计方案

描述

锁相环(PLL)频率合成技术是频率源设计的一种现代化技术,已广泛应用于通信、导航、电子侦查、电子对抗、遥控遥测及现代化仪器仪表等领域中。

1、 集成锁相环芯片PE3240介绍

PE3240是Peregrine公司最新生产的一种可在高达2.2GHz频段工作的分频次数可编程的数字锁相环芯片,正常工作状态下功耗低于0.6W。PE3240采用了UltraCMOS技术,具有超低相位噪声的优良性能。

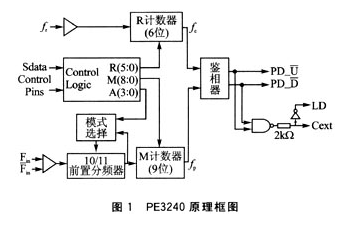

图1为PE3240芯片的原理框图。PE3240由双模前置分频器、计数器、鉴相器和控制逻辑组成。双模前7置分频器采用吞脉冲分频技术,通过模式选择确定对VCO输出频率是10分频还是11分频,通过20位寄存器的置数值,主计数器M和参考计数器R分别对双模前置分频器输出频率和参考频率进行分频,另外的计数器A,用于模式选择,鉴相器产生上下频率控制信号,还提供鉴相器测试和时钟检测输出功能。PE3240的分频置数采用三线串行模式。该芯片具有功耗低、相位噪声低、杂散小、分频频率高、编程灵活方便等优点。

PE3240主要电路性能为:

双模前置分频器(10或11分频);

9位M和4位A吞吐脉冲计数器;

6位R参考频率计数器;

低电源电压+3V供电;

输出频率范围为200-2200MHz;

参考频率最高为100MHz;

三线串行编程模式。

2、 频率源设计方案

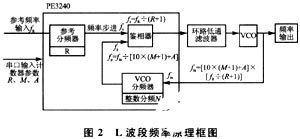

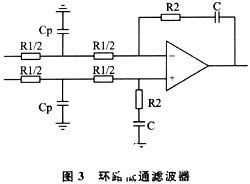

如图2所示,频率源原理框图以PE3240为核心。PE3240需要外接环路滤波器和压控振荡器。本设计中环路低通滤波器采用有源比例积分滤波器。如图3所示,环路低通滤波器的作用是滤除鉴相器输出电流中的无用组合频率分量及其他干扰分量,以保证环路所要求的性能,并提高环路的稳定性。

根据锁相环参数确定R、C等元件的值。需要注意的是,要将环路带宽设置在鉴相器噪声基底与VCO自由振荡时相位噪声的交叉点上,以提高PLL的相位噪声性能。

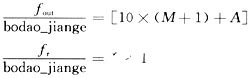

如图2所示,通过三线串口,由单片机将分频参数M、R、A置入PE3240,将输出频率进行[10×(M+1)+A]分频,作为鉴相器的一路输入,另一路鉴相器输入是将参考频率fR进行(R+1)分频,通过鉴相器后,得到与两路信号的相位误差成比例的误差电压,经环路低通滤波器,取出有用的直流电压分量,控制VCO的输出频率锁定在[10×(M+1)+A]×[fR/(R+1)]频率上。

本设计中,参考频率选为28MHz,R=39,A=3。这样,通过改变M值(119-159,步进为1),可得到频率间隔为7MHz,范围为842,1-1122.1MHz的稳定输出频率。

3、 与单片机接口及软件编程

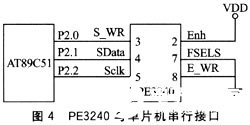

PE3240与单片机接口只有一种方式,即三线串口模式,电路连接如图4所示。

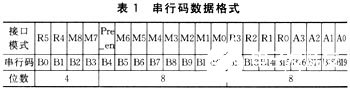

分频参数R、M、A是以20位串行码形式输入PE3240的。其中,R为6位,M为9位,A为4位,还有一位Pre_en为常0,数据格式如表1所列。

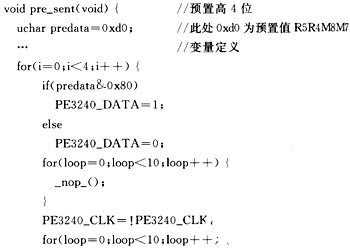

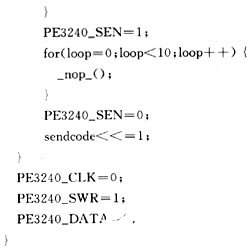

PE3240串口模式与SPI串口及RS232串口都不同,必须按照特定的时序实现串行码输入,即当S_WR为低电平时,在Sclk的上升沿,串行码被串行输入PE3240主寄存器,注意,高位R0先入。

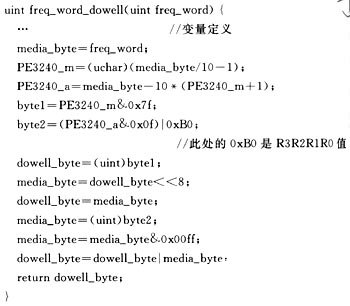

根据串口时序和数据格式,我们编写了使用高效的AT89C51单片机与PE3240的C51串口通信函数。具体如下:

本串口通信函数的设计十分巧妙,由于单片机一个字节是8位,因此把20位串行码分为高4位和低16位分别发送,高4位由预置函数置入,低16位由串行输入函数置入。

其中,分频参数R、M、A是根据输出频率的首频率和波道间隔,按下式计算:

4 、总结

根据本设计方案,制作的L波段频率源,已成功应用于无人机分米波仪表着陆系统设备中。性能指标良好:输出频率范围为842.1-1122.1MHz,频率间隔为7MHz,波道数为40;杂散抑制度>350dB;相位噪声≤-85dB(偏离中心频率10KHz处);频率稳定度为±1×10-6。

责任编辑:gt

-

C波段二级放大电路设计方案2023-11-07 677

-

一种用DDS激励PLL的X波段频率合成器的设计方案2023-10-24 575

-

X波段间接式频率综合器的方案分析2017-11-18 1633

-

基于DDS的短波射频频率源设计方案解析2017-11-08 1974

-

一种基于DDS的S波段频率源设计2017-01-13 820

-

基于HMC704LP4的一种X波段跳频源设计方案2013-10-22 10193

-

C波段频率源设计及性能分析2013-01-10 1221

-

一种X波段频率合成器的设计方案2012-06-28 1208

-

X波段低相噪跳频源的设计2012-03-20 876

-

l波段_l波段波长2011-12-31 24307

-

基于PE3236的L波段频率合成器设计2011-06-23 1442

-

L波段细步进捷变频频率综合器设计2010-04-22 2935

-

DDS+PLL高性能频率合成器的设计方案2010-04-17 5123

-

采用DDS+PLL技术实现的L波段频率合成器2009-09-11 1262

全部0条评论

快来发表一下你的评论吧 !