【深度报告】CoWoS封装的中阶层是关键——SiC材料

描述

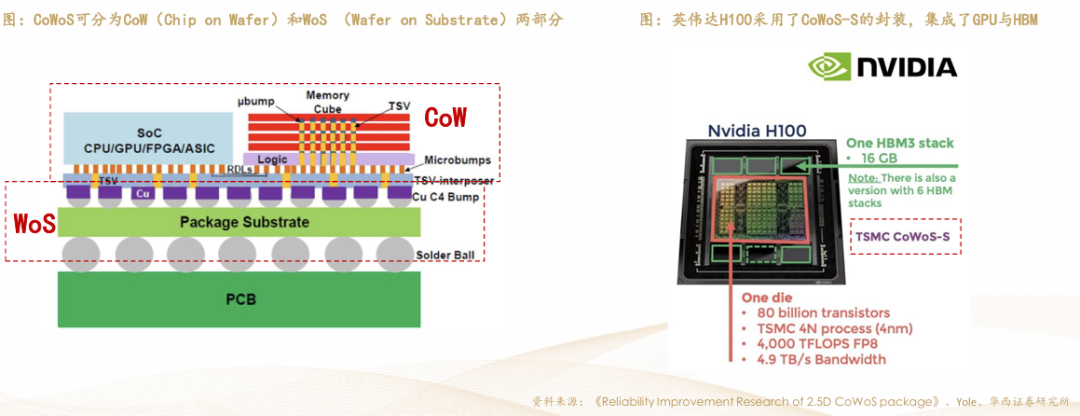

摘要:由于半导体行业体系庞大,理论知识繁杂,我们将通过多个期次和专题进行全面整理讲解。本专题主要从CoWoS封装的中阶层是关键——SiC材料进行讲解,让大家更准确和全面的认识半导体地整个行业体系。我们分为半导体知识、半导体“芯”闻几个模块,欢迎各位大佬交流学习。根据《Reliability Improvement Research of 2.5D CoWoS package》,2.5D CoWoS封装采用中介层互连技术,使用C2W(芯片到 晶圆)技术将ASIC、HBM和中介层连接为一个整体,再与基板连接,实现芯片、中介层和基板之间的互连。CoWoS技术旨在实现 更高集成度、更小封装尺寸、更短互连路径,以优化线宽和间距利用,提高传输速率,降低损耗和延迟。 • 根据天天IC,英伟达CEO黄仁勋在今年5月的采访中表示,CoWoS是非常先进的技术,“在目前除了CoWoS,我们无法有其他选 择”。

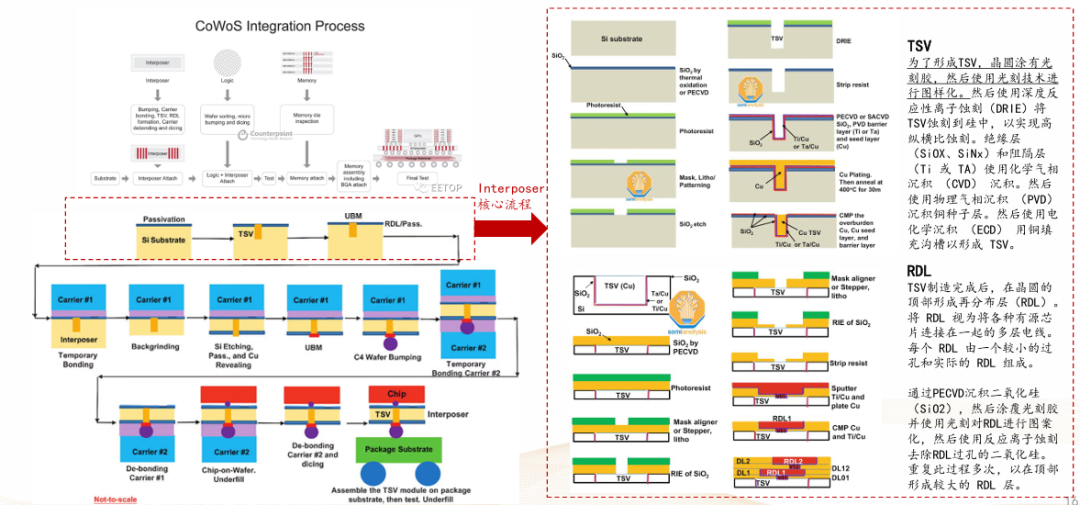

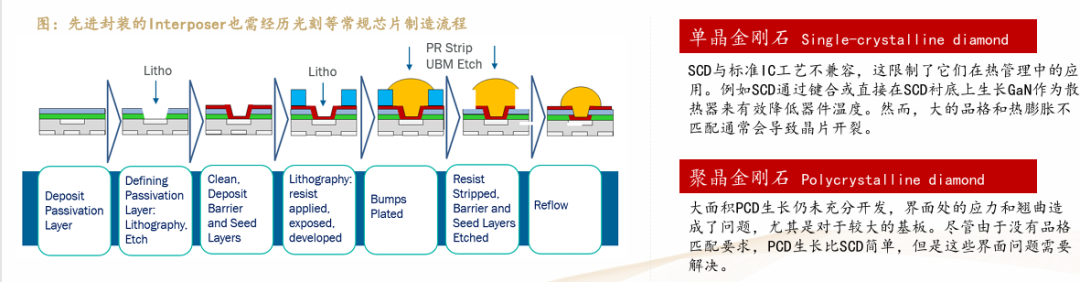

CoWoS制造流程根据Semianalysis,Interposer(中介层)的制造类似于传统的前端晶圆制造。

CoWoS核心价值在于interposer(中介层)的连通作用根据广电计量,CoWoS是由Chip on Wafer on Substrate缩写而来,即先将各主芯片和储存器集成堆叠到无源的Wafer(中介层) 上,再将CoW部分封装在有机载板Substrate上。 Interposer上的RDL使得各芯片之间的电信号可以直接交流,并通过Interposer中的硅通孔(TSV)传输到有机载板以完成与外界的 连接。这种封装形式具有以下优点:

1、减小器件所占用的面积,充分利用纵向空间,降低功耗; 2、缩短各芯片之间的电信号传输距离,减少导线寄生电容的影响。

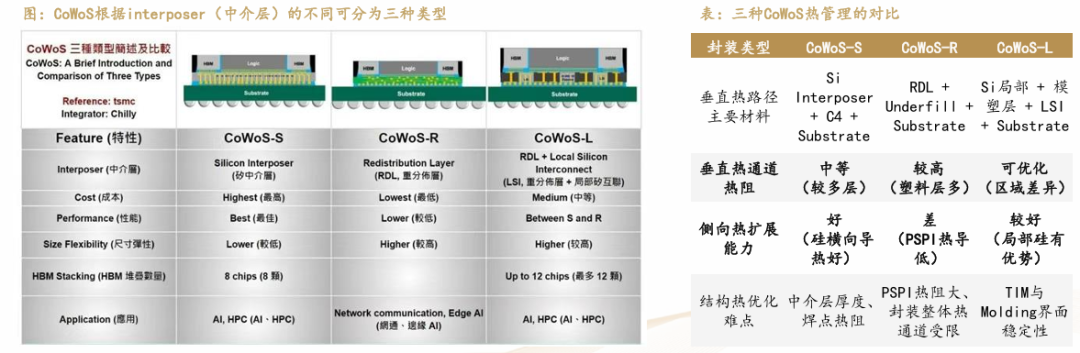

CoWoS核心在于interposer,目前可划分为S、R、L三种类型根据洞见热管理,CoWoS技术根据中介层所采用的材料不同,可分为CoWoS-S(硅中介层)、CoWoS-R(RDL重布线)和 CoWoS-L(LSI,重布线+部分硅中介层)三种类型。随着CoWoS封装在高性能计算(HPC)芯片上的广泛应用,其热管理问题正成为影响系统稳定性和性能释放的关键瓶颈。与传统封 装结构相比,CoWoS具备更高的集成密度和更复杂的堆叠结构,热流通路不再是单一方向的导热,而是需要穿越多个功能层、封装 材料和界面接触面。热路径中任何一层导热性能的不匹配,都可能导致局部热点、热阻叠加,进而限制芯片频率提升与长期可靠性。

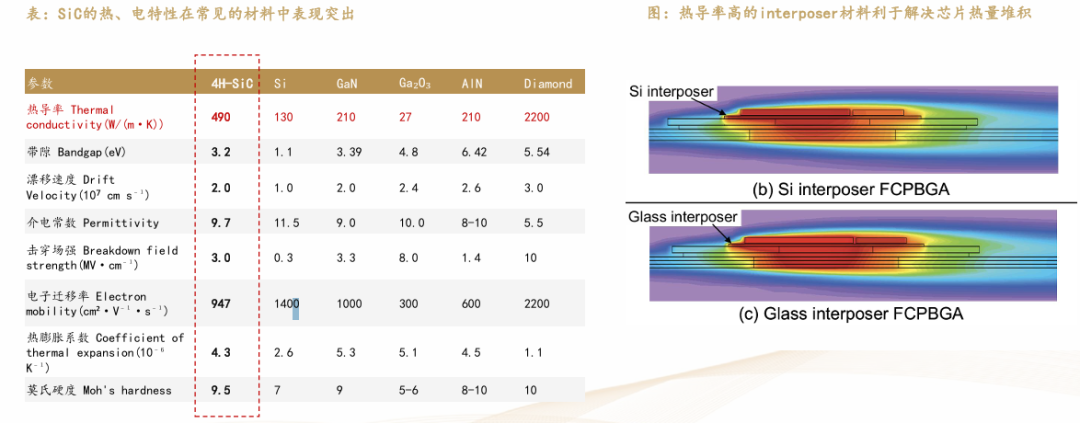

三种CoWoS热管理的特点CoWos-S :上行为散热路径:SoC顶部通过TIM与外部散热器/盖板连接,是主要热释放方 向; 下行路径中Si Interposer为硅材质,有较高热导率(约100-150 W/mK),但其 横向扩展面积较大,有一定散热作用,但热量最终还是需穿越多个热阻层(C4 bump、基板、焊料球)传至PCB;CoWoS-S结构下热路径较长、层级较多,每层 材料(如NCF、Underfill)均有热阻积累。 CoWos-R :去除了Si Interposer,减少了一个导热界面。RDL重布线层通常由聚酰亚胺 /PSPI与铜层构成,热导率远低于硅中介层(PSPI约0.3~0.5 W/m·K),成为热 瓶颈之一。此结构封装更轻薄、更经济,但热通道变窄、热扩展路径受限,适 合中等功率芯片或结合主动散热手段(如金属盖板/VC等)进行优化。CoWos-L :采用混合结构,将Si Interposer与RDL结合,局部引入硅中介层提升热导性, 同时通过模塑封装加强结构稳定性。LSI区块内部集成被动器件(IPD),可能 引入一定发热,同时也会形成热阻点。优点是兼顾热性能与良率,可进行定制 化热优化。对TIM、模塑材料(Molding)与Underfill提出更高热传导与可靠性 要求。Interposer的材料选择对芯片散热起到重要作用根据IBM的测试,玻璃中介层FCPBGA的逻辑芯片温度比硅中介层FCPBGA高约14℃,这仅仅是因为玻璃中介层的热导率较低。可 以看到热量在封装芯片中四处发散,在同等条件下热导系数更低的interposer材质,能使整体温度更低。

SiC用作Interposer的热性能有望高于现有的硅和玻璃

根据北京大学的相关论文,其制备的热管interposer在散热性能上显著优于硅与玻璃,证明了SiC衬底作为大功率器件散热主题材料 的潜力。虽然和CoWoS的interposer有差异,但从侧面验证了SiC在作为CoWoS中interposer的性能与可行性。

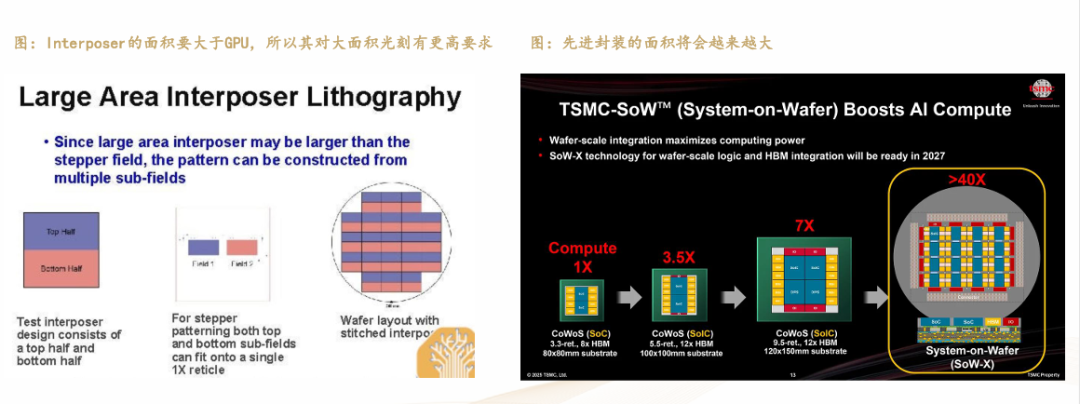

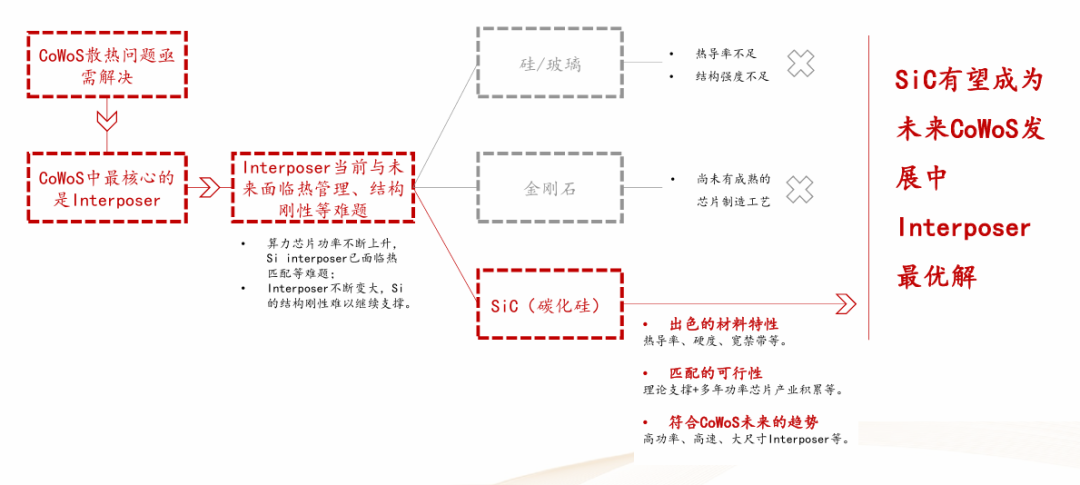

随着Interposer的变大,CoWoS的硅中介层还面临开裂等难题 金刚石仍难以匹配芯片制造工艺,使其目前还难以成为Interposer的选择根据Nature 25年8月新文章,金刚石无论是单晶或是多晶,在IC散热领域应用仍存在较多可行性问题。 Interposer的制造需要经历光刻等制造工艺,且对材料的要求高。根据Semianalysis,芯片的最大尺寸通常为26 毫米x 33 毫米, 因为光刻工具的狭缝/扫描将该尺寸最大化。由于仅GPU 芯片就接近这个限制,并且还需要将HBM 安装在它周围,因此中介层需 要很大。未来的先进封装对光刻等制造工艺还提出了更高要求。根据Veeco,未来五年内互连密度要求不断提高,将推动对更小线路/空间要 求的需求。这些要求正在影响用于创建先进封装结构的封装技术。特别是,光刻和相关的湿法工艺在整个工艺领域都面临着挑战, 从凸块、柱子和RDL 到贯穿硅通孔(TSV)、中介层和混合键合。 •因此我们认为在金刚石在尚未能解决芯片制造(如光刻、刻蚀、镀膜等)的基本要求之前,还难以成为interposer的选项.

金刚石仍难以匹配芯片制造工艺,使其目前还难以成为Interposer的选择根据Nature 25年8月新文章,金刚石无论是单晶或是多晶,在IC散热领域应用仍存在较多可行性问题。 Interposer的制造需要经历光刻等制造工艺,且对材料的要求高。根据Semianalysis,芯片的最大尺寸通常为26 毫米x 33 毫米, 因为光刻工具的狭缝/扫描将该尺寸最大化。由于仅GPU 芯片就接近这个限制,并且还需要将HBM 安装在它周围,因此中介层需 要很大。未来的先进封装对光刻等制造工艺还提出了更高要求。根据Veeco,未来五年内互连密度要求不断提高,将推动对更小线路/空间要 求的需求。这些要求正在影响用于创建先进封装结构的封装技术。特别是,光刻和相关的湿法工艺在整个工艺领域都面临着挑战, 从凸块、柱子和RDL 到贯穿硅通孔(TSV)、中介层和混合键合。 •因此我们认为在金刚石在尚未能解决芯片制造(如光刻、刻蚀、镀膜等)的基本要求之前,还难以成为interposer的选项.

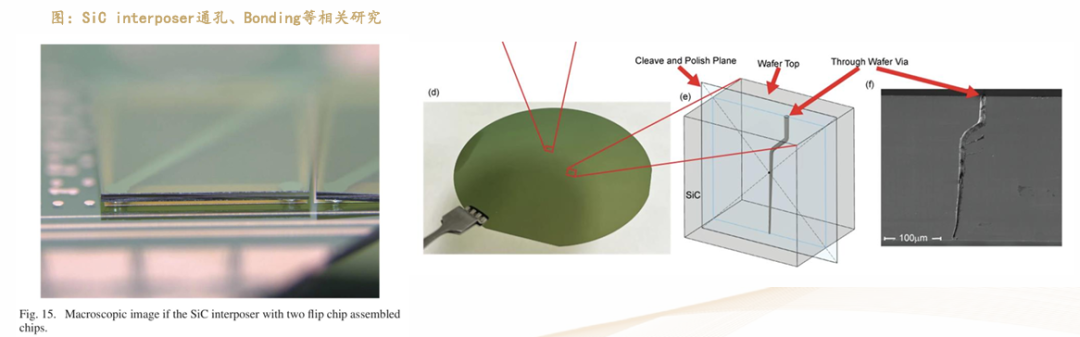

SiC成为解决Interposer痛点的重要方向根据Semivision,芯片的内部热路径涉及多层——硅衬底、金属互连、微凸块、底部填充、热界面材料(TIM)等。由于这些分层 的热界面,热量无法100% 有效地传递到盖子上,从而导致局部“热点”。这种累积热阻是限制芯片最大功率输出的主要因素之 一。提高热传导效率第一个关键在于缩短热路径并降低每层的界面热阻,并结合引入高导热材料,例如:SiC 衬底等。 • 近些年Piotr Mackowiak、Jared E. Payne等团队已在SiC的interposer上做了通孔、Bonding等相关研究,我们认为SiC用于先进封装 领域的interposer做了较好的理论指导,结合SiC产业链在功率器件领域多年的芯片制造经验,SiC作为CoWoS的Si interposer未来替 代者已具备一定的理论和产业基础。

SiC在散热和结构强度等关键指标上优于当前的Si材质根据Semisam,英伟达和台积电要尝试开发SiC衬底主要有两个原因:一是散热,仅HBM 产生的热量就很大,GPU 本身也会产生 大量热量。所需的热规格已经变得如此苛刻,以至于传统的硅中介层已经达到了极限;二是其非凡的强度,与易碎的玻璃基板不同, SiC 的坚固性要高得多。

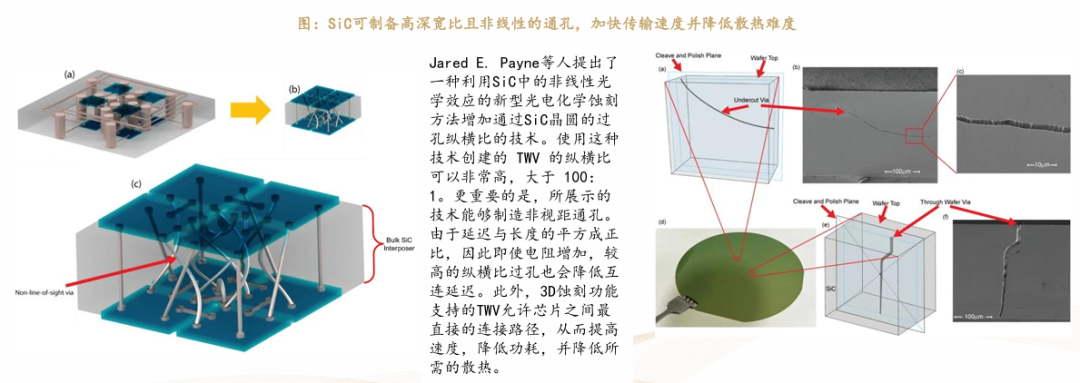

SiC通孔有望实现高深宽比,进一步契合先进封装未来高速、降温方向根据Nature,3D 集成涉及使用具有导电晶圆通孔(TWV)的中介层芯片,该芯片集成了两个或多个小芯片。这些小芯片可以连接 到中介层的同一侧和/或不同侧。TWV 提供小芯片之间的电气互连。为了实现高性能,小芯片之间需要高密度的互连。中介层中 TWV 密度的极限由TWV 的最大纵横比决定,许多高纵横比通孔研究都使用硅作为其TWV 衬底。然而,由于连接的小芯片会产生 大量热量,因此需要具有高导热性的中介层来实现高性能。单晶碳化硅(SiC)是一种具有高导热性的半导体,这种属性可提供高 散热性。

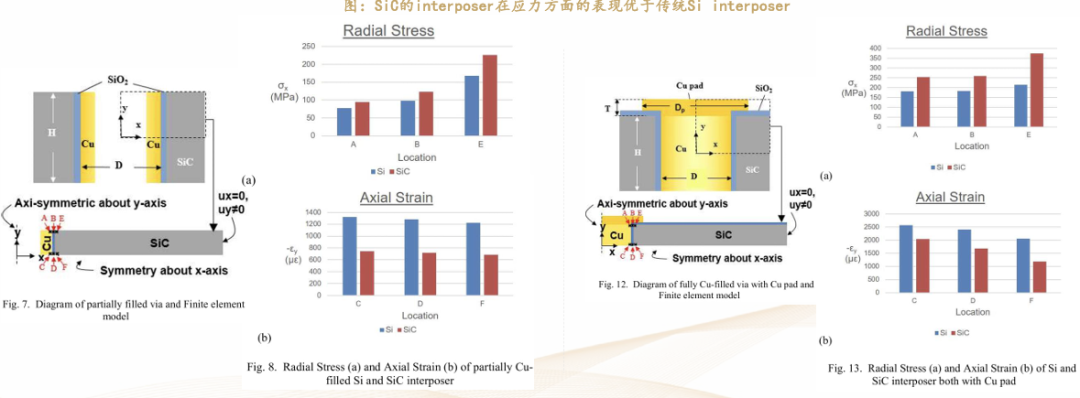

SiC在结构强度上也胜于Si,减少此前开裂、翘曲等问题根据Semivision,在 CoWoS-S 中,硅中介层与TSV 相结合可提供出色的信号和电源完整性。然而,一旦中介层尺寸超过光罩边界, 产量和机械脆性风险就会急剧上升。台积电正在探索使用单晶碳化硅(SiC)作为中介层或衬底,旨在利用SiC卓越的导热性和机械 坚固性来增强散热和可靠性,同时克服硅中介层固有的尺寸和材料限制。 • 根据《Nonlinear Thermal Stress/Strain Analyses of Through SiC Via》,SiC中介层在界面处比硅中介层具有更高径向应力和更小 轴向应变。

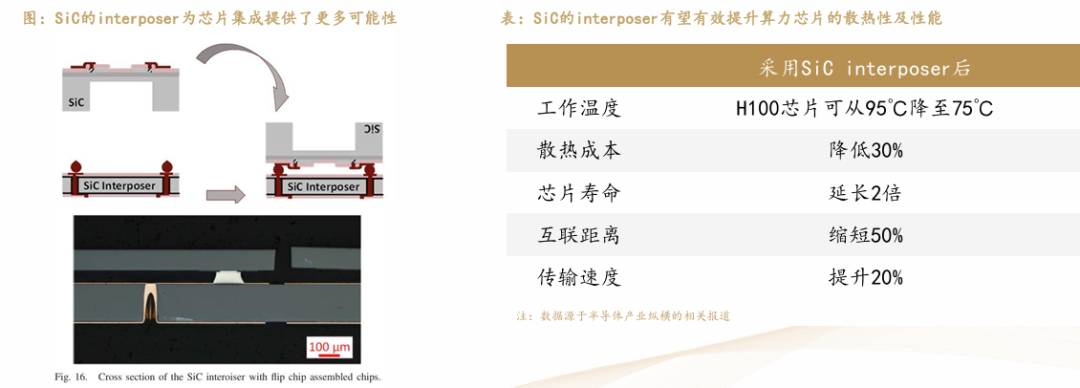

SiC在Interposer上的应用有望进一步扩展未来先进封装的性能边界根据Piotr Mackowiak等人的论文,介绍了碳化硅(SiC)干法蚀刻工艺的开发与优化主要成果,研究成果应用于开发200μm厚带铜 金属化的SiC中介层,所开发的蚀刻技术利用了SiC优异的电学和机械性能,为宽禁带衬底的3D集成提供了多种应用可能。 •根据半导体产业纵横,SiC中介层的优势十分显著:热导率达490W/mK(是硅的3倍以上),热膨胀系数(4.3ppm/℃)与芯片材料 高度契合,既能高效散热,又能保障封装稳定性。

SiC有望成为未来CoWoS发展中Interposer最优解 本文部分内容引自华西证券研究所

本文部分内容引自华西证券研究所

-

CoWoS(Chip-on-Wafer-on-Substrate)先进封装工艺的材料全景图及国产替代进展2026-03-28 625

-

HBM技术在CowoS封装中的应用2025-09-22 2661

-

CoWoS先进封装技术介绍2024-12-17 6085

-

深度了解SiC材料的物理特性2024-11-14 3915

-

IGBT和SiC封装用的环氧材料2024-10-18 2567

-

华立搭乘CoWoS扩产快车,封装材料业绩预翻倍2024-09-06 1718

-

什么是CoWoS封装技术?2024-08-08 10812

-

什么是 CoWoS 封装技术?2024-06-05 2290

-

CoWoS先进封装是什么?2023-07-31 6065

-

如何区分Info与CoWoS封装?2023-06-20 5148

-

归纳碳化硅功率器件封装的关键技术2023-02-22 2934

-

GaN和SiC区别2022-08-12 10136

-

SiC功率器件的封装技术研究2018-09-11 3000

-

金属封装材料的现状及发展(下)2018-08-23 3152

全部0条评论

快来发表一下你的评论吧 !