深入解析 8P34S2106A:高性能双路 1:6 LVDS 输出扇出缓冲器

电子说

描述

深入解析 8P34S2106A:高性能双路 1:6 LVDS 输出扇出缓冲器

在电子设计领域,时钟和数据信号的分配至关重要,它直接影响着系统的性能和稳定性。今天,我们要深入探讨的是瑞萨(Renesas)的 8P34S2106A 双路 1:6 LVDS 输出 1.8V/2.5V 扇出缓冲器,这是一款在高频、低相位噪声时钟和数据信号分配方面表现卓越的器件。

文件下载:Renesas Electronics 8P34S2106A扇出缓冲器.pdf

1. 器件概述

8P34S2106A 是一款高性能、低功耗的差分双路 1:6 LVDS 输出扇出缓冲器,支持故障安全操作,专为高频、极低附加相位噪声的时钟和数据信号扇出而设计。它具有两个独立的缓冲通道,每个通道有六个低偏斜输出,通道间的高隔离度可最大程度减少噪声耦合,并且通道间的交流特性(如传播延迟)相匹配。其输出到输出以及器件间的偏斜特性保证了该器件非常适合那些对性能和可重复性要求较高的时钟分配应用。

1.1 关键特性

- 双路 1:6 低偏斜、低附加抖动 LVDS 扇出缓冲器:能够提供稳定、低抖动的信号输出。

- 通道间匹配的交流特性:确保信号在不同通道间的一致性。

- 通道间高隔离度:有效减少通道间的噪声干扰。

- 低功耗:降低系统的整体功耗。

- 多种输入电平兼容:差分 CLKA、nCLKA 和 CLKB、nCLKB 输入可接受 LVDS、LVPECL 和单端 LVCMOS 电平。

- 高输入时钟频率:最大输入时钟频率可达 2GHz。

- 可选择的输出幅度:输出幅度有 350mV、500mV 和禁用三种可选。

- 低输出偏斜:输出组偏斜典型值为 10ps,输出偏斜典型值为 212ps。

- 低附加相位抖动:RMS 典型值为 45fs($f_{REF}=156.25 MHz$,12kHz - 20MHz)。

- 宽电源电压范围:支持 1.8V 和 2.5V 电源电压模式。

- 低电流消耗:1.8V 时典型电流消耗为 210mA,2.5V 时典型电流消耗为 230mA。

- 环保封装:采用无铅(RoHS 6)的 40 - VFQFPN 封装,尺寸为 6 × 6 × 0.9 mm。

- 宽工作温度范围:环境工作温度范围为 - 40°C 至 85°C,支持最高 105°C 的外壳温度。

1.2 应用领域

该器件适用于多种领域,包括 4.5G 和 5G 无线接入单元(RU)和分布式单元(DU)、交换机/路由器、医疗成像以及专业音频和视频等。

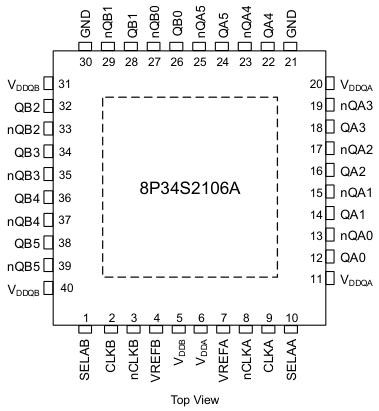

2. 引脚信息

2.1 引脚分配

8P34S2106A 共有 40 个引脚,每个引脚都有其特定的功能。详细的引脚分配图如下:

2.2 引脚描述

| 引脚编号 | 引脚名称 | 引脚类型 | 引脚描述 |

|---|---|---|---|

| 1 | SELAB | 输入 [PD/PU] | 控制输入,用于选择通道 B 的输出幅度 |

| 2 | CLKB | 输入 [PD] | 通道 B 的非反相差分时钟/数据输入 |

| 3 | nCLKB | 输入 [PD/PU] | 通道 B 的反相差分时钟/数据输入 |

| 4 | VREFB | 输出 | CLKB、nCLKB 输入对的偏置电压参考 |

| 5 | VpDB | 电源 | 通道 B 核心和输入的电源引脚 |

| 6 | VDDA | 电源 | 通道 A 核心和输入的电源引脚 |

| 7 | VREFA | 输出 | CLKA、nCLKA 输入对的偏置电压参考 |

| 8 | nCLKA | 输入 [PD/PU] | 通道 A 的反相差分时钟/数据输入 |

| 9 | CLKA | 输入 [PD] | 通道 A 的非反相差分时钟/数据输入 |

| 10 | SELAA | 输入 [PD/PU] | 控制输入,用于选择通道 A 的输出幅度 |

| 11 | VDDQA | 电源 | 通道 A 输出 QA[0:5] 的电源引脚 |

| 12 - 25 | QA[0:5]、nQA[0:5] | 输出 | 通道 A 的差分输出对,LVDS 接口电平 |

| 26 - 39 | QB[0:5]、nQB[0:5] | 输出 | 通道 B 的差分输出对,LVDS 接口电平 |

| 21、30 | GND | 电源 | 电源接地 |

| 31、40 | VDDQB | 电源 | 通道 B 输出 QB[0:5] 的电源引脚 |

| ePad | GND_EPAD | 电源 | 封装的外露焊盘,连接到地 |

2.3 功能表

-

SELAA 输出幅度选择表 SELAA QA 输出幅度 (mV) 0 350 浮空(默认) 500 1 禁用(掉电) -

SELAB 输出幅度选择表 SELAB QB 输出幅度 (mV) 0 350 浮空(默认) 500 1 禁用(掉电)

3. 规格参数

3.1 绝对最大额定值

| 在使用该器件时,需要注意不要长时间在绝对最大额定值附近工作,否则可能会影响产品的可靠性并导致故障。具体的绝对最大额定值如下: | 项目 | 额定值 |

|---|---|---|

| 电源电压 | 4.6V | |

| 输入电压 | - 0.5V 至 | |

| 输入电流 | 20mA | |

| 输出连续电流 | 10mA | |

| 输出浪涌电流 | 15mA | |

| 输入灌/拉电流 | 2mA | |

| 最大结温 | 125°C | |

| 存储温度 | - 65°C 至 150°C | |

| ESD - 人体模型 | 2000V | |

| ESD - 充电设备模型 | 1500V |

3.2 直流特性

-

直流输入特性 符号 参数 测试条件 最小值 典型值 最大值 单位 GIN 输入电容 2 pF RPULLDOWN 输入下拉电阻 51 kΩ RPuLLUP 输入上拉电阻 51 kΩ -

电源直流特性 在不同电源电压和温度条件下,该器件的电源直流特性如下: 电源电压 测试条件 最小值 典型值 最大值 单位 1.8V ± 5% QA[0:5]、QB[0:5] 输出端接 100Ω 负载,500mV 幅度 300 390 mA QA[0:5]、QB[0:5] 输出端接 100Ω 负载,350mV 幅度 210 275 mA QA[0:7]、QB[0:7] 输出禁用,SELAA = SELAB = 1 48 77 mA 2.1V - 2.7V QA[0:5]、QB[0:5] 输出端接 100Ω 负载,500mV 幅度 325 405 mA QA[0:5]、QB[0:5] 输出端接 100Ω 负载,350mV 幅度 230 290 mA QA[0:7]、QB[0:7] 输出禁用,SELAA = SELAB = 1 48 77 mA

3.3 交流特性

| 该器件的交流特性包括输入频率、传播延迟、输出偏斜、附加相位抖动等参数,具体如下: | 符号 | 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|---|

| fREF | 输入频率 | 2 | GHz | ||||

| AVAt | 输入边沿速率 | 1.5 | V/ns | ||||

| tpD | 传播延迟 | CLKA 到任意 QAx,CLKB 到任意 nQBx | 100 | 255 | 400 | ps | |

| tsk(o) | 输出偏斜 | 20 | 40 | ps | |||

| tsk(b) | 输出组偏斜 | 10 | 25 | ps | |||

| tsk(p) | 脉冲偏斜 | fREF = 100MHz | 5 | 25 | ps | ||

| tsk(pp) | 器件间偏斜 | 200 | ps | ||||

| tJIT | 缓冲器附加相位抖动,RMS | fREF = 156.25MHz;方波,$V{DD}[3]=1.8V±5%$,$V{pp}=0.5V$;积分范围:1kHz - 40MHz | 60 | 80 | fs | ||

| fREF = 156.25MHz;方波,$V{DD}[3]=2.5V$,$V{pp}=0.5V$;积分范围:1kHz - 40MHz | 54 | 75 | fs | ||||

| fREF = 156.25MHz;方波,$V{DD}[3]=2.5V$,$V{pp}=1V$;积分范围:12kHz - 20MHz | 40 | 55 | fs | ||||

| M(≥30M) | 时钟单边带相位噪声 | 230MHz 偏离载波和噪声底,$V_{DD}[3]=1.8V$ | <- 160 | dBc/Hz | |||

| 230MHz 偏离载波和噪声底,$V_{DD}[3]=2.5V$ | <- 165 | dBc/Hz | |||||

| tJIT.SP | 杂散抑制,通道间耦合 | fA = 491.52MHz,fB = 61.44MHz;$V_{DD}[3]=1.8V$,在相邻输出间测量 | - 59 | dB | |||

| fA = 491.52MHz,fB = 15.36MHz;$V_{DD}[3]=1.8V$,在相邻输出间测量 | - 59 | dB | |||||

| fA = 491.52MHz,fB = 61.44MHz;$V_{DD}[3]=2.5V$,在相邻输出间测量 | - 54 | dB | |||||

| fA = 491.52MHz,fB = 15.36MHz;$V_{DD}[3]=2.5V$,在相邻输出间测量 | - 67 | dB | |||||

| tR/tF | 输出上升/下降时间 | 10% 至 90%,输出负载 100Ω,$V_{DD}[3]=1.8V±5%$ | 150 | 400 | ps | ||

| 20% 至 80%,输出负载 100Ω,$V_{DD}[3]=1.8V±5%$ | 90 | 160 | ps | ||||

| 10% 至 90%,输出负载 100Ω,$V_{DD}[3]=2.1V - 2.7V$ | 200 | 420 | ps | ||||

| 20% 至 80%,输出负载 100Ω,$V_{DD}[3]=2.1V - 2.7V$ | 110 | 190 | ps |

4. 附加相位抖动

附加相位抖动是衡量时钟信号质量的重要指标之一。在 8P34S2106A 中,通过相位噪声测量来评估附加相位抖动。相位噪声是指在特定偏移频率处的 1Hz 带宽内的噪声功率与基频功率的比值,通常用 dBc/Hz 表示。在不同测试条件下,该器件的附加相位抖动典型值在几十飞秒(fs)级别,表现出良好的时钟信号纯度。

需要注意的是,相位噪声测量会受到测量设备的限制,设备的噪声底可能高于或低于器件的噪声底,因此附加相位噪声既取决于输入源的噪声底,也取决于测量设备。

5. 应用信息

5.1 故障安全操作

该器件的所有时钟输入支持故障安全操作,即在器件掉电时,时钟输入可以保持高达 4.6V 的直流电压,而不会损坏器件或输入引脚。

5.2 未使用输入和输出引脚的建议

- 输入引脚

- CLK/nCLK 输入:对于不需要使用差分输入的应用,CLK 和 nCLK 可以浮空。为了增加保护,可以从 CLK 连接一个 1kΩ 电阻到地。

- LVCMOS 控制引脚:所有控制引脚都有内部上拉电阻,不需要额外的电阻,但可以添加一个 1kΩ 电阻以增加保护。

- 输出引脚

- LVDS 输出:所有未使用的 LVDS 输出对可以浮空或跨接 100Ω 电阻。如果浮空,不应有走线连接。

- VREFXX:未使用的 VREFA、VREFBA 和 VREFB 引脚可以浮空,建议不要有走线连接。

5.3 差分输入连接以接受单端电平

通过合理的电路设计,可以使差分输入接受单端电平。例如,通过设置参考电压 V1 满足 VCMR 要求,使用旁路电容 C1 过滤直流偏置上的噪声,并且调整电阻 R1 和 R2 的比值来确保 V1 符合要求。同时,需要保证驱动器的输出阻抗和串联电阻之和等于传输线阻抗,并在输入处进行匹配端接以衰减信号。

5.4 1.8V 差分时钟输入接口

CLK / nCLK 可以接受 LVDS、LVPECL 和其他差分信号,但输入信号必须满足 $V{PP}$ 和 $V{CMR}$ 输入要求。对于不同类型的驱动器,需要根据其推荐的端接方式进行连接。

5.5 LVDS 驱动器端接

对于一般的 LVDS 接口,推荐的端接阻抗($Z{T}$)在 90Ω 至 132Ω 之间,实际值应根据传输线的差分阻抗($Z{0}$)进行选择。典型的点对点 LVDS 设计在接收器端使用 100Ω 并联电阻,并采用 100Ω 差分传输线环境。为了避免传输线反射问题,元件应采用表面贴装,并尽可能靠近接收器放置。

5.6 VFQFPN EPAD 热释放路径

为了最大限度地提高封装的散热和电气性能,需要在印刷电路板(PCB)上

- 相关推荐

- 热点推荐

-

CDCLVD2104:高性能双路1:4低附加抖动LVDS缓冲器解析2026-02-09 399

-

低抖动高性能之选:LMK1D210xL LVDS时钟缓冲器深度解析2026-02-06 346

-

深入解析ISO782xLL:高性能隔离式LVDS缓冲器的卓越之选2026-01-23 430

-

深入解析RC190xx:PCIe Gen5/6高性能扇出缓冲器家族2025-12-30 1152

-

深入解析SN65LVEL11:高性能1:2 ECL扇出缓冲器2025-12-25 468

-

CDCLVD2106 双路1:6低附加抖动LVDS缓冲器技术文档总结2025-09-16 883

-

CDCLVD2106双通道1:6低加性抖动LVDS缓冲器数据表2024-08-21 387

-

8P34S2106A 数据表2023-01-11 510

全部0条评论

快来发表一下你的评论吧 !