Renesas RZ/G2L, RZ/V2L SMARC模块板硬件设计解析

电子说

描述

Renesas RZ/G2L, RZ/V2L SMARC模块板硬件设计解析

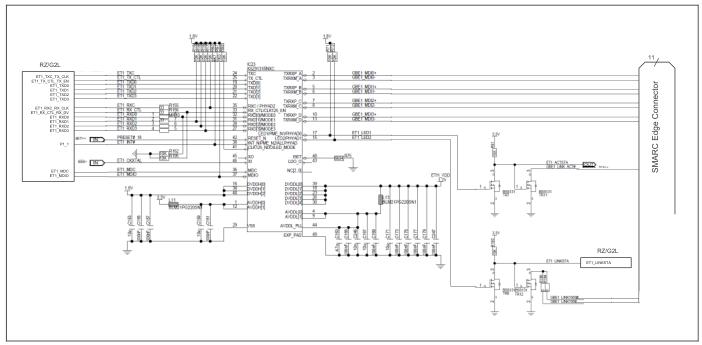

在嵌入式系统开发领域,Renesas的RZ/G2L和RZ/V2L SMARC模块板因其高性能和丰富的功能,成为了众多电子工程师关注的焦点。本文将深入剖析RTK9744L23C01000BE模块板的硬件设计,为大家在实际应用中提供有价值的参考。

文件下载:Renesas Electronics RZ,V2L SMARC PMIC套件.pdf

一、概述

RTK9744L23C01000BE是一款用于评估Renesas Electronics微处理器RZ/G2L “R9A07G044L23GBG”功能和性能的模块板,同时也可用于评估应用软件开发。它与RTK9754L23C01000BE的主要区别在于后者使用了Renesas Electronics微处理器RZ/V2L "R9A07G054L23GBG",不过两者引脚兼容,功能相似。

1.1 特性亮点

- 丰富的外部存储:配备了2GB的DDR4 SDRAM、512Mb的QSPI闪存和64GB的eMMC内存,为系统提供了充足的存储空间。

- 灵活的启动方式:设置了microSD卡插槽,可作为eSD用于启动系统。

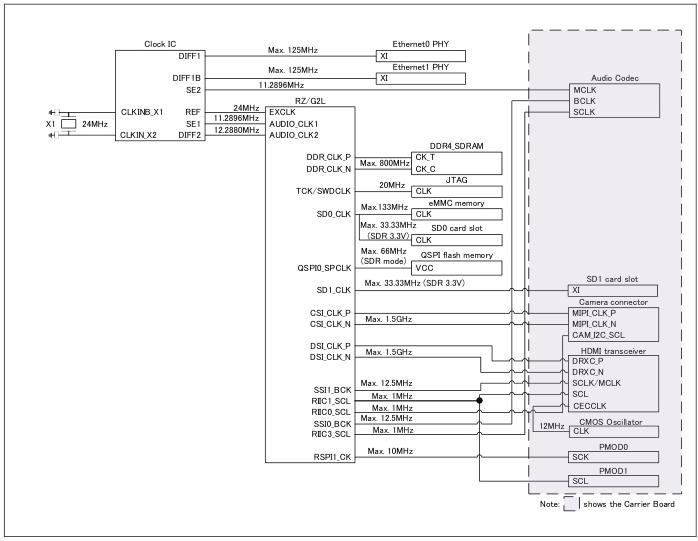

- 稳定的时钟供应:搭载了5输出时钟发生器“5P35023”,确保系统时钟的稳定性。

- 高效的电源管理:采用PMIC “RAA215300”作为电源电路,为系统各部分提供稳定的电源。

- 高速的网络连接:集成了以太网PHY,支持10/100/1000Mbps的数据收发。

- 便捷的扩展接口:未使用的端子连接到314引脚、0.5mm间距的连接器,可与载板配合使用,方便进行功能扩展。

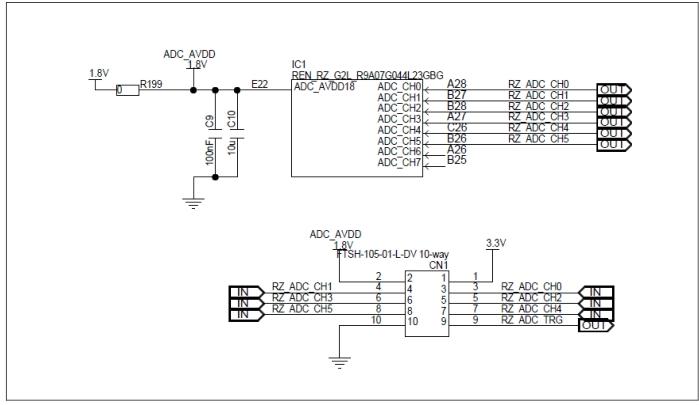

- 方便的调试与数据采集:配备了用于ARM Cortex调试的10引脚引脚头和用于ADC接口的10引脚引脚头。

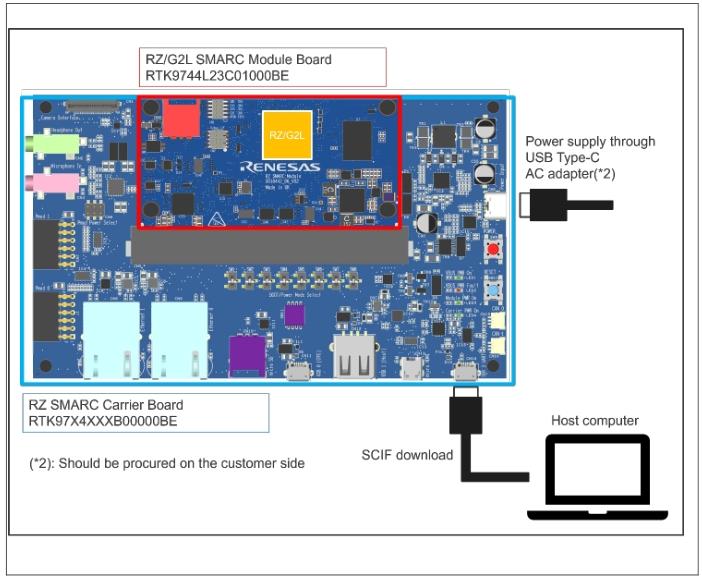

1.2 系统配置示例

1.3 详细特性参数

| 项目 | 详情 |

|---|---|

| CPU | RZ/G2L |

| 输入(Xin)时钟 | 24MHz |

| Arm Cortex - A55时钟 | 1.2GHz |

| Arm Cortex - M33时钟 | 200MHz |

| AXI - 总线时钟 | 200MHz |

| APB - 总线时钟 | 100MHz |

| 内部内存 | 指令缓存:32KB;数据缓存:32KB |

| 电源电压 | 1.1V,VO:3.3V |

| 封装 | 456引脚PBGA 0.5mm间距 |

| 内存 | QSPI闪存:512Mbit 1pc;DDR4 SDRAM:2GB 1pc;eMMC内存:64GB * 1pc |

| 时钟IC | 时钟发生器:1pc |

| 以太网IC | 以太网PHY:2pcs |

| 连接器 | microSD卡插槽(4位):1pc;10引脚JTAG引脚头:1pc;10引脚ADC引脚头:1pc;SMARC边缘连接器(314引脚):1pc |

| 开关 | 系统设置DIP开关:2位 |

| 电路板规格 | 尺寸:82mm * 50mm;安装方式:双面安装(6层) |

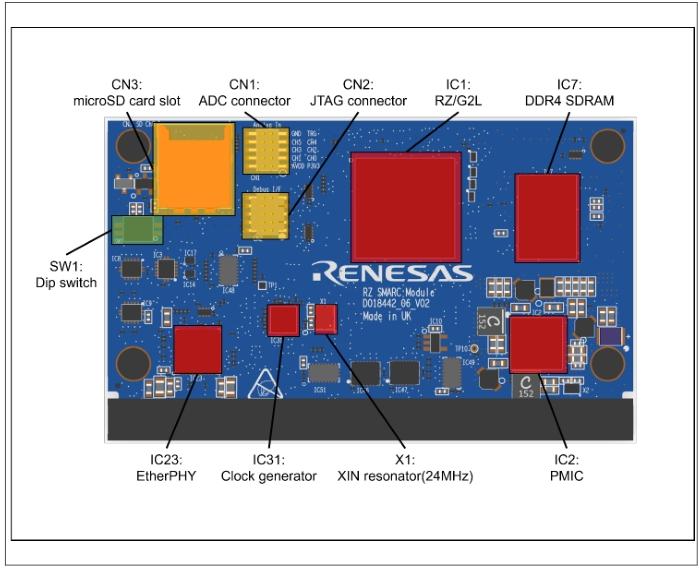

1.4 外观展示

RTK9744L23C01000BE的外观设计紧凑,布局合理。

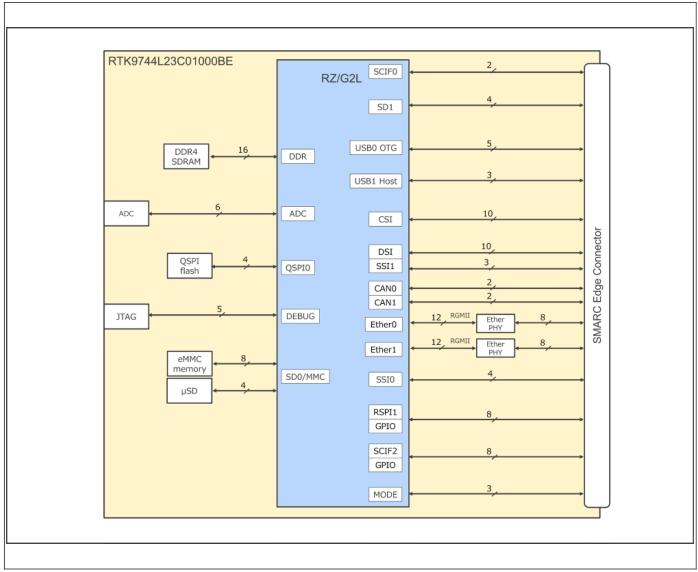

1.5 模块板框图

1.6 布局组件

模块板的主要组件布局清晰,便于安装和维护。

1.7 绝对最大额定值

| 符号 | 项目 | 额定值 | 注意事项 |

|---|---|---|---|

| VDD IN | 电源电压 | 5.25V | 参考:Vss |

| 最大功耗 | 3A | 包括连续RZ SMARC系列载板电流消耗 | |

| Topr | 工作环境温度 | 0℃ 至 50℃ | 避免暴露在冷凝或腐蚀性气体中 |

| Tstg | 存储温度 | -10℃ 至 60°C | 避免暴露在冷凝或腐蚀性气体中 |

1.8 工作条件

| 符号 | 项目 | 额定值 | 注意事项 |

|---|---|---|---|

| VDDIN | 电源电压 | 3.0V 至 5.25V | 参考:Smarc v2.1规范 |

| Topr | 工作环境温度 | 0℃ 至 40℃ | 避免暴露在冷凝或腐蚀性气体中 |

二、功能规格

2.1 功能模块概述

| 章节 | 功能 | 描述 |

|---|---|---|

| 2.2 | MPU | 输入(Xin)时钟:24MHz;Arm Cortex - A55时钟:1.2GHz;Arm Cortex - M33时钟:200MHz;AXI - 总线时钟:200MHz;APB - 总线时钟:100MHz |

| 2.3 | 内存 | QSPI闪存:512Mbit 1pc;DDR4 SDRAM:2GB 1pc |

| 2.4 | 千兆以太网接口 | 通过以太网PHY实现以太网控制器(E - MAC)与LAN连接器之间的连接 |

| 2.5 | ADC接口 | 实现ADC模块与连接器之间的连接 |

| 2.6 | 时钟配置 | 系统时钟配置 |

| 2.7 | 复位控制 | 对RTK9744L23C01000BE上安装的RZ/G2L进行复位控制 |

| 2.8 | 电源供应配置 | RTK9744L23C01000BE和RTK97X4XXXB00000BE的系统电源供应配置 |

| 2.9 | PMIC | 实现RZ/G2L与PMIC之间的连接 |

| 2.10 | 调试接口 | 实现调试接口与连接器之间的连接 |

| 2.11 | SD/MMC主机接口 | 实现SD/MMC主机接口(SDHI)通道0与microSD卡插槽之间的连接 |

2.2 MPU

2.2.1 RZ/G2L概述

RTK9744L23C01000BE搭载了64位微处理器RZ/G2L,其与CPU时钟(最大1.2 GHz)同步运行。

2.2.2 RZ/G2L引脚功能列表

| RZ/G2L的引脚功能丰富多样,涵盖了电源、信号输入输出、通信等多个方面。详细的引脚功能列表如下: | 引脚位置 | 引脚名称 | 引脚功能 | 描述 | SMARC引脚编号 | SMARC引脚名称 |

|---|---|---|---|---|---|---|

| G12 | ABG_ AVDD18 | ABG_AVDD18 | 1.8V,三星自适应体偏置发生器1.8V模拟电源 | |||

| B11 | ABG_NCP_OUT | ABG_NCP_OUT | 通过1uF旁路电容连接到VSS | |||

| …… | …… | …… | …… | …… | …… |

2.3 内存

RTK9744L23C01000BE除了内置的内存外,还配备了QSPI闪存和DDR4 SDRAM作为外部存储。

2.3.1 QSPI闪存

QSPI闪存由RZ/G2L内置的SPI多I/O总线控制器(SPIBSC)控制,支持66 MHz时钟频率下的操作。

2.3.2 DDR4 SDRAM

DDR4 SDRAM由RZ/G2L内置的内存控制器(MEMC)控制,支持16位数据总线宽度和1600Mbps的数据传输速率。

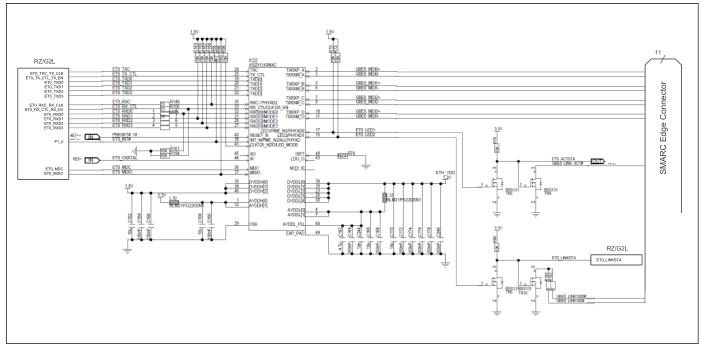

2.4 千兆以太网接口

RTK9744L23C01000BE集成了支持RGMII的以太网PHY,该接口符合IEEE802.3 PHY RGMII和IEEE802.3 PHYMII标准。

2.5 ADC接口

模块板配备了用于连接ADC接口的10引脚引脚头,可使用6个输入通道。

2.6 时钟配置

系统时钟配置合理,MIPI - DSI接口支持高达Full HD、60fps模式的操作,SD接口支持UHS - I模式的50MB/s(SDR50)和104MB/s(SDR104)。

2.7 复位控制

RTK9744L23C01000BE的DDR4 SDRAM、QSPI闪存、eMMC内存、以太网和调试接口由PMIC的复位信号控制。系统复位分为上电复位和按钮开关复位两种类型。 2024-05-06 2567

-

瑞萨RZ/V2L预训练的人工智能模型2024-03-21 1001

-

RZ/G2L、RZ/G2LC和RZ/G2UL的SMARC EVK启动指南Rev.1.012024-02-02 470

-

RZ/G2L、RZ/G2LC 用户手册概述2023-06-30 461

-

【米尔瑞萨RZ/G2L开发板-试用体验】米尔瑞萨RZ/G2L开发板使用SSH登录2023-06-11 7783

-

RZ/G2UL、RZ/A3UL、RZ/Five SMARC 模块板用户手册:硬件2023-01-09 582

-

【飞凌RZ/G2L开发板试用体验】+03.RZ/V2L开发板上电测试(WIFI+交叉编译)(zmj)2022-10-24 2015

-

【飞凌RZ/G2L开发板试用体验】+08.RZ/V2L开发板的QT测试(zmj)2022-09-06 1859

-

【飞凌RZ/G2L开发板试用体验】+01.开箱(zmj)2022-08-28 1451

全部0条评论

快来发表一下你的评论吧 !