石英晶体器件PCB布局建议

描述

在时钟与射频电路设计中,石英晶体及晶体滤波器的PCB布局直接关系到系统的稳定性与性能表现。“铺地还是挖空”应基于器件的电气本质进行判断:

挖空:对于高阻抗、参与起振的关键节点,应优先减少PCB寄生电容的影响;

铺地:对于低阻抗、已在器件内部完成振荡或需要良好电磁屏蔽的器件,应优先保证稳定、连续的接地参考。

在实际产品中,可能会看到同类器件存在不同PCB处理方式,原因如下:

频率和封装不同,对寄生参数的敏感度不同;

驱动电路和系统裕量不同;

厂商应用建议存在差异。

凯擎小妹建议您在工程设计中,应以器件数据手册和应用说明为优先依据,而非简单套用经验结论。

无源晶体:建议挖空

无源晶体本身并不产生振荡,它仅提供高Q值的机械谐振特性。实际的振荡放大器通常集成在MCU或专用时钟芯片内部,因此晶体两端构成了高阻抗起振节点。

在这种结构下,PCB中的寄生电容会直接影响振荡条件,尤其是焊盘正下方的地铜或电源铜皮,可能导致负载电容增大,从而引起频率偏移、起振裕量下降,甚至在极端条件下无法起振。

推荐做法:

晶体焊盘正下方保持挖空;

晶体本体下避免大面积铺地;

在晶体外围设置接地护环,抑制外界干扰;

晶体走线尽量短、对称、避免跨分割。

在部分低频应用或驱动能力较强的系统中,即使未完全挖空,电路仍可能工作。但从频率精度、温漂和批量一致性的角度看,“挖空”仍是更稳妥的选择。

有源晶振:建议铺地

有源晶振在封装内部已集成晶体、振荡、放大和缓冲电路。此时,晶体振荡已经在器件内部完成,PCB上输出的是驱动能力较强的时钟信号,而不再是高阻抗节点。因此,这类器件对PCB寄生电容并不敏感,反而更依赖稳定、低阻抗的地参考。

推荐做法:

器件本体下方铺设连续接地铜皮;

确保地回路短且完整;

电源去耦电容紧贴器件引脚。

对于TCXO、VCXO和OCXO等高稳定度器件,内部包含温补、调谐或恒温控制等模拟模块,地平面的连续性直接关系到相位噪声和频率稳定性,因此行业中通常建议采用完整、连续的接地设计。

KOAN晶振

为了让设计与选型用户在选型时更高效,凯擎小妹在KOAN晶振官网的参数选择页面完善常用频率下拉列表,可快速选择,提高选型效率。如果您的设计需要列表之外的频率,也可以直接输入:

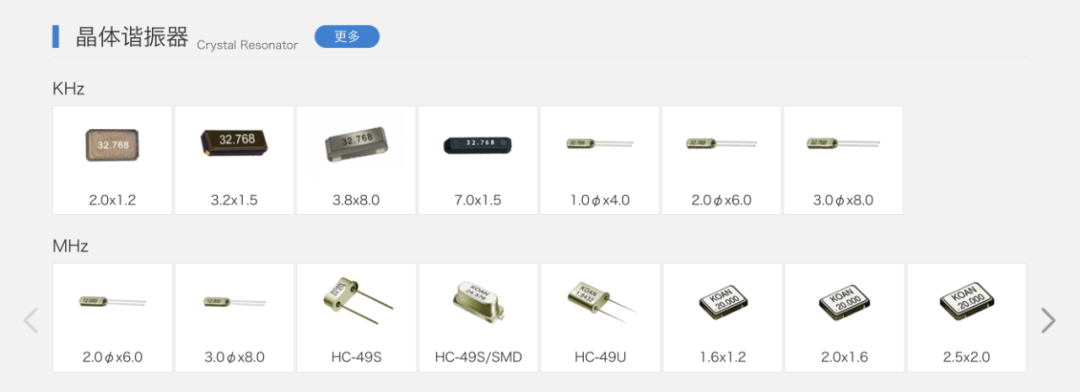

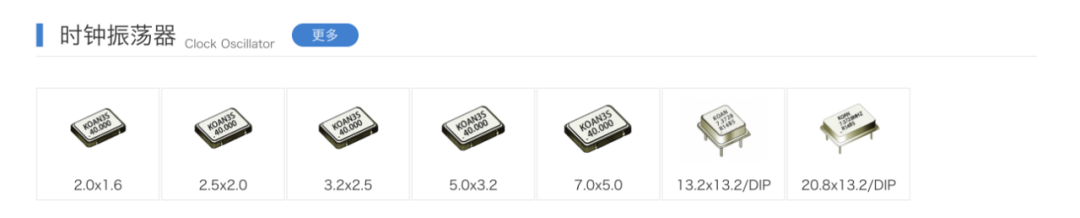

若您需要针对具体应用的晶振选型建议和技术支持,欢迎随时联系我们,KOAN将为您提供专业、贴心的解决方案。我们提供无源晶振和有源晶振,覆盖多种规格尺寸,现货充足,以满足客户需求。我们的产品质量和技术处于行业领先水平。公司致力于精细化质量管理,以满足客户对高端产品的需求。

-

GeneSiC MOSFETs的PCB布局建议2025-01-24 399

-

PW2162的PCB布局设计的建议是什么2021-12-28 1858

-

MT2492的PCB布局设计建议2021-11-17 2048

-

石英晶体好坏怎么判断2021-05-10 2218

-

石英晶体的结构,有哪些基本特性?2021-03-15 3717

-

石英晶体器件怎么分类?2019-10-28 2968

-

石英晶体——电子系统不可或缺器件2019-03-13 3423

-

请问石英晶体振荡器稳频原理是什么?2018-07-13 5058

-

使用石英晶体振荡子的注意事项——设计PCB布局图的要点2016-04-27 2545

-

石英晶体2014-01-15 2044

-

石英晶体的工作原理2013-12-20 3436

-

石英晶体谐振器2010-04-16 2400

-

石英晶体器件概述:从原料到振荡器2008-11-24 694

全部0条评论

快来发表一下你的评论吧 !