适用于高速流水线ADC中基于双采样技术的高性能采样/保持电路设计

描述

1 引言

随着现代电子技术迅猛发展,电子产业逐步形成了以数字为主的格局。数字信号处理 技术日渐成熟的同时, 对模拟信号和数字信号的转换接口电路模数转换器 (Analog-to-Digital Converter 简称ADC)的速度和精度方面的要求也越来越高。ADC 的性能在整个信号处理系统中起到至关重要的作用,成为限制整个系统性能的瓶颈。在整个 ADC 系统中,前级采样保持电路(sample-and-hold circuit 简称S/H)的性能直接影响到 后续电路对采样保持信号处理的正确性,从而影响整个系统的性能,因此对其速度和精度要 求十分严格。S/H 电路的精度很大程度上取决于运放的增益,S/H 电路的带宽则取决于运放 的带宽,所以设计一个相对高增益、高带宽的运放是整个ADC 设计的关键,本文采用的是增 益自举运放结构,可以在增益和带宽方面得到较好的效果。此外,随着采样的速度和精度的 不断提高,简单的CMOS 开关已经不能满足设计的需要,本文采用了栅压自举开关[2],可以 得到较好的采样精度和线性度。针对运放的增益误差和开关电路误差所引起S/H 电路速度受 限的问题,在整个S/H 电路结构方面采用了双采样技术[3],使同一周期内的采样保持工作由 原来的一次变为两次,整个S/H 电路的速度得到极大的提高。

2 运放的设计

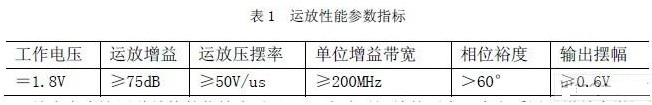

运放是S/H 电路中的核心模块。CMOS 的运放主要包括四种常见结构:简单两级运算放大器、套筒式的共源共栅放大器、折叠式共源共栅放大器、增益自举运算放大器[4,5]。比较 四种结构的性能发现,套筒式共源共栅在速度、功耗和噪声方面具有优势,但是它的增益和 输出摆幅有限,不适用于采样增益电路中。折叠式共源共栅的速度较高,但其他四个性能参 数一般,也不采用。两级运放最大的缺点是速度提升较为困难。增益自举运放在增益、带宽、 速度等方面表现较好。根据S/H 电路的设计要求,对运放的各参数的性能指标为:

综合考虑这四种结构的优缺点以及S/H 电路对运放的要求,本文采用了增益自举运放来作为S/H 电路中的核心模块。

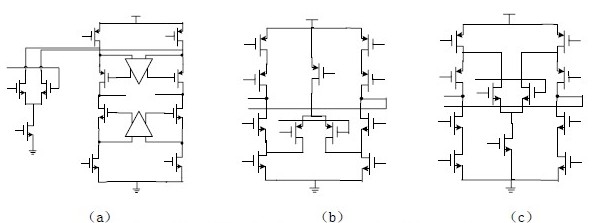

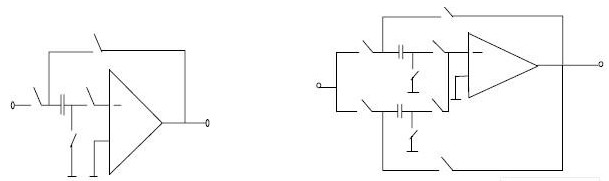

增益自举运放在增益和带宽方面都具有明显的优势,基本的增益自举运放为一个主运 放内连接四个辅运放构成,这种结构在功耗和面积方面没有优势。本文设计的增益自举运放 只采用三个运放构成,主运放采用全差分折叠共源共栅结构,考虑到匹配问题,两个辅运放 也采用全差分折叠共源共栅结构设计。辅运放单位增益频率的选择根据经验[7]单位增益带 宽应大于主运放的-3dB 带宽,这样主运放就能保持原有的的高频特性。具体电路布局如下 图:

对运放采用SMIC0.18um 工艺库进行仿真,得到仿真结果如下:

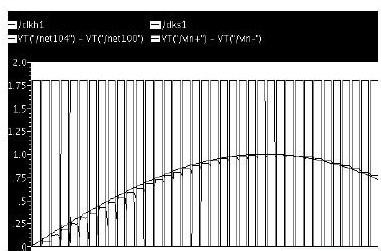

仿真波形如下图所示:

3、栅压自举开关设计

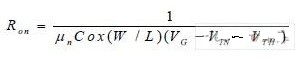

在流水线结构中,采样模式的开关等效为一个阻抗为 Ron 的电阻,忽略体衬偏效应的影响,Ron 的值为:

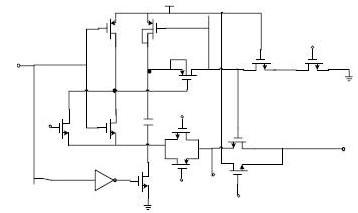

影响开关主要性能的因素包括:开关导通阻抗的非线性、开关电荷注入效应以及时钟 馈通效应等。开关导通阻抗的非线性主要影响着无杂散动态范围(spurious free dynamic range,SFDR);电荷注入效应给电路引入了非线性;时钟馈通效应带来了一个与输入电压 无关的固定失调。针对这些问题,设计选用了带时钟馈通补偿结构的栅压自举开关。

当时钟 CLK 为高电平时,开关处于采样状态,当CLK 为低电平时,开关处于保持状 态。MS 为栅压自举开关中的开关管,DS 为引入的虚拟开关,其作用是在时钟由高变低的 时刻在输出端产生一个补偿电压,用于补偿时钟馈通效应带来的影响。在开关电路中,电容 两端电压虽然在保持阶段能够被充到电源电压值,但在采样阶段由于寄生电容的影响,使得 电容两端电压值产生变化,这将给开关电路带来非线性。因此在设计时,对电容值的选取要 求较高。

4、双采样技术采样保持电路

采样保持电路是流水线 ADC 中至关重要的部分。特别是前端采样保持电路,它将直接 影响到后续电路对采样保持信号处理的正确性,从而影响整个系统的性能。基本采样保持电 路由开关和电容组成,电容翻转结构的采样保持电路,在采样时刻,电容C 采集输入信号 量,在保持时刻电容C 输出电压为采样时刻电压,从而实现采样保持。电容翻转结构在功 耗与噪声较低,适用于该流水线结构ADC 的设计。

通过研究电路的时序发现,基本的采样保持结构在采样周期,保持电路处于空闲,在 保持周期,采样电路处于空闲,一个时钟周期内电路只能对输入信号进行一次处理。双采样 结构的采样保持电路对电容翻转结构进行扩展,利用两个采样电容交替工作。在时钟信号为高电平时刻,电容 C1 进行采样,输出端保持电容C2 的采样信号;时钟信号为低电平时刻, 电容C2 进行采样,输出端保持电容C1 的采样信号。在一个时钟周期内两个电容如此交替工 作,完成两次采样保持过程。

整体采样保持电路采用SMIC0.18um 工艺,利用spectre 进行仿真。输出的仿真结果为, 电路工作电压1.8V,输入信号频率为800KHZ,采样频率为50MHZ。满足流水线ADC 系统中 对采样保持电路的设计要求,下图为双采样技术的采样保持电路仿真波形图。

5、结束语

本文设计了一种采用双采样技术、全差分增益自举运放和栅压自举开关的采样保持电 路。采用增益自举运放达到较好的增益和带宽性能指标;采用栅压自举开关克服了开关导通 阻抗的非线性、开关电荷注入效应以及时钟馈通效应等不良影响;双采样电路的使用使得采 样速率达到同等结构单采样速率的两倍。通过对这几种结构进行分析设计,最终得到的采样 保持电路能够满足10bits50MS/s 的流水线ADC 的应用。整个电路设计基于SMIC0.18um 工 艺,仿真结果表明,该采样保持电路达到设计要求,能够满足中高精度高速流水线ADC 的 应用。

-

适用于多标准收发器中的可重构流水线ADC的应用设计2020-08-05 1096

-

流水线ADC结构解析 流水线ADC和其它ADC的比较2023-09-26 2522

-

一种用于高速ADC的采样保持电源电路的设计2018-10-08 1798

-

如何设计一个适用于12bit流水线ADC采样保持电路?2021-04-20 2707

-

求一种高性能低功耗流水线ADC设计方法2021-04-22 1635

-

适用于流水线ADC的高性能采样保持电路2009-12-26 912

-

流水线技术在高速数字电路设计中的应用2010-07-17 894

-

流水线ADC2009-02-08 10407

-

适用于12 bit流水线ADC采样保持电路的设计2010-06-07 3395

-

13bit 40MS/s流水线ADC中的采样保持电路设计2012-09-25 8489

-

高速ADC的采样保持电源电路的设计方案解析2017-11-16 1412

-

用于高速ADC的采样保持电源电路的设计方案解析2017-12-07 1301

-

高性能低功耗的采样保持电路的设计与实现2019-06-13 7163

-

CEA技术的原理特点及在流水线ADC中的应用2019-05-17 4666

-

了解流水线型ADC2023-02-25 6876

全部0条评论

快来发表一下你的评论吧 !