英伟达GPU直流供电架构与基本半导体SiC MOSFET在AI服务器PSU中的应用价值分析

电子说

描述

英伟达GPU直流供电架构与基本半导体SiC MOSFET在AI服务器PSU中的应用价值分析

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

生成式人工智能(Generative AI)的爆发式增长正在重塑全球数据中心的物理基础设施,其中最为显著的变革发生在高功率密度计算单元的供电网络(Power Delivery Network, PDN)中。随着大语言模型(LLM)参数量向万亿级别迈进,算力基础设施的核心——GPU加速器,其单体功耗与集群功率密度正经历着前所未有的跃升。NVIDIA作为AI算力的领军者,其Hopper架构(H100)及最新的Blackwell架构(B200/GB200)不仅重新定义了计算性能的边界,更迫使数据中心供电架构从传统的12V交流配电体系向高压直流(48V/54V)母线架构发生根本性迁移。

倾佳电子全面剖析NVIDIA高性能GPU架构下的直流供电系统演进逻辑,并深入探讨碳化硅(SiC)金属氧化物半导体场效应晶体管(MOSFET)在此类高密度电源供应单元(PSU)中的关键应用价值。倾佳电子特别聚焦于基本半导体(BASiC Semiconductor)的SiC技术路线与产品组合——包括B3M010C075Z、B3M025065B(TOLT封装)及AB3M025065CQ等核心器件——如何通过卓越的开关特性、热管理能力及宇宙射线耐受性,解决5.5kW至8kW AI服务器电源面临的效率与密度双重挑战。分析表明,在OCP ORv3标准下,SiC MOSFET已不再是可选项,而是实现97.5%以上钛金级/红宝石级效率以及大于100W/in³功率密度的必要使能技术。

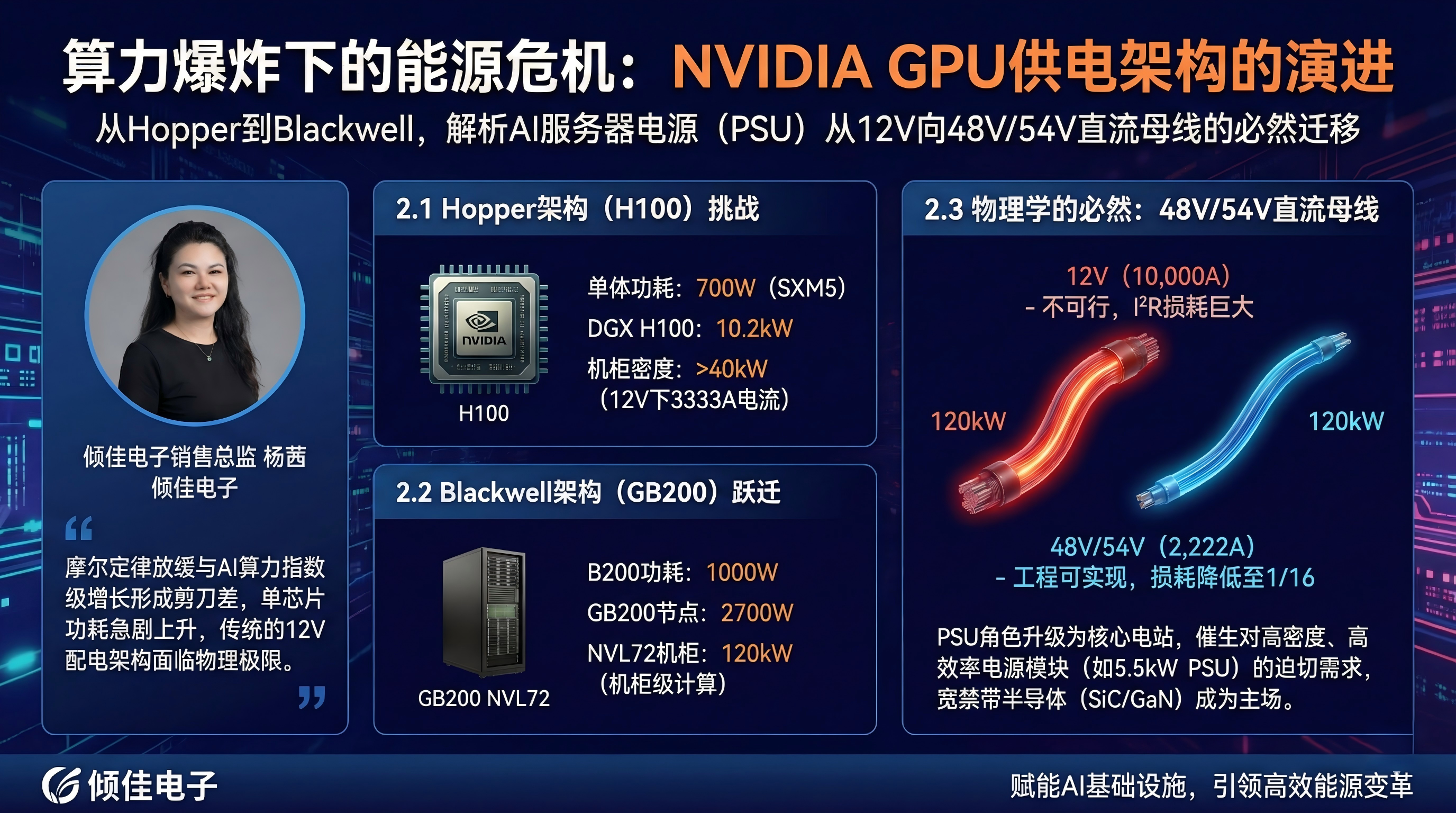

2. 算力爆炸下的能源危机:NVIDIA GPU供电架构的演进

要理解AI服务器电源(AI Server PSU)的技术变革,必须首先从负载端——即GPU及其互联架构的功耗特性出发。摩尔定律的放缓与AI算力需求的指数级增长(每3.5个月翻一番)形成剪刀差,导致单芯片功耗急剧上升。

2.1 Hopper架构:H100开启的700W时代与供电瓶颈

NVIDIA H100 GPU基于Hopper架构,采用台积电4N工艺制造,集成了800亿个晶体管。作为上一代A100的继任者,H100在性能提升的同时,其热设计功耗(TDP)也攀升至新的高度。

单体功耗极限: SXM5版H100的TDP达到700W,部分配置甚至更高 。相比之下,传统CPU服务器的单路功耗通常在200W-350W区间。

集群功率密度: 一个标准的NVIDIA DGX H100系统包含8颗H100 GPU、2颗Intel Xeon Platinum CPU、4个NVSwitch以及高速网卡。单台服务器的峰值功耗设计高达10.2 kW 。

机柜级挑战: 在传统风冷数据中心,一个标准机柜通常仅能支持10-15 kW的功率密度。然而,部署4台DGX H100服务器的机柜功率密度瞬间突破40 kW 。这种密度使得传统的12V配电架构面临巨大的I2R损耗挑战。在12V母线下,40kW意味着高达3333A的电流,铜排的截面积需求和传输损耗将变得不可接受。

2.2 Blackwell架构:GB200 NVL72与机柜级计算的千瓦级跃迁

Blackwell架构的推出标志着AI计算从“芯片级”向“机柜级”的彻底转变。GB200 NVL72并非简单的服务器堆叠,而是一个通过NVLink全互联的巨型计算单元。

B200 GPU功耗: 单颗B200 GPU的TDP突破1000W大关,相比H100提升了约43% 2。

GB200超级芯片: 将两颗B200 GPU与一颗Grace CPU封装在一起,单节点的TDP高达2700W 。

NVL72机柜功率风暴: 一个GB200 NVL72机柜集成了72颗Blackwell GPU和36颗Grace CPU。加上NVLink Switch系统,整个机柜的功耗达到了惊人的120 kW 。

2.3 物理学的必然:从12V到48V/54V直流母线的迁移

面对120 kW的机柜功率,维持传统的12V配电架构在物理上已不再可行。根据焦耳定律,传输损耗与电流的平方成正比。将配电电压从12V提升至48V(或54V),电流可降低至原来的1/4,而线路损耗理论上可降低至原来的1/16。

电流对比分析:

120 kW @ 12V: 需传输 10,000 A 电流。这需要如同手臂般粗细的铜母排,且连接器接触电阻会导致严重的发热和压降。

120 kW @ 54V: 电流降至约 2,222 A。虽然依然巨大,但通过分段母排(Busbar)和分布式电源架(Power Shelf)的设计,已处于工程可实现的范围内 10。

这一转变确立了48V/54V直流母线作为AI数据中心的核心骨干网。电源供应单元(PSU)的角色从为主板供电的组件,升级为向机柜直流母线输能的核心电站。这一架构变迁直接催生了对高密度、高效率电源模块(如5.5 kW PSU)的迫切需求,而这正是宽禁带半导体(SiC/GaN)的绝对主场。

3. OCP ORv3标准下的AI服务器电源架构解析

为了应对AI负载的特殊需求,开放计算项目(OCP)推出了Open Rack Version 3 (ORv3) High Power Rack (HPR) 规范,这也成为了NVIDIA及其合作伙伴(如Delta、LiteOn、MPS等)设计电源系统的基准。

3.1 ORv3电源架(Power Shelf)的设计哲学

在ORv3架构中,电源不再内置于服务器机箱内,而是集中在机柜中部的电源架(Power Shelf)上。

容量配置: 一个标准的ORv3电源架高度通常为1OU或2OU,可容纳6个电源模块(PSU)。

功率等级: 随着GPU功耗的提升,电源架的总功率已从早期的18 kW(6x 3kW)升级至33 kW(6x 5.5kW)甚至更高 。

冗余架构: GB200 NVL72机柜通常配备6到8个电源架,通过并联为直流母线供电,形成N+N或N+1的冗余池,总供电能力设计需覆盖132 kW至192 kW的峰值负载 。

3.2 核心组件:5.5 kW PSU的技术指标

作为电源架的基本构建单元,5.5 kW PSU的性能指标极为苛刻,代表了当前电力电子工业的最高水平。

功率密度: 必须在极为有限的体积内输出5.5 kW。这意味着功率密度必须达到100 W/in³以上 。传统的硅基方案在风冷条件下几乎无法达到这一指标。

效率曲线: 必须满足**80 Plus Titanium(钛金级)**甚至更高的效率标准。

50%负载效率:> 97.5%

100%负载效率:> 96.5%

10%轻载效率:> 94% 。

动态响应: AI训练任务具有极端的负载瞬变特性(Load Transient)。GPU在启动训练批次瞬间,电流需求可能在微秒级内从空闲跳变至峰值。PSU必须具备极快的环路响应速度,以维持54V母线的电压稳定 。

3.3 拓扑结构的必然选择:图腾柱PFC与LLC

为了实现上述指标,传统的升压PFC+二极管整流桥方案已被彻底淘汰。行业普遍收敛于以下拓扑组合:

PFC级(功率因数校正): 采用无桥图腾柱(Bridgeless Totem-Pole)PFC拓扑,工作在连续导通模式(CCM)。

优势: 省去了整流桥的导通损耗,效率理论极限最高。

挑战: “快桥臂”必须进行硬开关操作。传统硅MOSFET体二极管的反向恢复电荷(Qrr)过大,会导致巨大的反向恢复损耗甚至器件损坏。因此,SiC MOSFET或GaN HEMT是实现CCM图腾柱PFC的唯一选择 17。

DC-DC级: 采用LLC谐振变换器。

优势: 可实现原边零电压开通(ZVS)和副边零电流关断(ZCS),最大限度降低开关损耗。

挑战: 为了减小磁性元件体积以提升密度,开关频率需推高至200kHz-500kHz甚至更高。SiC MOSFET凭借低开关损耗和稳定的高温RDS(on),成为原边开关的首选 。

4. 碳化硅(SiC)MOSFET在AI PSU中的核心应用价值

在5.5 kW AI服务器电源的设计中,SiC MOSFET并非简单的硅器件替代品,而是实现高密度与高效率的物理基础。

4.1 物理特性的降维打击

SiC材料的宽禁带特性赋予了MOSFET远超硅基器件的性能边界:

极低的反向恢复电荷(Qrr): SiC MOSFET体二极管的Qrr仅为同规格硅超结MOSFET的1/10甚至更低。这使得在图腾柱PFC的硬开关过程中,反向恢复损耗几乎可以忽略不计,直接使能了99%以上的PFC级效率 。

高温下的导通电阻稳定性: 硅MOSFET在150°C时,其导通电阻(RDS(on))通常会增加到室温值的2.5倍以上。而SiC MOSFET仅增加约1.3-1.5倍。在AI服务器长期满载运行的高温环境下,这意味着SiC的热损耗远低于硅,从而减轻了散热系统的负担 。

高热导率: SiC的热导率(4.9 W/cm·K)是硅(1.5 W/cm·K)的3倍以上。这使得SiC芯片能够更有效地将热量传导至封装外壳,允许更小的芯片面积承受更大的电流密度 。

4.2 电压等级的战略选择:750V vs. 650V

在AI数据中心电源设计中,一个显著的趋势是从标准的650V器件转向750V器件。这一转变并非为了应对更高的输入电压,而是为了应对**宇宙射线(Cosmic Ray)**引起的单粒子烧毁(SEB)风险。

背景: 现代数据中心母线电压通常在400V左右(PFC输出)。对于650V器件,400V的工作电压占其额定值的61%。

风险: 在海量部署(数万台服务器)和高海拔数据中心场景下,宇宙射线诱发的失效概率(FIT率)与器件承受的电压应力呈指数关系。

解决方案: 采用750V SiC MOSFET,在400V母线下工作时,电压应力降至53%。这额外的100V裕量可以将宇宙射线诱发的失效率降低数个数量级,满足AI超算集群对“零停机”的高可靠性要求 25。

基本半导体的布局: 基本半导体推出的B3M010C075Z(750V, 10mΩ)正是精准对标这一关键需求的战略产品 。

4.3 封装技术的革新:顶部散热(Top-Side Cooling)

为了达到100 W/in³的功率密度,传统的PCB底部散热方式已触及天花板。

传统瓶颈: 传统SMD封装(如TO-263)热量通过PCB散发。PCB既是电气互连载体又是散热通道,导致热设计与电气布线相互掣肘。

TOLT/QDPAK解决方案: 顶部散热封装(如基本半导体的TOLT和QDPAK)将漏极金属裸露在封装顶部。

优势:

热电分离: 热量直接通过顶部散热器导出,不经过PCB,极大降低了热阻。

空间利用: PCB底部不再需要大面积铺铜散热,可用于布置驱动电路或无源元件,显著提升空间利用率。

系统风道优化: 配合散热器设计,可以直接利用服务器风扇的高风速气流进行冷却 。

5. 基本半导体(BASiC Semiconductor)SiC产品在AI PSU中的深度应用分析

基本半导体作为中国SiC功率器件的领军企业,其产品线布局与AI服务器电源的技术演进路径高度契合。以下结合提供的技术文档,深入分析其核心产品在5.5 kW PSU中的具体应用场景。

5.1 B3M010C075Z:PFC慢桥与高可靠性的基石

规格概要: 750V, 10 mΩ, 240A (25∘C), TO-247-4封装 。

应用场景分析:

图腾柱PFC慢桥(工频臂): 尽管慢桥开关频率低(50/60Hz),但承载电流极大。B3M010C075Z极低的10 mΩ导通电阻能最大程度降低导通损耗,提升整机效率。

交错并联PFC主开关: 在大功率交错PFC中,其强大的电流能力(240A)提供了充足的裕量。

可靠性护城河: 750V的耐压设计是其核心竞争力,能够有效抵御电网浪涌和宇宙射线威胁,特别适合对可靠性要求极高的金融与AI训练数据中心。

开尔文源极(Kelvin Source): TO-247-4封装引入的开尔文源极引脚有效解耦了栅极驱动回路与功率回路的共源极电感干扰,这对于在大电流下保持快速且干净的开关波形至关重要,能够显著降低Eon和Eoff损耗 。

5.2 B3M025065B:高密度PFC快桥的利器(TOLT封装)

规格概要: 650V, 25 mΩ, 108A, TOLT封装 。

应用场景分析:

图腾柱PFC快桥(高频臂): 这是PSU中开关损耗最大的部分。B3M025065B不仅具有25 mΩ的低导通电阻,更关键的是其TOLT封装。

TOLT的热学价值: 在5.5 kW PSU极其紧凑的空间内(通常仅为1U高度),散热是最大挑战。TOLT允许散热器直接压在器件顶部,热阻Rth(jc)低至0.40 K/W 30。这种设计允许PSU内部采用“三明治”堆叠结构,极大提升功率密度。

寄生参数优化: 无引脚的TOLT封装具有极低的寄生电感,非常适合工作在100kHz以上的硬开关频率,减少电压过冲和振铃 。

5.3 AB3M025065CQ:车规级品质降维打击工业市场

规格概要: 650V, 25 mΩ, QDPAK封装, AEC-Q101认证。

应用场景分析:

虽然标注为车规级,但在高端服务器电源领域,“车规级”代表着更严苛的环境耐受力(如温度循环、高湿偏压)。

5.4 竞品对比与市场定位

与Infineon的CoolSiC G2系列相比,基本半导体的策略在于:

电压等级差异化: 通过B3M010C075Z的750V规格,直接对标Infineon的750V产品线,切中400V直流母线的高可靠性痛点。

封装创新跟进: 迅速推出TOLT产品(B3M025065B)QDPAK封装产品(AB3M025065CQ),与Infineon的QDPAK在顶部散热赛道保持同步,显示了其对高密度电源趋势的敏锐洞察。

性价比与供应链安全: 在全球半导体供应链波动的背景下,作为本土供应商,BASiC能为以AI服务器电源大厂提供更灵活的支持和供应链安全保障。

6. 5.5 kW AI服务器电源系统级设计建议

基于上述分析,构建一个符合OCP ORv3标准的5.5 kW AI服务器PSU,推荐采用以下SiC器件配置方案:

| 拓扑级 | 功能描述 | 关键技术要求 | 推荐基本半导体型号 | 选型理由 |

|---|---|---|---|---|

| PFC快桥 | 高频整流与升压 | 低开关损耗,高频能力,顶部散热 | B3M025065B | TOLT封装解决高密度散热瓶颈;25mΩ平衡导通与开关损耗。 |

| PFC慢桥 | 工频换向 | 极低导通损耗,抗浪涌,高可靠性 | B3M010C075Z | 750V耐压提供宇宙射线防护裕量;10mΩ实现极致效率。 |

| LLC原边 | 谐振变换 | ZVS软开关,热稳定性 | B3M040065B (TOLT) | 40mΩ成本更优;TOLT封装保持整体散热设计的一致性。 |

| LLC副边 | 同步整流 | 低电压大电流 | (建议采用低压Si MOSFET) | 此处通常使用80V/100V硅基器件。 |

设计洞察:

在PFC级,建议采用交错并联(Interleaved)图腾柱结构。使用两路B3M025065B交错工作,可以将单管电流应力减半,并倍增等效开关频率,从而显著减小PFC电感体积,这是实现100 W/in³功率密度的关键系统级策略 35。

7. 结论与展望

NVIDIA GB200 NVL72的出现不仅仅是算力的升级,更是对数据中心能源架构的一次暴力重构。从12V到48V的母线迁移,以及单机柜120 kW的功率需求,使得传统的硅基电源技术彻底失效。

在此背景下,碳化硅MOSFET的应用价值被无限放大:

使能拓扑革命: SiC是实现图腾柱PFC CCM模式的物理前提,直接决定了PSU能否达到97.5%的钛金级效率。

解热密度难题: 顶部散热TOLT或者QDPAK封装的SiC器件将热管理从二维平面释放到三维空间,是实现高功率密度的机械基础。

构筑安全防线: 750V耐压规格为400V直流母线提供了抵御宇宙射线失效的关键屏障,保障了单体价值数百万美元的AI机柜的运行安全。

基本半导体通过精准布局750V高压器件和TOLT先进封装,已具备了在下一代AI服务器电源市场中与国际巨头同台竞技的技术实力。对于电源设计工程师而言,采用这些先进的SiC器件不仅仅是提升效率的手段,更是通向AI算力时代的入场券。

审核编辑 黄宇

- 相关推荐

- 热点推荐

- gpu

- 英伟达

- SiC MOSFET

- AI服务器

-

AI服务器机架供电架构解析:PSU、BBU 与 CBU 的设计逻辑及关键芯片方案2026-03-27 431

-

高压革命:英伟达800V平台架构与SiC MOSFET的商业技术共生2026-02-17 5771

-

英伟达GPU算力直流供电架构变革与SiC MOSFET在800V至57V转换中的关键应用价值2026-01-05 764

-

SiC MOSFET模块在英伟达800V HVDC电源系统中的技术优势与应用价值2025-05-23 1590

-

大功率AI服务器PSU的革新之路2025-03-10 2444

-

GPU服务器AI网络架构设计2024-11-05 2636

-

英伟达AI服务器将革新采用插槽式设计2024-09-27 1291

-

ai服务器是什么架构类型2024-07-02 3747

-

英伟达新业务动向:AI服务器市场的新变局2024-06-21 2101

-

喜讯 | MDD辰达半导体荣获蓝点奖“最具投资价值奖”2024-05-30 1284

-

进一步解读英伟达 Blackwell 架构、NVlink及GB200 超级芯片2024-05-13 6648

-

英伟达首次向OpenAI供应AI服务器,鸿海出货预期将增长2024-04-26 1839

-

英伟达DPU的过“芯”之处2022-03-29 5897

-

英伟达发布新一代 GPU 架构图灵和 GPU 系列 Quadro RTX2018-08-15 4307

全部0条评论

快来发表一下你的评论吧 !