使用FPGA器件和无线收发模块实现编解码应用设计

描述

前言

随着电子技术的飞速发展 ,计算机应用的普及,计算机与计算机,计算机与数据终端,以及数据终端与数据终端之间的数据传输与通信的应用也日益广泛。从工业控制,军事应用,到医疗仪器,家用电器,到处都涉及到数据通信和数据传输的技术。目前这些数据传输主要有无线和有线这两种方式。有线方式由于它的传统性而在现代的数据传输领域占据着主要地位。而无线方式的出现弥补了有线传输的部分缺陷,如线路的成本等。FPGA(FieldProgrammable Gate Array现场可编程门阵列)是一种高密度的可编程逻辑器件,其编程灵活,可在系统编程中通过写入不同的配置数据即可实现不同的逻辑功能。基于 FPGA设计的产品集成度高、体积小、功耗低、开发周期短,现在很多应用产品都是基于 FPGA的开发。对于应用系统而言,只要拿出 FPAG其中的一部分区域完成特定的专项工作,并不影响其他部分的工作,模块之间具有相互独立性。

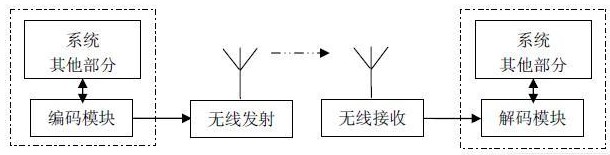

1 系统结构

系统分为接收和发射两部分,使用非编码的无线发射模块和接收模块进行无线数据的传输,发送和接收部分各自具有独立的逻辑模块进行编码或解码,可以和系统其他部分进行数据交互,如图 1。

2.5数据接收过程

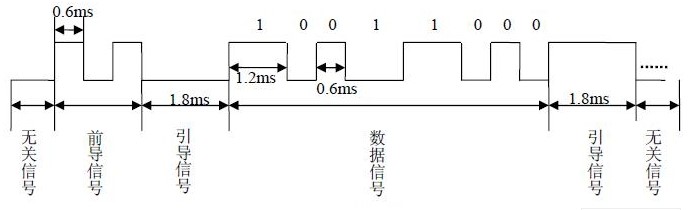

根据发送脉冲宽度,很容易判断信号高低电平,接收采用检测电平时间的方法来判断0、1数据,过程如下:

①接收到输入信号变化,重置计数器计数以判断前导信号,这里时间判断需要有个裕度,本来是 0.6ms的信号,判断在 0.3ms—0.9ms是正确的,其他的丢弃处理,如果是有两个以上的前导信号就进入引导信号的判断;

②判断引导信号是不是1.8ms,此处裕度判断为1.5ms--2.1ms;如果此信号正确,进入数据接收,否则返回空闲态;

③数据接收:数据‘0’判断 0.3ms—0.9ms是正确的,数据‘1’ 判断 0.9ms—1.5ms 是正确的,并将判断所得数据暂放临时变量对应的位空间,过程中如果出现错误则作丢弃整个数据处理,返回空闲态;

④数据接收完成后,接收引导信号,该信号如果判断为 1.8ms即以 1.5ms--2.1ms为准则,则完成数据的接收,将暂存数据输出,否则,整个数据丢弃处理,返回空闲态。

3 实例仿真

非编码无线模块硬件连接只需要电源、地、信号(发射模块对应输出,接收模块对应输入)三根线的电气连接,使用非常方便。其中要注意的问题就是电源的滤波,因为无线模块极易受到干扰,也容易干扰外界,所以对模块的供电要经过一定的处理,一般的方法是通过LC网络(电感电容网络)对系统电源进行滤波后再对无线模块供电。试验表明滤波电路的有无对数据传输的可靠性有比较大的影响。

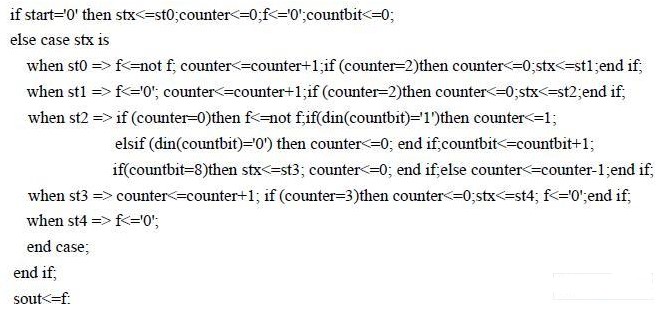

对 FPGA的程序可以使用 VHDL语言,Verilog语言,AHDL语言以及图形等方法进行设计,而在用 VHDL语言的设计中,有限状态机的使用使设计控制的灵活性和高速运算性能大大提高,而且程序的结构清晰明了。

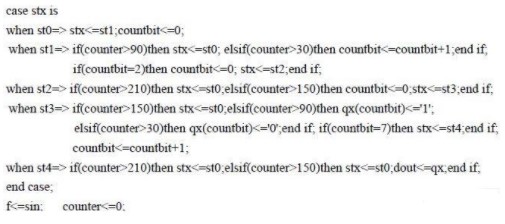

根据无线模块的编码原则与算法,使用 VHDL语言实现状态机,完成无线发射模块数据编码发送的主体程序如下:

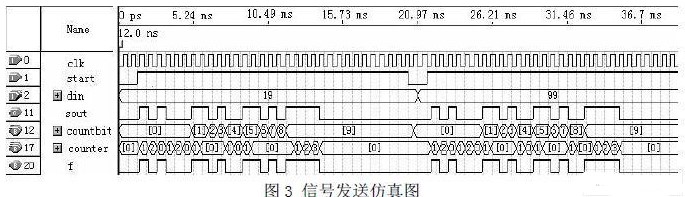

图 3为数据编码发送时序仿真图形,所发送的数据为十六进制的 19H和99H。

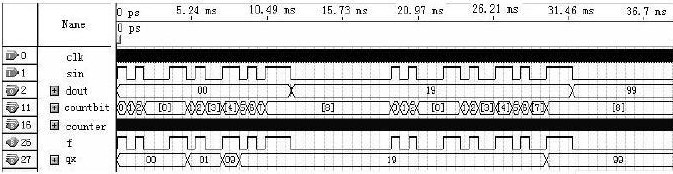

根据无线模块数据接收的解码方法,使用 VHDL语言实现状态机,完成无线接收模块数据解码的主体程序如下:

图 4为数据接收解码时序仿真图形,接收数据为十六进制的 19H和99H。如果在接收数据人为加入干扰,这种方式可以有效地将干扰滤除。

4结论

实验表明,数据可以通过无线模块使用此编解码方式进行正确传输,减少了零电平干扰的影响,而且,此种编解码方法实现灵活简单,占用资源少,具有独立性,电路简洁。设计是 8位数据的编码发送与接收的系统模块,也适合于单片机等 8位处理器接口,当然这种设计可以很方便的扩展为 16位或32位等,并增加校验位,提高数据的吞吐速度以及数据传输的可靠性,也可以增加地址的编码,实现单一的点对点通信。

-

密勒调制副载波编解码器的FPGA实现2023-10-26 563

-

RF433和RF315无线模块的软件编解码遥控程序免费下载2020-12-25 2946

-

如何使用UHF RFID读写器编解码模块实现FPGA2020-07-28 980

-

一种基于FPGA的UHF RFID读写器编解码模块设计2019-07-26 1831

-

单片机实现无线通信中数据的编解码2017-08-31 1201

-

一种高速卷积编解码器的FPGA实现2017-02-07 970

-

基于FPGA的JPEG实时图像编解码系统2016-08-29 723

-

RS编解码的FPGA实现-说明2016-05-04 829

-

13曼彻斯特码编解码的FPGA设计与实现-92016-04-26 712

-

G.7xx语音编解码模块及在AD218X上的实现2016-04-14 595

-

音频编解码芯片接口的FPGA应用2011-09-15 12319

-

基于FPGA的8B/10B编解码设计2011-05-26 4439

-

基于FPGA的非编码无线模块的应用设计2009-12-18 576

-

FPGA进行视频编解码2009-02-06 5363

全部0条评论

快来发表一下你的评论吧 !