采用FPGA芯片完成基于LMS算法的自适应谱线增强系统的设计

描述

在信号采集与处理中,常只关心具有较窄带宽和较强周期特征的信号,这时宽带噪声成为必须滤除的有害成分。信号的频谱携带着信源最本质的特征,但是实际采集的信号不可避免地受到宽带噪声或宽带干扰的影响,如何快速、高效地消除这些噪声和干扰,增强目标谱线在信号处理领域具有重要的意义。ALE利用窄带信号的周期性和宽带噪声的弱相关性,能够在信号特征未知的条件下自适应地将信号从噪声中提取出来,广泛应用于目标识别和特征提取中。FPGA因具有高度的设计灵活性、高速的数据处理能力、丰富的片内资源而在数字信号处理领域占用重要的地位。在此利用FPGA作为数字信号处理的核心部分。流水线结构和分布式算法即是充分利用FPGA高速处理能力,实现复杂数字信号处理算法的有效途径。ALE核心部分构造了利用LMS(Least Mean Square LMS)算法实现自适应谱线增强以及硬件实现的FPGA流水线结构。

1自适应滤波原理

自适应滤波是相对固定滤波器而言的.固定滤波器滤波频率是固定的,自适应滤波器滤波的频率自动适应输入信号而变化的,所以其适用范围更加广泛。自适应滤波器是满足某种准则的最佳滤波器,这种滤波器能够在不需要任何关于信号和噪声先验统计知识的情况下,自动地根据输入信号的变化更新自身的权系数,来满足最佳滤波的需要。自适应滤波器不仅能够处理平稳随机信号而且能处理非平稳随机信号。这些特点使得自适应滤波器在干扰消除、预测、反演、辨识等信号处理领域得到广泛应用。

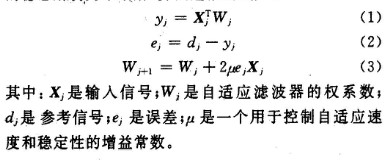

自适应滤波原理包含两方面的内容:一是调整滤波器系数的自适应算法,二是滤波器结构。自适应滤波算法是设定某种准则,使滤波后的输出信号与参考信号的差在此准则下最小。维纳准则广泛应用于自适应滤波,它的解为维纳解。滤波器结构是具体实现自适应算法的途径,寻求高效的滤波器结构一直是自适应滤波的研究重点。FIR横向结构是最常见的滤波器结构。为横向结构滤波器设计硬件的流水线是在FPGA中实现高速自适应滤波的有效途径,因此该设计中采用流水线实现ALE的自适应滤波器。自适应滤波器原理如图1所示。其中,x(n)为输入信号,y(n)为输出信号,d(n)为参考信号,e(n)为误差信号。

LMS算法是一种易于实现、性能稳健、应用广泛的算法。它采用负误差能量梯度更新滤波器的权系数,它的稳态解仍为维纳解,算法递推公式如下:

其中:Xj是输入信号;Wj是自适应滤波器的权系数;dj是参考信号;ej是误差;μ是一个用于控制自适应速度和稳定性的增益常数。

2 ALE原理及其Matlab仿真

2.1 ALE原理

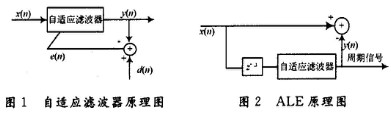

ALE属于自适应滤波的范畴,但是在谱线增强的自适应滤波器设计中,没有外部参考信号可以利用。此时,利用窄带信号周期性明显而宽带噪声周期性差,延迟一段时间后窄带信号的相关函数会显着地强于宽带噪声这一特征,将原始输入信号接入具有固定延迟的延迟线作为参考信号。只要选取的延迟△足够长,参考信号的宽带噪声和原始输入的宽带噪声相关性就会迅速减弱,而窄带周期信号的相关性不会受到影响。根据自适应滤波理论可知,ALE滤波会有一个学习过程,学习过程就是误差信号趋于不断减小的过程。当学习过程进入稳态后,滤波器输出是源窄带周期信号和一个随机的误差,其误差可以通过选取合适的步长因子而达到很小的振幅。ALE原理图如图2所示。

2.2 ALE的Matlab仿真

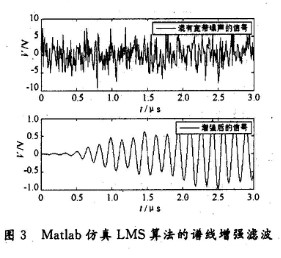

Matlab是数字信号处理和仿真的有效工具,设计之初使用Matlab进行仿真,可以有效地*估设计的最终效果,为整个设计过程提供强有力的理论支持。首先用Matlab仿真以LMS算法实现的ALE,从仿真结果的时域波形和处理时间两方面证明算法在ALE系统中的有效性。将正弦波混合高斯白噪声作为谱线增强滤波的输入信号,图3是用Matlab对算法的部分仿真结果。可以看出根据混有噪声的输入信号根本无法判断原始周期信号,经过0~100时间长度的学习过程后滤波器输出信号已经具有明显的周期性,宽带噪声得到有效的滤除,窄带信号得以滤出。而这段时间在高速FPGA中只需要μs级的处理时间,满足实时性要求。

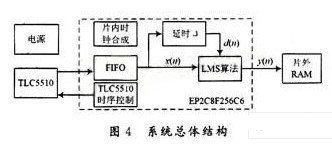

3 系统结构

ALE系统总体包括:模/数转换、FPGA核心处理、片外RAM、电源等。前端采用TLC5510完成模拟信号的采集,并以数字信号的形式传递给FPGA。FPGA部分是整个系统的核心,其实现模/数转换器时序控制、内部数据缓存FIFO、片内时钟合成、谱线增强算法以及片外RAM控制。经过谱线增强后的数据存入片外RAM芯片CY7C1021V。电源提供整个系统需要的3.3 V和5 V以及TLC5510的参考电压。系统结构如图4所示。

TLC5510是TI公司的高速模/数转换器,可以用于视频处理、高速数据转换等领域,它的转换速率达到20 Mb/s,采用高速AD芯片是为了与FPGA的高速处理能力相匹配。EP2C8F256C6是Altera公司的生产的CycloneⅡ系列的FPGA,片内具有162 Kb的片内存储器和36个18×18 b片内乘法器,可以用于实现复杂数字信号算法。片内存储器基于流行的M4K存储器块,可以支持广泛的配置方式,包括RAM,ROM、先入先出(FIFO)缓冲器以及单端口和双端口模式等。片内乘法器是低成本数字信号处理(DSP)应用的理想方案。这些乘法器可用于实现通用DSP功能,如有限冲击响应(FIR)滤波器、快速傅里叶变换、相关器、编/解码器以及数控振荡器(NCO)。EP2C8F256C6提供高级外部存储器接口支持,允许开发人员集成外部单倍数据速率(SDR)、双倍数据速率(DDR)、DDR2 SDRAM器件以及第2代4倍数据速率(QDRⅡ)SRAM器件。片内具有时钟管理模块,利用PLL实现片内时钟合成,使数据处理速率远高于信号采集速率,以满足实时性要求。在FPGA内部首先实现TLC5510的采样控制,采样信号先要存人片内FIFO,当每次ALE算法迭代完成后,取出FIFO中的数据,更新处理数据。需要处理的数据经过信号延迟处理和LMS自适应滤波算法后得到谱线增强的信号。片内时钟合成模块为系统提供时钟信号,利用片内PLL对晶振时钟倍频和分频,为片内提供600 MHz时钟和片外TLC5510以及RAM提供10 MHz时钟。为了保证数据精度。经过ALE处理后的数据以16位二进制数字信号输出。片外存储器选用64K×16 b静态RAM芯片CY7C1021V,它的读/写控制时序也由FPGA实现。

3.1 TLC5510的控制

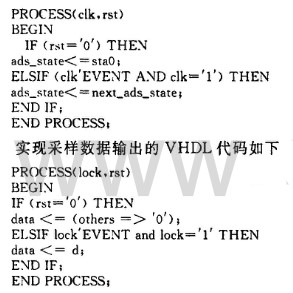

TLC5510是8位高速模数转换器,以流水线的工作方式进行采样,在每一个时钟周期启动1次采样、完成1次采样,采样在时钟下降沿进行,经过2.5个时钟周期后输出转换结果。设计中根据采样时序,用状态机来描述采样控制过程,实现了采样的控制。实现状态交替的VHDL代码如下:

3.2 采样信号延迟

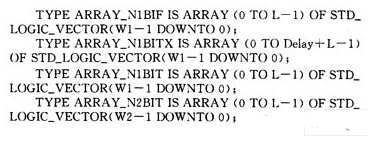

为了实现延时,FPGA片内开辟了3个缓冲区,分别是输入、时延、权值缓冲区。采样后的数据首先存入片内数据缓存FIFO,进入待命状态。时延缓冲区实现△长度的时延,权值缓冲区储存权值。其中,时延缓冲区和输入缓冲区地址是连续的。时延缓冲区的长度由延迟△决定,输入缓冲区和权值缓冲区的长度由权值的维数决定。缓冲区的实现是在VHDL语言编写的程序中定义存储数据的向量,这些数据向量的数据类型定义如下:

其中:ARRAY_N1BIF定义的是滤波器参数向量的数据类型;ARRAY_N1BIYX定义的延迟后信号向量的数据类型;ARRAY_N1BIT定义的是输入信号向量的数据类型;ARRAY_N2BIT定义的是谱线增强后信号向量的数据类型;W1是采样数据的宽度,这里为8;Delay是延时长度;L是滤波器阶数。

3.3 LMS算法核心模块

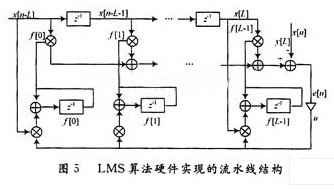

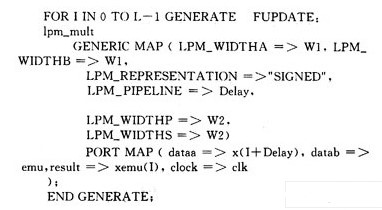

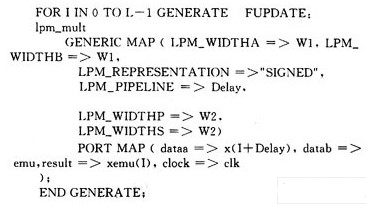

这是设计的核心部分也是设计中的难点。用FPGA实现复杂数字信号处理并不像DSP中那样简单,需要考虑时序同步、数据宽度以及如何舍入。该设计采用16阶自适应滤波器实现ALE,滤波器初始权值全部为0,按照式(3)的算法进行迭代更新,算法实现中用到大量乘法运算。调用芯片内部嵌入的乘法器宏功能模块lpm_mult使实现这些乘法运算更加快速、高效的方案。lpm_mult模块输入采样的8位数据,因为在乘法运算中2个8位二进制数相乘得到的结果是1个16位二进制数,所以设计中将处理结果输出为16位二进制数。为了提高自适应滤波速度,设计中采用流水线的滤波器结构。流水线结构能够显着地提高处理的速度,但是要消耗更多的硬件资源,特别是硬件乘法器,如果LMS FIR滤波器的长的为L则需要2L个通用乘法器。设计中L=16,片内有36个片内乘法器可以胜任处理要求。编译结果显示片内应用于LMS核心算法的其他资源消耗全部小于或等于总消耗的6%,其余资源可以用于片内的采样、输出等时序控制。LMS算法硬件实现的流水线结构框图如图5所示。

流水线结构中调用乘法器的VHDL代码如下:

4 仿真结果分析

VHDL程序在QuartusⅡ软件上部分仿真结果如图6所示,图中仿真数据以十进制表示。因为仿真结果不便于绘制类似Matlab中的图形,将仿真结果的数据与Matlab仿真结果进行对比。通过行比较,发现处理结果在大体上与Matlab相一致,但是在幅度上整体有些衰减,这是由于FPGA中将处理结果的低位进行截尾处理,而Matlab仿真环境使用浮点形式、数据位数长,处理精度远高于FPGA,FPGA设计中存在较大的截尾误差。该仿真结果表明,基于:FPGA实现ALE是切实可行的。

5 结 语

系统采用FPGA芯片加上少量的外围电路,完成了信号的自适应谱线增强。通过调用FPGA片内乘法器和片内存储器,完成了LMS算法的自适应谱线增强,仿真结果与理论相符合。现代数字信号处理算法大多要进行大量的乘法运算,调用FPGA片内乘法器是实现这些算法的快速高效而又经济的手段,这使得复杂信号处理算法在FPGA上实现成为可能。流水线结构是硬件设计中牺牲资源以提高速度的有效手段,有效地利用流水线可以显着地提高资源利用率和处理速度。该设计可以实现高速、准确地谱线增强,在需要滤除宽带噪声提取单根谱线的领域具有一定的现实意义。

-

LMS算法实现对自适应谱线增强器的仿真2022-05-07 1303

-

基于FPGA的自适应LMS算法的实现2021-05-28 1285

-

求大神分享一种基于FPGA的自适应谱线增强系统的设计2021-04-29 1242

-

LMS自适应算法的FPGA设计与实现_陈亮2017-03-19 1177

-

变抽头长度LMS自适应滤波算法2017-01-03 1123

-

求助!如何使用labview编写 VS_LMS 算法自适应陷波器2015-04-01 4647

-

用FPGA实现LMS自适应滤波2013-08-20 3141

-

基于LMS算法与RLS算法的自适应滤波2012-07-06 2850

-

语音去噪LMS自适应滤波器算法2011-01-15 817

-

改进的变阶数LMS自适应滤波算法2010-05-13 3872

-

改进的变步长LMS自适应算法及其应用2010-04-26 3283

-

基于AccelDSP的自适应滤波器设计2010-04-24 3251

全部0条评论

快来发表一下你的评论吧 !