基于VHDL语言和FPGA开发板实现数字秒表的设计

描述

应用VHDL语言设计数字系统,很多设计工作可以在计算机上完成,从而缩短了系统的开发时间,提高了工作效率。本文介绍一种以FPGA为核心,以VHDL为开发工具的数字秒表,并给出源程序和仿真结果。

1 系统设计方案

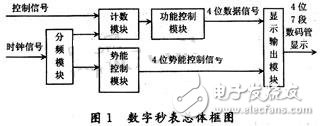

1.1 系统总体框图

数字秒表主要有分频器、计数模块、功能控制模块、势能控制模块和显示输出模块组成。系统框图如图1所示。

本次的设计仿真选用以EP1C6Q240芯片为核心的FPGA开发板,该开发板提供了较完善的外围周边电路和信号接口,并提供了一块4位7段数码管的扩展板,为本次设计提供了硬件条件。在设计中,功能控制模块根据控制选择不同的功能状态的时间输出,通过势能控制模块和显示输出模块驱动7段数码管显示相应的时间。

1.2 系统功能要求

(1)具有时钟秒表系统功能要求显示功能,用4个数码管分别显示秒和百分秒;

(2)具有3种功能状态:系统时间运行状态,系统时间至零状态,时钟正常显示状态,通过输入控制信号可以使系统在这3个状态之间切换,使数码管显示相应状态的时间;

(3)开启时间设定、关闭时间设定可通过控制信号中的时间调节来设置,在秒设置方面每按一下,秒就会自动加1,采用60进制计数,当计数到59时又会恢复为00;百分秒设置方面每按一下,百分秒会自动加1,采用100进制计数,当计数到99时,向上进位并恢复00。系统时间可以同单独的至零信号,将数码管显示时间直接恢复到00.00状态。

2 模块功能设计及仿真

2.1 分频模块

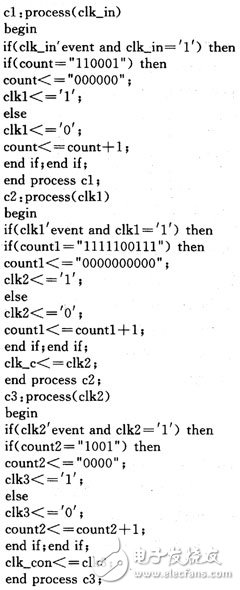

开发板提供的系统时钟为50 MHz,通过分频模块3次分频,将系统的时钟信号分为100 Hz和1 000 Hz分别提供给计数模块和势能控制模块作为时钟控制信号。该模块部分VHDL源程序如下:

2.2 计数模块

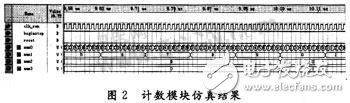

计数模块中,时钟信号是100 Hz作为秒表的百分秒输入,百分秒为100进制计数器,其进位输出作为秒的计数时钟,秒为60进制计数器。控制信号输入端的begin-stop和reset信号控制计数器的开始、停止和至零。该模块部分VHDL源程序如下,方针结果如图2所示:

2.3 势能控制模块

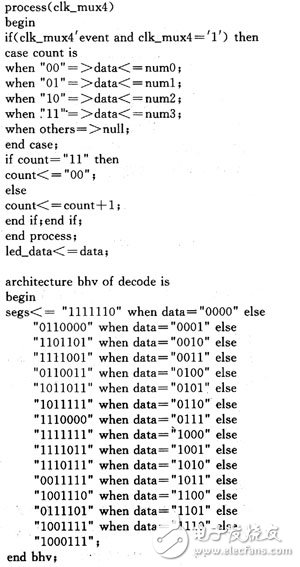

本次设计选用的开发板数码管扩展板的数码显示采用的是4个数码管动态扫描输出,一般只要每个扫描频率超过人的眼睛视觉暂留频率24 Hz以上就可以达到点亮单个显示而不闪烁,扫描频率采用1 kHz信号。通过势能控制,每个数码管的显示频率为250 Hz,满足显示要求。该模块部分VHDL源程序如下:

2.4 显示控制模块

本次设计选用的开发板在4位数码管输入方面只提供1个数据接口,用来动态显示4位数据,在数据输入信号方面要做到和势能控制信号同频率输出,才能保证数码显示不会出错或显示移位。该模块部分VHDL源程序如下:

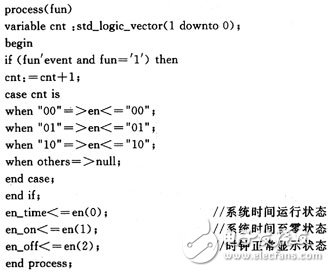

同时通过控制信号示系统处在不同的功能状态:系统时间运行状态,系统时间至零状态,时钟正常显示状态。利用功能转换信号实现3个功能状态之间的转换,并产生相应的控制信号去控制显示输出模块不同状态的正确显示。其部分源程序如下:

3 系统部分功能仿真

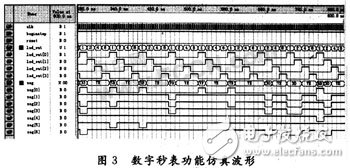

各部分模块完成后,用QuartusⅡ对程序编译、仿真、得到的仿真波形如图3所示。

本系统采用的FPGA芯片为Altera公司的EP1C6Q240,用VHDL和QuartusⅡ软件工具开发,设计输入完成后,进行整体的编译和逻辑仿真,然后进行转换、延时仿真生成配置文件,最后下载至FPGA器件,完成结果功能配置,实现其硬件功能。

4 结 语

该系统运用先进的EDA软件和VHDL,采用模块法自顶向下的设计原则,并借助FPGA实现数字秒表的设计,充分体现了现代数字电路设计系统芯片化,芯片化设计的思想突破了传统电子系统的设计模式,使系统开发速度快、成本低、系统性能大幅度地提升。

-

硬件描述语言和FPGA的具体关系2022-02-08 1644

-

分享一种数字秒表设计方法2021-05-11 1974

-

C语言入门开发板实验指导电子版下载2021-03-24 980

-

使用VHDL语言和FPGA设计一个多功能数字钟的论文免费下载2020-08-28 1282

-

使用51单片机开发板实现LED点阵显示数字0的程序免费下载2019-10-31 1727

-

请问VHDL语言和verilog语言有什么区别?2019-03-28 3016

-

利用VHDL硬件描述语言和FPGA技术完成驱动时序电路的实现2017-11-24 2171

-

51开发板实现计算器2016-11-23 1070

-

基于Xilinx FPGA和VHDL的数字秒表设计与仿真实现2012-12-25 7241

-

基于VHDL语言含秒表数字钟仿真和引脚设置2012-05-22 3383

-

基于CPLD的VHDL语言数字钟(含秒表)设计2011-09-27 2788

-

数字电压表的VHDL设计与实现2009-10-12 2232

-

VHDL语言在FPGA/CPLD开发中的应用?2009-05-10 1516

全部0条评论

快来发表一下你的评论吧 !