从“能用”到“懂原理”:ARMv8寄存器架构深度拆解

电子说

描述

做嵌入式或芯片开发的同学,大概率都有过这样的困惑:

写汇编时知道X0-X30是通用寄存器,调用函数时按规矩用X0-X7传参,但为什么是这8个?剩下的寄存器又该怎么划分职责?调试异常时,盯着SPSR、ELR这些寄存器,只知道是保存状态的,却搞不清背后的设计逻辑;

其实ARMv8的寄存器架构,不是“零散知识点的堆砌”,而是围绕“高效运算”“安全隔离”“状态可控”三个核心目标设计的完整体系。

今天这篇文章,我不做枯燥的知识点罗列,而是从“为什么这么设计”“实际怎么用”两个角度,把通用寄存器、特殊寄存器、系统寄存器的逻辑讲透,还配套了直观的结构图和速查表,帮你真正做到“知其然也知其所以然”。

一、先搞懂核心前提:AArch64与AArch32的区别

聊ARMv8寄存器之前,必须先明确一个关键:ARMv8支持两种执行状态——AArch64(64位)和AArch32(32位,兼容ARMv7),两者的寄存器资源完全不同。

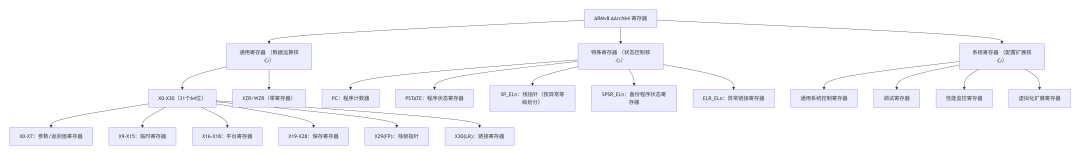

我们日常开发中重点关注AArch64(毕竟现在主流芯片都是64位),后面的内容也主要围绕AArch64展开,先看一张总览图,建立整体认知:

从图中能清晰看到,ARMv8 AArch64的寄存器主要分三类:通用寄存器(数据运算核心)、特殊寄存器(状态控制核心)、系统寄存器(配置与安全核心)。接下来逐个拆解。

二、通用寄存器:数据运算的“临时货架”,为什么这么划分职责?

通用寄存器就像处理器的“临时货架”,用来存放运算过程中的数据、函数参数、返回值等。ARMv8 AArch64给了31个64位通用寄存器(X0-X30),为什么是31个而不是32个?因为第32个被“零寄存器(XZR)”占用了,后面会说。

很多资料只告诉你“X0-X7传参、X29是栈帧指针、X30是链接寄存器”,但没说“为什么要这么规定”。核心原因是:统一函数调用规范,避免不同编译器、不同函数之间的调用混乱。

我们用“仓库分拣”来类比:如果每个分拣员(函数)都按自己的习惯放包裹(数据),跨部门协作时就会乱套。所以ARM制定了AAPCS64(ARM架构64位应用程序调用规范),给31个通用寄存器划分了明确职责,下面这张表把“职责、用途、是否需要保存”说的明明白白:

| 寄存器组 | 具体寄存器 | 核心职责(类比) | 实际用途 | 函数调用时是否需要保存 |

| 参数/返回值寄存器 | X0-X7 | 快递收发窗口 | 传递函数参数(最多8个,超过用栈)、存储函数返回值 | 不需要(由调用者保存) |

| 临时寄存器 | X9-X15 | 临时工作台 | 存放函数内部临时数据,运算过程中的中间结果 | 不需要(由调用者保存) |

| 平台寄存器 | X16-X18 | 专用工具柜 | 用于动态链接、调试等平台级功能(如X16/X17作为过程调用临时寄存器) | X16-X17不需要;X18看平台约定 |

| 保存寄存器 | X19-X28 | 长期存储架 | 存放函数需要长期使用的数据,跨函数调用时不会丢失 | 需要(由被调用者保存到栈) |

| 栈帧/链接寄存器 | X29(FP)、X30(LR) | 仓库定位器+返回地址记录 | X29:栈帧指针,标记当前函数栈的起始位置;X30:链接寄存器,存储函数返回地址 | 需要(由被调用者保存) |

| 零寄存器 | XZR/WZR | 固定零值货架 | 读取时始终返回0,写入时忽略;用于快速清零、比较等操作 | 无(本身是固定值) |

这里有两个关键疑问需要解答:

1. 为什么X0-X7只能传8个参数?超过就要用栈?

核心是“平衡性能与资源”。31个通用寄存器中,拿出8个作为参数寄存器,既能满足绝大多数函数的参数传递需求(统计显示,大部分函数参数不超过8个),又不会占用过多寄存器资源影响其他运算。如果参数过多,就用栈来补充——虽然栈的访问速度比寄存器慢,但胜在容量大。

2. 为什么有的寄存器需要保存,有的不需要?

本质是“减少不必要的栈操作”。X0-X7、X9-X15这些寄存器,通常是调用者(发起函数调用的一方)在调用前使用,被调用者(被调用的函数)可以直接覆盖;而X19-X28、X29、X30是被调用者在执行过程中需要长期使用的,为了不破坏调用者的原有数据,就需要被调用者在使用前保存到栈,用完后恢复。

另外,每个X寄存器(X0-X30)都可以直接使用低32位,对应的名称是W0-W30(比如X0的低32位是W0),这是为了兼容32位运算——当执行32位指令时,使用W寄存器,运算结果会自动零扩展到64位(X寄存器),兼顾了灵活性和兼容性。

三、特殊寄存器:处理器的“控制中枢”,状态与流程的核心

如果说通用寄存器是“干活的工具”,那特殊寄存器就是“指挥工具干活的大脑”——负责管理处理器状态、控制指令执行流程、处理异常等核心功能。ARMv8的特殊寄存器不多,但每一个都至关重要,我们还是用“表格+原理”的方式拆解:

| 寄存器名称 | 核心功能(类比) | 关键细节与实际应用场景 |

| 程序计数器(PC) | 任务进度条 | 存储下一条要执行的指令地址;ARMv8中PC不可直接修改(需通过分支指令间接修改)。应用场景:调试时查看PC值,就能知道程序执行到了哪一行代码。 |

| 程序状态寄存器(PSTATE) | 系统状态仪表盘 | 整合了ARMv7中的CPSR(当前程序状态寄存器)功能,包含条件标志位(N/Z/C/V)、异常等级(EL0-EL3)、中断屏蔽位(I/F/A/D)等。核心作用:判断指令执行结果(比如比较两个数后,Z位为1表示相等)、控制处理器运行状态(比如屏蔽IRQ中断后,处理器不响应外部中断)。 |

| 栈指针(SP_ELn) | 仓库货架的起始定位器 | 每个异常等级(EL0-EL3)都有独立的栈指针(SP_EL0、SP_EL1、SP_EL2、SP_EL3),避免不同等级的程序共用栈导致数据混乱。应用场景:操作系统内核运行在EL1,用户程序运行在EL0,两者用不同的SP,确保内核栈的安全性。 |

| 备份程序状态寄存器(SPSR_ELn) | 状态备份硬盘 | 当发生异常时(比如用户程序调用系统调用,从EL0进入EL1),处理器会自动把当前的PSTATE状态保存到对应等级的SPSR中(比如进入EL1就保存到SPSR_EL1);异常返回时,再从SPSR中恢复PSTATE,让程序回到异常发生前的状态继续执行。 |

| 异常链接寄存器(ELR_ELn) | 异常返回地址记录器 | 和SPSR配套使用:异常发生时,处理器会把“异常返回后要执行的指令地址”保存到ELR_ELn中;异常返回时,通过ERET指令把ELR_ELn的值加载到PC,程序就能回到原来的位置继续执行。应用场景:调试异常(如段错误)时,查看ELR_EL1的值,就能找到触发异常的代码地址。 |

这里重点讲一下PSTATE寄存器的核心字段,因为它直接决定了处理器的运行状态,用一张结构图更直观:

几个关键字段的作用:

1. 条件标志位(N/Z/C/V):这是最常用的字段,比如执行“ADD X0, X1, X2”后,处理器会根据结果自动更新这四个位——如果结果为0,Z位=1;如果结果为负数,N位=1;如果有进位,C位=1;如果有溢出,V位=1。后续的条件分支指令(比如BEQ,相等则跳转)就根据这些位来判断是否跳转。

2. 异常等级(EL0-EL3):ARMv8的安全隔离核心,等级从高到低是EL3(最高,通常是安全监控模式)>EL2(虚拟化扩展模式,用于虚拟机监控器)>EL1(内核模式,操作系统运行在此)>EL0(用户模式,应用程序运行在此)。不同等级的程序拥有不同的权限,比如EL0的程序不能直接访问EL1的寄存器,确保了系统安全。

3. 中断屏蔽位(I/F/A/D):用于控制处理器是否响应对应类型的中断——I位屏蔽IRQ(普通中断),F位屏蔽FIQ(快速中断),A位屏蔽系统错误中断,D位屏蔽调试中断。比如内核在执行关键任务时,会设置I位和F位,避免被中断打断。

四、系统寄存器:处理器的“配置面板”,定制化功能的核心

系统寄存器是ARMv8提供的“高级配置接口”,主要用于配置处理器的各种功能(如虚拟化、调试、性能监控、安全特性等),通常只有特权等级(EL1及以上)的程序才能访问。

很多同学觉得系统寄存器复杂,其实核心原因是“种类多,但常用的不多”。ARMv8把系统寄存器分成了七大类,我们重点关注常用的几类,用表格梳理:

| 系统寄存器类别 | 核心作用 | 典型寄存器示例 | 应用场景 |

| 通用系统控制寄存器 | 配置处理器核心功能 | SCTLR_EL1(系统控制寄存器,控制MMU、缓存等)、CPACR_EL1(协处理器访问控制) | 操作系统内核初始化时,配置MMU(内存管理单元)、开启缓存,都需要修改这些寄存器。 |

| 调试寄存器 | 支持程序调试功能 | DBGDTR_EL0(调试数据传输寄存器)、DBGWFAR_EL1(调试观察点地址寄存器) | 调试器(如GDB)通过这些寄存器设置断点、观察点,查看程序运行状态。 |

| 性能监控寄存器 | 统计处理器性能数据 | PMCR_EL0(性能监控控制寄存器)、PMCNTENSET_EL0(性能计数器使能寄存器) | 性能优化时,通过这些寄存器统计指令执行次数、缓存命中率等数据,找到性能瓶颈。 |

| 虚拟化扩展寄存器 | 支持虚拟机功能 | HCR_EL2(虚拟化配置寄存器)、VPIDR_EL2(虚拟机ID寄存器) | 虚拟机监控器(如KVM)通过这些寄存器管理多个虚拟机,实现资源隔离。 |

系统寄存器的命名有个规律:通常以“Reg_ELn”结尾,n表示该寄存器可访问的最低异常等级。比如SCTLR_EL1,最低可在EL1访问,EL2、EL3也能访问;而PMCR_EL0,最低可在EL0访问,所有等级都能访问。这个命名规则能帮我们快速判断寄存器的访问权限。

五、核心总结:ARMv8寄存器架构的设计逻辑

看到这里,相信你对ARMv8寄存器已经有了整体的认知。最后我们提炼一下核心设计逻辑,帮你快速记住:

1. 分层设计:通用寄存器负责“数据运算”,特殊寄存器负责“状态控制”,系统寄存器负责“功能配置”,三层各司其职,既独立又协同;

2. 安全优先:通过异常等级隔离(EL0-EL3)、独立栈指针(SP_ELn)、权限控制(系统寄存器访问限制),确保不同等级的程序不能越权访问资源,保障系统安全;

3. 兼容与灵活:支持AArch64与AArch32两种状态,X寄存器可兼容W寄存器(32位),兼顾了新架构的性能和旧架构的兼容性;

4. 高效运算:通用寄存器的职责划分(参数/临时/保存寄存器)遵循AAPCS64规范,减少栈操作,提升函数调用和数据运算效率。

审核编辑 黄宇

-

一文帮你梳理Cortex与ARMv8等基础概念2021-12-14 1494

-

ARMv8架构资料分享2022-03-21 2643

-

ARMv8系统定时器需要实现的寄存器及各个寄存器的偏移2022-04-01 5708

-

ARMv8架构的两种执行状态分别是什么2022-04-06 5921

-

ARMv8架构概述2022-05-13 3153

-

为什么访问ARMV8系统寄存器icc_sre_el2会发生错误呢2022-08-30 2283

-

ARMV8的The current Program Counter介绍2023-02-23 1069

-

如何使用CSAT调试Armv8平台2023-08-02 708

-

ARM推新品:ARMv8首次支援64位元指令集2011-11-01 1790

-

TRACE32支持ARMv8架构2017-09-12 1059

-

从软件开发的角度概述ARMv8处理器架构中的虚拟化操作2018-10-13 1326

-

ARM重新定义ARMv8新架构,ARMv8新架构特性解说2020-10-08 11903

-

Armv8架构及虚拟化介绍2023-04-16 8844

-

u-boot armv8链接脚本2023-12-07 1662

-

ARMv8体系结构入门(附流程图+脑图)2026-01-06 1087

全部0条评论

快来发表一下你的评论吧 !