基于FPGA和DDS+PLL器件实现跳频信号发生器的设计

描述

引 言

为了保证机载电台的设计性能和通信质量,并且各种电台都有各自详细的技术指标要求,需要使用很多台单一功能的仪器或综合检测仪来测试。目前,产生稳定可靠、符合要求的跳频信号已成为进行跳频关键技术验证、通信设备开发预研,综合测试系统研制的瓶颈。本设计正是某机载电台综合检测仪的一部分,为其提供一个高稳定度的跳频信号源。

由于FPGA 器件速度快、密度高、功耗低、可配置性强, 现已在许多领域得到了广泛的应用。硬件描述语言的出现使FPGA 的设计更加方便、快捷。DDS 技术具有频率转换速度快、分辨率高及相位噪声特性好等优点,但组合干扰信号多,难以控制,无法适应跳频通信的要求。而PLL 技术具有控制灵活、体积小、电路简单、杂散抑制度高及频谱纯度高等一系列优点,是当今战术电台的主流技术方案,但面临高速的技术要求,锁相环路的固有惯性已成为严重的障碍。因此,本设计以FPGA(EP1C12)为核心进行跳频控制,采用DDS(AD9850)与PLL(MC145152)相结合,由DDS 提供快速跳频的小步进间隔,PLL 工作在大步进间隔,增大环路带宽,缩小跳频时间,而且完成对杂散的抑制。在此硬件平台上加载相应的程序,可以产生所需的跳频信号,具有转换速率快、电路简洁、系统控制简易灵活等优点。

1. 信号发生器的硬件设计

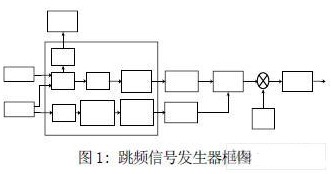

图1 所示是跳频信号发生器组成框图。整个硬件系统分为基带子系统、中频子系统和射频子系统三部分:

1)基带子系统包括FPGA 和其外部所需的D/A 转换器(包括其所需的波形成型滤波器)、按键开关、数码管电路以及拨码开关。

该子系统主要以FPGA 为核心,,首先FPGA 从拨码开关和键盘电路采集信息数据并通过显示电路显示,然后对这些获取的信息数据进行BFSK 调制,产生BFSK 波形的样点值,经D/A 转换器和成型低通滤波器产生BFSK 的基带模拟波形,同时,FPGA 还产生跳频码序列,通过预设的跳频图案表,最后获得产生该频率信号所对应的DDS 控制字,并将该控制字写入DDS 之中和对DDS 发出频率切换的指令。FPGA 以1000 次/秒的频率来更新DDS 输出的频率,这样,在DDS 就能产生了1000 跳/秒的跳变中频载波信号。

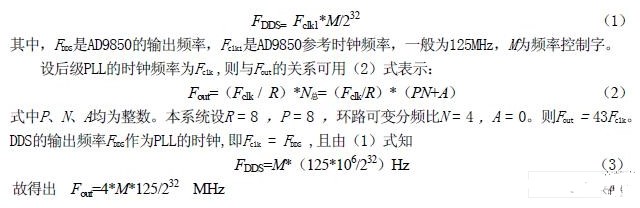

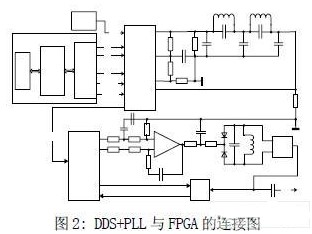

2)中频子系统包括DDS+PLL、混频器、中频滤波器。在跳频信号产生过程中频率合成器是其中的关键技术之一,在本设计中,DDS选用的是AD公司的AD9850,在125MHz时钟信号的驱动下,可以产生分辨率为4.492Hz的信号。虽然DDS优点突出,但是它的输出频率不高,不能满足设计所需的44.625~90.125MHz跳频范围,因此必须通过PLL倍频。具体实现电路是AD9850的输出经低通滤波后作为时钟驱动锁相环MC145152。如图2所示为FPGA采用并行输入方式与DDS+PLL的连接图。对于PLL,其换频时间Ts1与鉴相频率有关,工程上近似为Ts1 = 25/ Fr = 25R/ Fclk,其中Fclk就是DDS的输出频率。在本系统中,R= 8,FDDS的范围是20. 5MHz ~22. 5MHz。所以Ts1的量级是十几μs量级,即Ts的量级也是十几μs量级,因此完全能满足1000跳/秒的指标。根据AD9850的相关特性可知,其输入和输出频率的关系为:

其中M 为频率控制字。从(4)式也可知该频率合成器的分辨率为4*3*125/ 232MHz=1.164Hz。由此可知,完全能够满足本设计对频率合成器的要求。

BFSK 基带信号与DDS 产生跳变的载波信号在混频器中混频后再产生跳变的中频信号(44.625~90.125MHz)经滤波后送入射频电路。

3)射频子系统有频率合成器、混频器、滤波器等构成,其中频率合成器采用的是有固定频率输出的由锁相环路构成的频率合成器,以产生200MHz 的输出频率作为本振频率。中频宽带信号(44.625~90.125MHz)与本振频率在混频器中混频后,经过带通滤波器取上边带,得到(109.875~155.375MHz)的跳频信号。

2. 信号发生器的软件实现

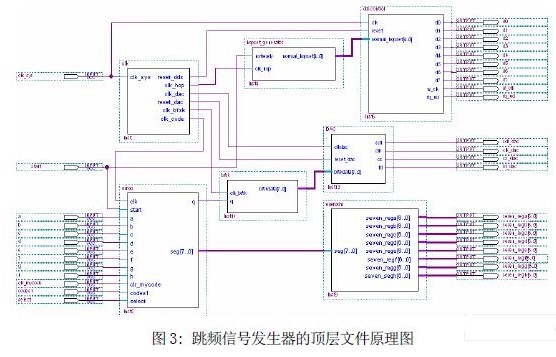

在本系统的软件设计实现中,采用了VHDL 硬件描述语言进行设计,并在Altera 公司的QuartusⅡ7.0 软件中完成基带子系统程序编写、语言编译和调试及硬件下载工作。本系统的软件结构框图主要有时钟分频模块、跳频图案产生模块、信息码输入模块、BFSK 调制模块及DAC 和DDS 的接口控制模块组成,具体框图如图3。

2.1 时钟分频模块

完成一次DDS 转换需要10 个时钟信号,因此选择系统时钟clk_sys 频率为50MHz,周期为0.02us。以系统时钟为基准,14 个状态为一个循环产生各种时钟信号。每个状态循环的第0 个状态的1 个周期产生跳频图案产生模块的时钟信号,第0 和第1 个状态的2 个周期产生AD9850 控制代码的复位信号。当AD9850 控制代码的复位信号变为低电平后,在系统时钟的作用下,AD9850开始装入控制信号。

2.2 跳频图案产生模块

本系统的跳频图案发生器是由31 级m 序列构成,把该序列相邻的5 个码元对应的值模20 作为频率控制码,系统中不同的信道在同一时钟控制下进行全同步跳频,跳频图案为同一序列的不同偏移,这样就保证了各信道的频率各不相同,不会产生频率交叠。系统的中频频段为44.625~90.125MHz,跳频带宽为45.5MHz,分了20 个频率点,跳频最小间隔为2.275MHz。采用以上介绍的DDS+PLL 的频率合成法,根据电路可推算出输出频率Fout与频率控制字M 的关系为

(一般FDDS=125MHz),由此关系式产生相应的频率。

2.3 信息码输入模块

信息码输入模块包括外部输入模块、序列信号产生模块、2 通道数据选择模块。外部输入模块是将输入的8 位用户自定义的信息码在按键开关信号codes1 和clr 的控制下循环移位输出,输出信号为q。当循环移位键按下即codesl=‘0’时,从拨码开关并行读入8 位信息码;当codesl=‘1’时,8 位信息码循环移位,最后一位码作为待发送的码元。当清除键按下即clr=‘0’时,8 位信息码全部置‘0’。序列信号产生模块在分频器输出的时钟信号的作用下能够循环产生一组或多组序列信号,在开始初始化按键按下即clr=‘0’时,初始化为“10110101”。通道数据选择模块通过按键信息方式选择开关来选择采用用户自定义的信息或由序列信号产生模块生成的信息进行处理。

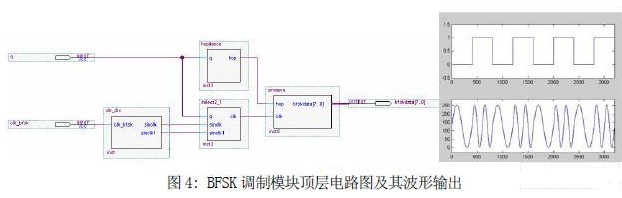

2.4 BFSK 调制模块

该模块的功能是在系统时钟控制模块输入的时钟clk_bfsk 的控制下,由通过数据选择模块输入的序列q 的信息比特决定发送分频器输出的2 个频率中的哪一个来进行BFSK 调制,输出为BFSK 波形的各点采样幅值,幅值的精度为8 位二进制,该8 位信号经过D/A 转换后,即得到实际的BFSK 信号。如图4 所示,该调制模块共分为分频器、跳变检测、2:1 数据选择器、正弦波信号产生器等5 部分。

正弦波信号产生器中每个采样点采用8 位量化编码,即8 位分辨率。用包含100 个状态的状态机来实现,同时设计一个异步复位端,保证当每个‘1’或‘0’到来时其调制信号正好位于坐标原点sin0 处。状态机共有8 位输出,经DAC 变换为模拟信号输出。

由于仿真结果并非直观的波形,所以将BFSK 模块在Quartus 中的波形仿真结果bfsk.vwf 另存为列表文件bfsk.tbl。把该文件放置在Matlab 程序的当前工作文件夹内,使用编写的Matlab程序读取该文件,并提取其中的数值作图,可以得到图7 所示直观的BFSK 波形,这样可以看到频率随着输入信息的变化而变化,验证设计的正确性。

2.5 DAC 和DDS 的接口控制模块

利用状态机模型实现DAC 和DDS 的控制时序。利用组合逻辑电路产生输出信号容易出现毛刺现象,单一进程的状态机的程序可读性不好,因此我们采用时序逻辑电路产生输出信号的格式进行控制程序的编写。

3. 结束语

本文提出一种基于FPGA和DDS+PLL 技术的跳频信号源的实现方案。在FPGA中利用VHDL语言来实现基带子系统,通过修改程序中的相关内容便可产生多种形式的跳频信号,具有很大的灵活性,并且电路易于实现同步。实验证明,通过FPGA和DDS+PLL相结合,该跳频信号源设计原理正确,输出的跳频信号稳定、频率分辨率高、频率切换速度快、输出频率高,可在45.5MHz范围内实现全频段跳频。

-

信号发生器原理_DDS芯片及应用_DDS信号发生器设计2015-06-23 8153

-

基于DDS的跳频信号产生系统案例解析2020-11-14 5437

-

基于FPGA的DDS信号发生器2019-03-18 3148

-

怎么设计基于FPGA和虚拟仪器的DDS信号发生器?2019-09-29 1977

-

如何利用FPGA设计DDS信号发生器?2021-04-09 1840

-

怎么利用FPGA设计基于DDS的信号发生器?2021-05-06 1991

-

怎么实现基于FPGA+DDS的正弦信号发生器的设计?2021-05-11 1765

-

基于FPGA的DDS调频信号的研究与实现2009-06-26 661

-

基于FPGA 的新的DDS+PLL时钟发生器2009-12-14 553

-

基于FPGA的DDS信号源设计与实现2010-02-11 1001

-

基于FPGA短波差分跳频信号发生器的设计2011-08-13 2260

-

基于DDS的信号发生器设计2016-01-11 1140

-

DDS多波信号发生器的实现2016-11-22 1130

-

基于FPGA的DDS信号发生器设计方案解析2017-12-04 2253

-

基于FPGA 的DDS正弦信号发生器的设计和实现2024-03-24 916

全部0条评论

快来发表一下你的评论吧 !