FPGA的高速总线测试和分析的方法与工具介绍

描述

随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物理链路的速度从200Mbps到高达10Gbps,高速IO的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员面临的巨大挑战。这些挑战使设计人员非常容易会把绝大部分设计周期时间放在调试和检验设计上。

1. 引言

随着FPGA的设计速度和容量的明显增长,当前流行的FPGA芯片都提供高速总线,例如DDR内存总线,PCI-X总线、SPI总线;针对超高速的数据传输,FPGA通过集成SerDes提供高速串行IO,支持各种诸如PCI-E、GBE、XAUI等高速串行总线协议,为各种不同标准的高速传输提供极大的灵活性。典型的高速FPGA器件提供的每一条物理链路的速度从200Mbps到高达10Gbps,高速IO的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员面临的巨大挑战。这些挑战使设计人员非常容易会把绝大部分设计周期时间放在调试和检验设计上。

为了加速对于FPGA中高速并行和串行总线的调试和验证,它需要使用新的高速信号完整性测试工具和分析方法。本文根据当前FPGA的高速总线测试和分析,提供了最新的方法和工具。

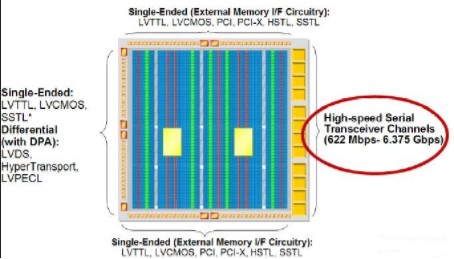

图1是一个典型FPGA的提供的各种高速接口。对于这些速度从200M到高达10G的高速总线,信号完整性的测试和分析是保证设计成功的基础和关键。

图1 典型FPGA的提供的各种高速接口

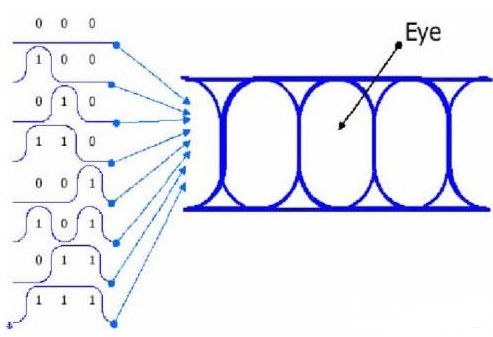

2. 高速串行总线眼图测试对于采用内嵌SERDES电路的FPGA芯片,其高速串行信号进行测试和验证,最基本的工具是通过示波器进行对其眼图测试。因为眼图能够非常直观的反映一条被测信号路径上的整体信号质量问题,包括信号的抖动量大小(眼宽)以及幅度的大小(眼高)等重要信息。图2是一个高速数据信号的眼图形成的过程。

图2 眼图的形成过程

从眼图的形成过程可以看出,一个NRZ编码的高速数据无论传输何种码流,都可以看作一个重复信号,经过一定时间和样本数的累计,它反映整个传输链路上的总体信号质量。

3. 选择合适的眼图测试工具

3.1 示波器带宽的要求

示波器是进行高速串行信号眼图测试的首选工具。无论是用高速实时示波器还是采样示波器(Sampling Scope)得到眼图,带宽是对示波器的基本要求。以一个NRZ编码的高速串行总线为例,它理想的波形是一个方波信号,方波信号是由它的基波(正弦波)和奇次谐波(3次,5次,7次…)组成。根据信号的传输速率和上升时间,选择尽量高带宽和最快上升时间的示波器,这样测试结果保留更多的谐波分量,构建高精度的眼图测试结果。

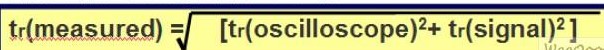

示波器带宽反映了对被测信号幅度上的衰减,而示波器上升时间决定了对被测信号上升时间测试的误差。经典的示波器带宽和上升时间的关系为:带宽×上升时间=0.35-0.45,0.35-0.45为常系数。每一个高性能示波器除了提供带宽的指标外,还会给出上升时间,表征其对阶跃信号的测试能力和精度。示波器测试结果的经验公式为:

高速串行数据(NRZ编码)提供一般为数据率,其最高的基频为比特率的一半。即假设给定一个NRZ编码的串行信号,码型为时钟码型(即传输的数据为1-0-1-0-1),从频域的角度观测该信号,它成为一个基波为数据率一半的方波信号,这个时钟码型是数据变化最快的情况。以泰克TDS6154C 大于15GHz带宽的实时示波器为例,它可以测试保留6.25Gb/s (2×XAUI)信号的五次谐波,以及10Gb/s (XFI)信号的三次谐波。下表列出了不同的高速串行总线在不同测试精度要求下对示波器带宽的要求。

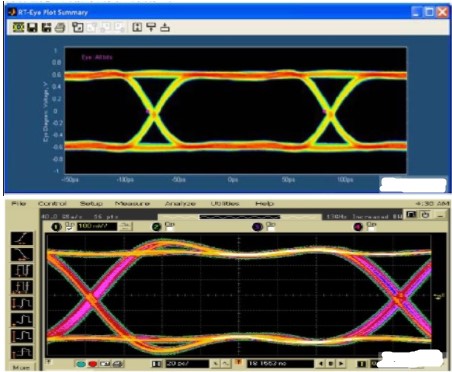

当示波器系统不能提供足够的系统带宽时,它会衰减对高速信号的高次谐波分量。测试结果除了引入由于示波器带宽不足导致的码间干扰(ISI),电压幅度的异常(过冲和衰减),还会导致抖动量过大,最终眼图模板测试的错误或者测试容限的减小,无法真正反映信号完整性问题。图3 分别是泰克TDS6154C 15GHz带宽和传统DSO 13GHz带宽实时示波器对一个FPGA器件提供的的6.25Gb/s高速数据进行的眼图测试结果比较。图中上半部分显示的眼图有很好的对称性,上升和下降时间更快,信号抖动量很小,真实的反映信号的真实特性。

由于13GHZ的DSO示波器系统带宽不足,无法捕获信号的五次谐波分量,图中下半部分的测试结果反映出眼图上升时间过慢;同时测试的眼图还存在明显的过冲和震铃,测试仪器导致的抖动也掩盖的信号的真正抖动大小。

图3 高速串行数据测试比较(上图为泰克TDS6154C示波器测试结果)

3.2 示波器高速采集内存的要求

当使用实时示波器对于FPGA信号进行信号完整性测试时,利用一次采集的数据构建眼图,所以除了示波器硬件带宽和高速采样率外,采集的数据量的大小非常关键,这样对示波器的高速采集内存就有了更高的要求。下图是在高采样率下,不同高速内存容量下一次捕获的数据量的大小。

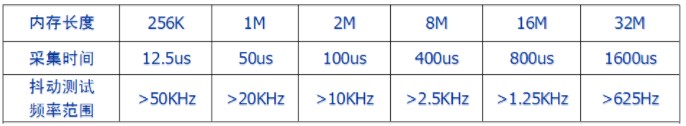

当对FPGA的高速信号进行抖动测试时,高速内存长度不仅决定了一次抖动测试中样本数的多少,还决定了示波器能够测试的抖动频率范围。针对信号中的各种低频抖动干扰源,高速采集内存长度是示波器进行低频抖动测试的关键。下表显示的为20GSa/s高采样率下,不同内存长度分析抖动频率范围的大小。

传统高性能示波器设计构架采用将高速采集前端(多达80颗ADC)和高速内存在物理上用一颗SOC芯片实现,由于有太多功能在一个芯片内部实现,导致片内高速内存容量的限制(在20GS/s下小于1M),无论是对于高速串行数据的眼图测试还是对于时钟信号的抖动测试,都存在很大的限制,并且日后无法对内存扩展升级。

为了弥补这种设计结构的缺陷,这类示波器会采用在芯片外部添加低速存储器弥补片内高速内存的限制,但外部存储器不能在高采样率下工作,一般只能提供2GS/s,样点间隔500ps,由于绝大多数信号边沿速度都在皮秒级,2GS/s无法在信号边沿采集足够样点,甚至出现会出现混叠,所以它无法提供有意义的眼图和抖动测试结果。

泰克TDS6154C高速实时示波器采用硅锗(SiGe)半导体集成采集前端,并使用独立的高速存储器,这样就不受内存长度的限制,并且它同时支持最大采样率和存储长度。

4. 抖动、噪声和BER测试和分析

针对FPGA中不断增长的串行数据传输速率,设计人员不仅进行眼图测试,还需要一套先进的测试和分析工具帮助他们更好地理解和改善他们设计方案的信号完整性。

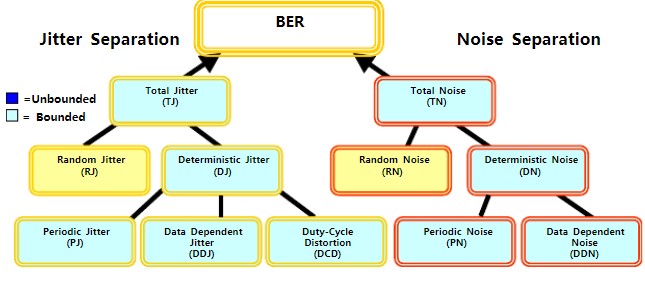

针对FPGA提供的各种高速串行信号,传统的采样示波器配合抖动分析软件针对FPGA中的高速串行信号能够进行抖动的测试,测试结果的分离,后期的抖动原因的定位和分析,以及水平时间分量上的BER分析。但是,对于导致BER的另一个主要原因,即串行信号中的噪声分量,没有一个彻底的测试和分析方法。图4显示了对于一个高速串行信号的抖动分量和噪声分量影响BER的过程。

图4 抖动分量和噪声分量的分解

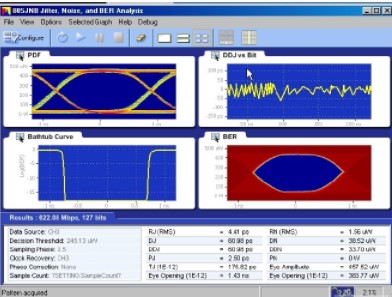

从事FPGA器件的设计和应用,以及背板的设计和制造的公司在开发基于超高速串行数据标准的产品时需要最高精度的抖动分析,噪声分析以及完整的BER眼图信息。泰克CSA/TDS8200系列采样示波器(Sampling Oscilloscope)测试眼图时,除了传统的眼图和抖动测试外,泰克80SJNB抖动和噪声分析软件提供了对于设计人员和调试人员更有价值的抖动、噪声、BER分析功能。

80SJNB不仅能够得到高精度的眼图测试结果,还能够通过分隔抖动和噪声,加快了识别水平和垂直眼图闭合原因的速度。由于它能够以独特的视角查看抖动和噪声的构成成分,80SJNB可以高度精确全面地推断BER及分析眼图轮廓。在把抖动、噪声和BER分析与8000系列的模块化灵活性、完善的性能和信号保真度结合在一起时,您可以获得理想的下一代高速串行数据设计检验和一致性测试解决方案。下表列出了80SJNB软件配合泰克CSA/TDS8200系列示波器得到的抖动和噪声分析结果。

80SJNB软件除了能够得到每一个抖动和噪声分量的精确结果,针对设计和测试人员还提供了各种图形显示进行更细致的信号完整性分析。例如,抖动和噪声成分概率分布, 频谱分布, 数据相关抖动和噪声与位的关系, 数据码型波形, 抖动和噪声浴缸曲线, BER概率图, BER轮廓图, 概率分布眼图。图5是得到的分析结果。

图5 80SJNB软件得到的分析结果

5. 高速并行总线的眼图测试

对于FPGA芯片提供的高速并行总线,由于其数据传送方式并没有采用内嵌时钟的方法,时钟可以作为触发信号,观测多路并行总线的眼图。由于并行总线的通道数比较多,在示波器中手工测试多通道的眼图比较繁琐,有些传统逻辑分析仪虽然能够直接进行并行总线的眼图测试,但无论是测试精度和速度都无法和示波器进行的标准眼图测试相提并论。

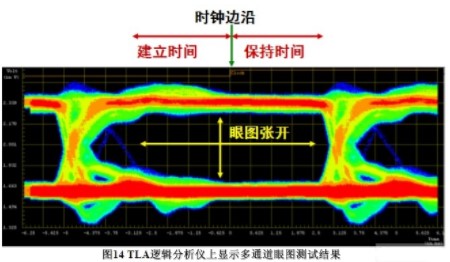

除了能够通过FPGAView对简化FPGA的在线调试,TLA逻辑分析仪能够配合TDS示波器对FPGA外部信号自动进行多通道的眼图测试和分析,该功能称为iVerify眼图测试,最多可以自动的测试408个通道的眼图。

泰克为逻辑分析仪和示波器集成提供了一个信号完整性测试工具包,称为iLink工具包,分为iConnect,iView,以及iVerify眼图测试三个工具。iVerify是建立在iConnect技术和iView技术的基础上,它能够自动对多路并行总线进行眼图测试来彻底验证被测信号。结合iConnect技术,使用一套逻辑分析仪有源探头进行信号逻辑和模拟的同时观测,逻辑分析仪可以将被测通道分成多组,每一组3个数据通道送入到示波器中进行眼图测试,示波器的第4个通道作为外部时钟;采用iView技术,逻辑分析仪可以自动的将每一次送入示波器的3个数据信号的眼图测试数据会传到逻辑分析仪中,这样逻辑分析仪就可以再选择另外一组3个通道进行测试,对于复杂的高速总线,可以一次测试408个数据通道。最后,iVerify技术通过逻辑分析仪将最多408个数据信号的眼图测试数据叠加显示出来,彻底验证总线中出现的信号完整性问题。图6是在TLA逻辑分析仪上自动累计的多个通道眼图数据的色温显示。

图14 TLA逻辑分析仪上显示多通道眼图测试结果

6. 小结

对于FPGA中的高速串行和并行IO信号,需要根据被测信号特点和速度来选择合适的测试和分析工具。当测试信号完整性,希望得到最精确的上升时间,下降时间,信号过冲和震铃等参数,带宽是首要选择。某种意义上带宽越高,测试精度越高。对于实时示波器而言,高速采集内存是眼图和抖动等信号完整性测试的关键。对于采样示波器,通过CSA/TDS8200配合80SJNB抖动和噪声分析软件,不仅可以精确的测量高速串行信号的抖动和噪声,并且能够根据测量结果进行精确的抖动、噪声中每一个分量的分离,和系统的BER相关,最终为信号完整性验证人员提供有价值的信息。当测试高速时钟或数据抖动时,泰克两种示波器都配备业内推荐的抖动测试和分析软件,帮助设计人员得到抖动结果,分析抖动产生的原因,最终得到高可靠性的系统。

-

FPGA测试DDR带宽跑不满的常见原因及分析方法2025-10-15 1246

-

车载总线监控分析及仿真工具 - VBA2025-01-02 1153

-

Verilog 测试平台设计方法 Verilog FPGA开发指南2024-12-17 1937

-

CAN总线测试工具的主要功能2024-06-25 2641

-

Intrepid—总线采集测试仿真工具2022-03-16 1621

-

关于FPGA的高速总线测试和分析2021-05-11 3050

-

车载总线监控分析及仿真工具VBA介绍2021-03-05 3583

-

LED测试程序FPGA工具使用源码2020-12-09 885

-

FPGA设计与调试教程说明2020-09-22 1186

-

如何使用FPGA模拟实现MBUS总线2019-12-24 1295

-

FPGA测试面临哪些挑战?测试方案是什么?2019-08-07 2589

-

汽车CAN/LIN总线测试流程和测试工具解析2010-03-19 8987

-

基于FPGA的USB2.0高速、低成本的虚拟逻辑分析仪的设计2009-06-22 1078

全部0条评论

快来发表一下你的评论吧 !