铝电解电容在高频电路适用性如何选?

电子说

描述

铝电解电容在高频电路中的适用性较差,因其等效串联电阻(ESR)和等效串联电感(ESL)较大,高频下阻抗显著上升,导致性能下降。若需在高频电路中使用铝电解电容,需通过材料革新、结构优化及电路协同设计突破其高频瓶颈,同时结合陶瓷电容等低ESR元件进行补偿。以下为具体分析:

铝电解电容高频性能受限的原因

ESR较高:铝电解电容的阴极采用电解液导电,离子迁移速度远低于电子运动,导致高频下ESR急剧上升。实测数据显示,在100kHz频率下,普通铝电解电容的ESR可达数十毫欧,而相同容量的陶瓷电容仅有个位数毫欧。

ESL较大:传统卷绕式结构产生的寄生电感(ESL)通常在几纳亨到几十纳亨之间。当频率超过1MHz时,感抗(XL=2πfL)将成为阻抗的主要成分。例如,10nH电感在100MHz下的感抗已达6.28Ω,严重削弱电容的退耦效果。

介质损耗增加:铝电解电容的氧化铝介质在高频下介电损耗显著增加,导致信号能量转化为热能的比例上升。某实验室测试表明,在500kHz工作时,标准铝电解的损耗功率可达低频时的3倍以上,这不仅降低效率,还会引发温升导致的寿命衰减。

提升铝电解电容高频性能的方法

材料革新:

导电聚合物阴极:采用聚吡咯(PPy)等导电聚合物作为阴极材料,电子电导率比传统电解液提升5个数量级,使ESR降至传统产品的1/10以下。实测数据显示,100μF/16V的聚合物电容在1MHz下ESR可低至5mΩ,而传统产品通常超过50mΩ。

高纯度蚀刻铝箔:与纳米级阳极氧化技术结合,使介电常数提升30%的同时将介质厚度控制在亚微米级,进一步降低ESR。

结构创新:

四端子设计:通过对称布局将寄生电感降低60%,改善高频性能。

三维结构:如村田的“倒装芯片”铝电解,通过将电极垂直堆叠,使ESL突破性降至1nH以下。

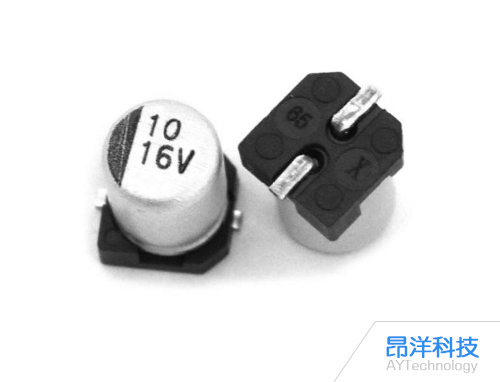

贴片式封装:采用树脂模压封装,相比传统径向封装,ESL降低70%至2nH。

电路协同优化:

容值阶梯策略:将1个100μF铝电解与10个1μF陶瓷电容并联,可使有效频带从100kHz扩展至100MHz。

局部去耦网络:在CPU周围10mm范围内布置0.1μF陶瓷电容阵列,而铝电解负责低频段储能,这种组合使电源噪声降低12dB。

审核编辑 黄宇

-

常规铝电解电容的应用选型2015-11-18 5414

-

固态电解电容如何取代铝电解电容?2017-03-17 3653

-

铝电解电容的应用选型2018-03-12 4494

-

铝电解电容的选取问题2019-05-23 4850

-

铝电解电容进化趋势2019-07-02 2149

-

详解高频电解电容的不同点2019-10-03 2669

-

贴片铝电解电容的选择2020-06-30 2651

-

普通铝电解电容是否可以用高频低阻电解电容替换?2023-04-12 2551

-

铝电解电容器适用指南2010-06-10 1111

-

贴片铝电解电容2016-06-06 1350

-

详解铝电解电容寿命的计算2021-04-28 5138

-

贴片电解电容的标识方法,贴片铝电解电容如何选择型号2023-07-18 15501

-

铝电解电容的用途包括了哪些?2025-07-29 1437

-

铝电解电容的 “高频响应瓶颈”:在高速电路中如何突破局限?2025-08-08 1220

-

数控机床主轴驱动铝电解电容 高频响应2025-12-10 562

全部0条评论

快来发表一下你的评论吧 !