基于应用SiC模块的固态变压器(SST)控制架构与DSP实现报告

电子说

描述

基于应用SiC模块的固态变压器(SST)控制架构与DSP实现报告

BASiC Semiconductor基本半导体一级代理商倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 绪论

1.1 固态变压器技术演进与应用背景

随着智能电网(Smart Grid)概念的深化以及分布式可再生能源(DERs)渗透率的提升,传统的工频变压器(LFT)因其体积庞大、缺乏可控性以及无法直接处理直流负载等局限性,正面临着技术革新的迫切需求。固态变压器(Solid State Transformer, SST),亦称为电力电子变压器(PET),作为一种集成了高频变压器与功率半导体变换器的能量路由设备,凭借其高功率密度、电能质量调节能力以及交直流混合接口特性,成为了配电网现代化的核心装备

在SST的发展历程中,半导体器件的性能始终是制约其电压等级与转换效率的关键瓶颈。传统的硅(Si)基IGBT虽然技术成熟,但其开关损耗限制了SST的工作频率(通常低于10 kHz),导致高频变压器的体积缩小优势无法充分发挥。近年来,以碳化硅(SiC)为代表的宽禁带(WBG)半导体技术的商业化成熟,为SST带来了革命性的突破。SiC MOSFET具有更高的击穿电场、更高的热导率以及极低的开关损耗,使得SST能够在数十千赫兹甚至上百千赫兹的频率下运行于中压(MV)配电网环境,同时保持极高的系统效率。

1.2 SiC模块在SST中的关键作用

倾佳电子杨茜将重点围绕应用SiC功率模块的SST展开,特别是针对中压配电网(如10 kV或13.8 kV)的主流拓扑架构——级联H桥(Cascaded H-Bridge, CHB)整流级与双有源桥(Dual Active Bridge, DAB)隔离DC-DC级的组合。选用的核心参考器件为BASiC Semiconductor(基本半导体)的Pcore™2系列SiC MOSFET模块(如BMF240R12KHB3,1200V/240A),该类器件代表了当前工业界在低电感封装与高频开关性能方面的先进水平。

SiC模块的引入不仅提升了硬件性能,更对数字控制系统提出了严苛的挑战。纳秒级的开关速度(如BMF240R12KHB3的开通延迟仅约65ns)要求控制算法具备极高的执行效率与精确的时序管理能力。数字信号处理器(DSP),特别是Texas Instruments的C2000系列(如TMS320F28379D, F280049C),凭借其高分辨率PWM(HRPWM)、控制律加速器(CLA)以及可配置逻辑块(CLB)等专用外设,成为了实现SiC SST复杂控制策略的首选平台。

1.3 报告范围与结构

倾佳电子杨茜剖析基于SiC模块的固态变压器SST的主流控制算法及其在DSP上的底层代码实现。倾佳电子杨茜将涵盖从系统级拓扑分析、SiC器件特性对控制参数的影响,到具体的AC/DC与DC/DC级控制策略(如SRF-PLL、电压平衡排序算法、SPS移相控制),以及系统级的软启动与保护逻辑。文中将通过详细的C语言代码片段、寄存器配置说明以及算法流程图,展示如何将理论控制策略转化为工业级的嵌入式软件。

2. SST拓扑架构与SiC器件特性分析

2.1 级联型SST拓扑解析

针对中压交流(MVAC)到低压直流(LVDC)的应用场景,模块化多电平级联拓扑是目前工业界的主流选择。该架构主要由三个功率变换阶段组成:

高压交流/直流级(MV AC/DC): 采用级联H桥(CHB)整流器。由于单管SiC MOSFET的耐压通常限制在1.2 kV - 3.3 kV,直接通过单级变换器连接10 kV电网是不现实的。CHB拓扑通过将多个低压功率单元(Power Electronic Building Block, PEBB)在交流侧串联,能够分担高压应力,并合成出多电平阶梯波,显著降低网侧电流谐波THD。

隔离直流/直流级(MV DC/LV DC): 采用输入串联输出并联(ISOP)的双有源桥(DAB)变换器。每个CHB单元的直流母线后端连接一个DAB模块。DAB通过高频变压器实现电气隔离与电压匹配,并利用漏感实现能量传输。其核心优势在于能够实现全负载范围内的零电压开通(ZVS),与SiC器件的高频特性相得益彰。

低压直流/交流级(LV DC/AC): (可选)若需连接低压交流负载或并入低压微网,可在低压直流母线后级联逆变器。

2.2 SiC MOSFET模块的关键电气特性

在设计DSP控制算法之前,必须深入理解所选SiC模块的电气特性,因为这些参数直接决定了死区时间、驱动保护阈值以及热保护逻辑的设定。以BASiC BMF240R12KHB3(1200V, 240A)为例:

2.2.1 开关动态特性与死区设置

SiC MOSFET的开关速度远快于同等级的Si IGBT。根据数据手册5:

开通延迟时间(td(on)): 典型值为65 ns(@25°C)至56 ns(@175°C)。

上升时间(tr): 典型值为37 ns(@25°C)。

关断延迟时间(td(off)): 典型值为110 ns(@25°C)至124 ns(@175°C)。

下降时间(tf): 典型值为36 ns(@25°C)。

控制启示: 总的开关转换过程在200ns以内。这意味着在DSP的PWM配置中,死区时间(Dead-Time)必须设置得足够小以减少体二极管导通带来的损耗(SiC体二极管压降较高,约3-4V),但又必须大于器件的关断延迟与驱动回路传输延迟之和以防止直通。传统的微秒级死区在SiC应用中是不可接受的,通常需要设置在300ns至500ns之间。

2.2.2 栅极驱动与内部电阻

该模块的内部栅极电阻(RG(int))典型值为2.85 Ω。由于SiC MOSFET的跨导特性,其对栅极振荡较为敏感。DSP输出的PWM信号在经过隔离驱动芯片(如UCC21732)时,必须匹配合适的外部栅极电阻,并在代码中配置消隐时间(Blanking Time)以避免由于高dv/dt导致的误触发保护。

2.2.3 热特性与NTC传感器

模块内部集成了NTC热敏电阻用于温度监测。由于SiC器件具有极高的功率密度,结温上升极快,DSP必须通过ADC实时采样NTC电压,并利用Steinhart-Hart方程或查表法快速计算结温,实现过温保护(OTP)。

3. 分布式数字控制系统架构

鉴于SST包含数十甚至上百个开关器件,单一控制器难以满足实时性要求。主流方案采用“主控制器(Master)+ 从控制器(Slave)”的分布式架构。

3.1 硬件层级划分

主控制器(Master Controller):

核心任务: 负责系统级能量管理、电网同步(PLL)、功率分配、人机交互以及与上层调度系统的通讯。

硬件选型: 通常采用高性能多核DSP(如TMS320F28388D)或FPGA+DSP组合。

从控制器(Slave Controller):

核心任务: 负责单个PEBB(包含一个H桥和一个DAB)的具体控制,包括高频PWM生成、本地电流/电压采样、保护逻辑执行以及DAB的移相控制。

硬件选型: 高性价比实时MCU(如TMS320F280049C或F280039C),具备高分辨率PWM和快速ADC。

3.2 通讯架构

主从之间通常通过高速串行总线连接:

CAN/CAN-FD: 用于下发功率指令和上传状态信息,抗干扰能力强,适合工业环境15。

FSI (Fast Serial Interface): TI C2000系列特有的高速接口,用于在隔离域之间传输极低延迟的同步信号和保护信号。

PWM同步信号: 物理层面的同步脉冲,确保所有级联单元的三角载波相位严格对齐或按规律移相(载波移相SPWM)。

4. AC/DC级控制算法与DSP实现

CHB整流器的控制目标是维持直流母线电压稳定,并控制网侧电流为正弦且与电网电压同相(单位功率因素)。

4.1 软件锁相环(SRF-PLL)

为了实现坐标变换(Park变换),必须准确获取电网电压的相位角θ。在三相系统中,同步旋转坐标系锁相环(SRF-PLL)是标准方案。

4.1.1 算法原理

将采集的三相电压vabc通过Clarke变换得到vαβ,再通过Park变换得到vdq。利用PI控制器调节vq分量至0,PI控制器的输出即为电网角频率偏差Δω,叠加额定频率ω0后积分即可得到相位θ。

4.1.2 DSP C代码实现

在C2000 DSP中,PLL算法通常在ADC中断服务程序(ISR)中执行。为了提高计算效率,利用DCL(Digital Control Library)库18。

C

// 定义PLL结构体

typedef struct {

float32_t v_q; // q轴电压反馈

float32_t theta; // 输出相位角 (0 ~ 2*PI)

float32_t omega; // 当前角频率

float32_t omega_nom; // 额定角频率 (如 2*PI*50)

DCL_PI pi_reg; // PI控制器对象

float32_t sin_theta; // sin(theta) 缓存

float32_t cos_theta; // cos(theta) 缓存

} SPLL_3PH_SRF;

// PLL 初始化

void SPLL_Init(SPLL_3PH_SRF *spll) {

spll->omega_nom = 2.0f * 3.1415926f * 50.0f; // 50Hz

spll->theta = 0.0f;

// 初始化PI参数 (需根据带宽设计,例如带宽20Hz)

spll->pi_reg.Kp = 166.32f;

spll->pi_reg.Ki = 165.68f;

DCL_resetPI(&spll->pi_reg);

}

// PLL 运行函数 (在ISR中调用)

// Ts 为采样周期

inline void SPLL_Run(SPLL_3PH_SRF *spll, float32_t v_q_meas, float32_t Ts) {

// 1. 运行PI控制器调节 Vq -> 0

// 注意:PI的误差输入应为 (Ref - Meas) = (0 - v_q_meas) = -v_q_meas

float32_t loop_out = DCL_runPI(&spll->pi_reg, 0.0f, v_q_meas);

// 2. 频率计算

spll->omega = spll->omega_nom + loop_out;

// 3. 角度积分

spll->theta += spll->omega * Ts;

// 4. 角度归一化 (0 ~ 2*PI)

if (spll->theta > 6.2831853f) {

spll->theta -= 6.2831853f;

} else if (spll->theta < 0.0f) {

spll->theta += 6.2831853f;

}

// 5. 计算三角函数供Park变换使用 (利用TMU硬件加速)

spll->sin_theta = __sin(spll->theta);

spll->cos_theta = __cos(spll->theta);

}

深度分析: 在SiC应用中,由于高dv/dt可能导致ADC采样噪声,直接输入vq可能导致PLL抖动。在实际工程代码中,通常会在输入端增加软件陷波器(Notch Filter)滤除2倍工频纹波,或使用滑动平均滤波器20。

4.2 电压定向电流控制(VOC)

CHB采用双闭环控制:外环为总直流电压环,内环为网侧电流环。

电压环: 对比总直流电压参考值与采样值,PI输出为有功电流参考id∗。

电流环: 在dq坐标系下对id,iq进行解耦控制。

DSP实现要点:

由于CHB是多电平,电流环的输出vd,ref,vq,ref经过反Park变换得到vα,ref,vβ,ref后,不能直接发给PWM,而是作为调制波(Modulation Wave),需要结合均压算法分配给各个H桥单元。

4.3 级联单元均压策略:排序算法(Sorting Algorithm)

CHB正常工作的前提是各单元直流电容电压均衡。均压控制是CHB算法中最耗资源的部分。最有效的方法是基于气泡排序(Bubble Sort)的策略23。

算法逻辑:

采样: 获取该相所有单元的电容电压vdc,1,vdc,2,...,vdc,N。

排序: 将电压从低到高(或从高到低)排序。

分配:

若电流igrid>0(充电方向):优先导通电压最低的单元,使其充电更多。

若电流igrid<0(放电方向):优先导通电压最高的单元,使其放电更多。

C代码实现与优化:

对于N较大的系统(如N>5),全排序耗时较长。在C2000上,可以利用指针数组进行间接排序,避免大量数据搬移。

C

#define NUM_CELLS 7

typedef struct {

uint16_t cell_id;

float32_t voltage;

uint16_t active_status; // 1:投入, 0:切除

} Cell_Obj;

Cell_Obj Cell_Array;

Cell_Obj* pSorted_Cells; // 指针数组,用于排序

// 气泡排序实现 (按电压从小到大)

void Voltage_Sort(void) {

int i, j;

Cell_Obj* temp;

// 初始化指针

for(i=0; i

// 排序逻辑

for (i = 0; i < NUM_CELLS - 1; i++) {

for (j = 0; j < NUM_CELLS - i - 1; j++) {

if (pSorted_Cells[j]->voltage > pSorted_Cells[j + 1]->voltage) {

// 交换指针

temp = pSorted_Cells[j];

pSorted_Cells[j] = pSorted_Cells[j + 1];

pSorted_Cells[j + 1] = temp;

}

}

}

}

// 均压分配逻辑 (在电流环ISR中调用)

void Balance_And_Assign_PWM(float32_t i_grid, uint16_t num_cells_to_on) {

Voltage_Sort(); // 先排序

// 清除所有状态

for(int k=0; k

if (i_grid > 0) {

// 充电:选电压最低的 num_cells_to_on 个单元

for(int k=0; k

pSorted_Cells[k]->active_status = 1;

}

} else {

// 放电:选电压最高的 num_cells_to_on 个单元

// 即数组末尾的单元

for(int k=0; k

pSorted_Cells->active_status = 1;

}

}

// 更新PWM寄存器

Update_PWM_Based_On_Status();

}

数据分析与洞察: 排序算法虽然逻辑简单,但执行时间随单元数平方增长。对于20kHz的开关频率,DSP可能无法在单周期内完成所有计算。因此,工程上常采用降频排序策略(例如每5或10个PWM周期执行一次排序),或者利用CLA协处理器并行处理排序任务,主CPU只负责读取结果和更新PWM25。

5. DC/DC级控制算法与DSP实现

DAB是SST的核心功率传输级,其控制主要围绕**单移相(Single Phase Shift, SPS)**调制展开。

5.1 单移相控制(SPS)原理

SPS控制通过调节原边全桥与副边全桥输出电压之间的相位差ϕ来控制传输功率。

P=2πfswLnV1V2ϕ(1−π∣ϕ∣)

其中ϕ为弧度制。

5.2 基于C2000的高精度相位控制

在100 kHz的高频下,能够调节的相位精度直接决定了功率控制的分辨率。C2000的**高分辨率PWM(HRPWM)**模块在此至关重要。标准PWM在100 MHz时钟下,100 kHz开关频率只有1000个计数点,分辨率仅为0.1%。HRPWM利用微边沿定位技术(MEP),可将分辨率提升至150 ps级别26。

5.2.1 硬件配置

ePWM1 (Primary): 配置为主模块(Master),SYNCOSEL = CTR_ZERO。

ePWM2 (Secondary): 配置为从模块(Slave),PHSEN = 1。

5.2.2 移相更新代码示例

传统的ePWM模块在更新TBPHS(相位寄存器)时没有影子寄存器(Shadow Register),可能导致波形抖动。F2837x及更新型号支持TBPHS的影子加载或利用**全局加载(Global Load)**功能同步更新27。

C

// 计算移相值并更新

// phase_pu: -1.0 到 1.0 对应 -180度 到 180度

void DAB_Update_Phase(float32_t phase_pu) {

uint32_t period_ticks = EPwm1Regs.TBPRD;

int32_t phase_ticks;

// 计算计数值

phase_ticks = (int32_t)(phase_pu * (float32_t)period_ticks);

// 限制范围

if(phase_ticks > period_ticks) phase_ticks = period_ticks;

if(phase_ticks < -((int32_t)period_ticks)) phase_ticks = -((int32_t)period_ticks);

EALLOW;

// 处理正负移相 (超前/滞后)

// 注意:TBPHS寄存器是无符号的,方向由TBCTL.PHSDIR控制

if (phase_ticks >= 0) {

EPwm2Regs.TBCTL.bit.PHSDIR = 1; // Count Up after Sync (Lag)

EPwm2Regs.TBPHS.bit.TBPHS = (uint16_t)phase_ticks;

} else {

EPwm2Regs.TBCTL.bit.PHSDIR = 0; // Count Down after Sync (Lead)

EPwm2Regs.TBPHS.bit.TBPHS = (uint16_t)(-phase_ticks);

}

// 触发全局加载,确保在下一个周期起始点同步生效

EPwm2Regs.GLDCTL2.bit.OSHTLD = 1;

EDIS;

}

5.3 变压器偏磁抑制(Flux Balancing)

DAB的高频变压器容易因驱动脉冲不对称或采样误差产生直流偏磁,导致磁芯饱和。在SST中,必须引入磁通平衡控制。

控制逻辑: 采样原边电流,通过低通滤波器(或滑动平均)提取直流分量Idc。将该分量送入PI控制器,输出修正量Δϕ或ΔD,叠加到SPS的控制量上。

C

// 偏磁抑制代码片段 (运行在CLA或主CPU ISR)

// i_prim_meas: 原边电流采样值

static float32_t i_dc_accum = 0;

float32_t i_dc_avg;

// 滑动平均提取直流分量

i_dc_accum = (i_dc_accum * 0.99f) + (i_prim_meas * 0.01f);

i_dc_avg = i_dc_accum;

// PI控制抑制直流分量

float32_t offset_comp = DCL_runPI(&dc_suppression_pi, 0.0f, i_dc_avg);

// 将偏置量应用到PWM占空比或相位微调

// 方式:微调CMPA/CMPB使正负半周不对称,抵消直流偏置

EPwm1Regs.CMPA.bit.CMPA = Nominal_CMPA + (int16_t)offset_comp;

EPwm1Regs.CMPB.bit.CMPB = Nominal_CMPB - (int16_t)offset_comp;

6. SiC专用保护与软启动策略

6.1 软启动状态机(Soft-Start State Machine)

SST直接启动会产生巨大的冲击电流,损坏SiC模块或电容。必须设计严格的软启动序列。

状态机流程:

预充电(Pre-charge): 闭合交流侧预充电电阻回路,CHB不发波,直流母线通过二极管整流自然充电。

DAB开环软启(DAB Open Loop): 直流电压稳定后,旁路预充电电阻。DAB开始以极小的占空比或移相角发波,逐步建立低压侧电压。

闭环切换(Closed Loop Handover): 当低压侧电压接近设定值,初始化PI控制器积分项(预置位),无缝切换到闭环控制模式。

代码实现:

C

typedef enum {

STATE_IDLE,

STATE_AC_PRECHARGE,

STATE_DAB_RAMP_UP,

STATE_RUNNING,

STATE_FAULT

} SystemState_t;

void SST_State_Machine(void) {

static float32_t dab_phase_ramp = 0.0f;

switch(CurrentState) {

case STATE_AC_PRECHARGE:

if (V_dc_total > V_PRECHARGE_TARGET) {

GPIO_setHigh(RELAY_BYPASS_PIN); // 旁路电阻

CurrentState = STATE_DAB_RAMP_UP;

}

break;

case STATE_DAB_RAMP_UP:

// 缓慢增加移相角

dab_phase_ramp += 0.0005f;

DAB_Update_Phase(dab_phase_ramp);

if (V_out >= V_NOMINAL * 0.9f) {

// 预置PI积分器,防止切换冲击

pi_voltage.i10 = dab_phase_ramp;

CurrentState = STATE_RUNNING;

}

break;

case STATE_RUNNING:

// 执行正常的闭环控制

Run_Voltage_Loop();

break;

}

}

6.2 硬件级保护:Trip Zone配置

SiC MOSFET抗短路能力较差(短路耐受时间SCWT通常< 3μs),传统的软件保护来不及响应。必须利用C2000的Trip Zone (TZ) 模块直接联动驱动器的DESAT(退饱和)故障信号。

配置逻辑:

将驱动器的FAULT引脚连接到DSP的TZ引脚(如GPIO12)。配置TZ为**单次触发(One-Shot, OSHT)**模式,一旦检测到低电平(或高电平),硬件立即将PWM置为低电平(封锁脉冲),无需CPU干预。

C

void Init_Protection(void) {

EALLOW;

// 1. 将GPIO12配置为TZ1输入 (连接到驱动器DESAT Fault)

InputXbarRegs.INPUT1SELECT = 12;

// 2. 配置ePWM模块响应TZ1

EPwm1Regs.TZSEL.bit.OSHT1 = 1; // 启用TZ1作为单次触发源

// 3. 配置触发动作:强制输出低电平 (保护SiC)

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

// 4. 启用TZ中断 (用于通知CPU记录故障)

EPwm1Regs.TZEINT.bit.OST = 1;

EDIS;

}

// 故障中断服务程序

interrupt void TZ_ISR(void) {

EALLOW;

// 清除标志位,记录故障时间

EPwm1Regs.TZCLR.bit.INT = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP2;

EDIS;

// 切换状态机到故障状态

CurrentState = STATE_FAULT;

}

6.3 NTC温度检测算法

针对BMF240R12E2G3等模块,准确的温度读取是热保护的关键。NTC电阻随温度非线性变化,需使用Steinhart-Hart方程。

T1=A+Bln(R)+C(ln(R))3

由于log和立方运算在ISR中耗时较多,实际工程中常预先计算生成查找表(Look-up Table, LUT) ,在代码中通过线性插值快速获取温度,兼顾精度与效率。

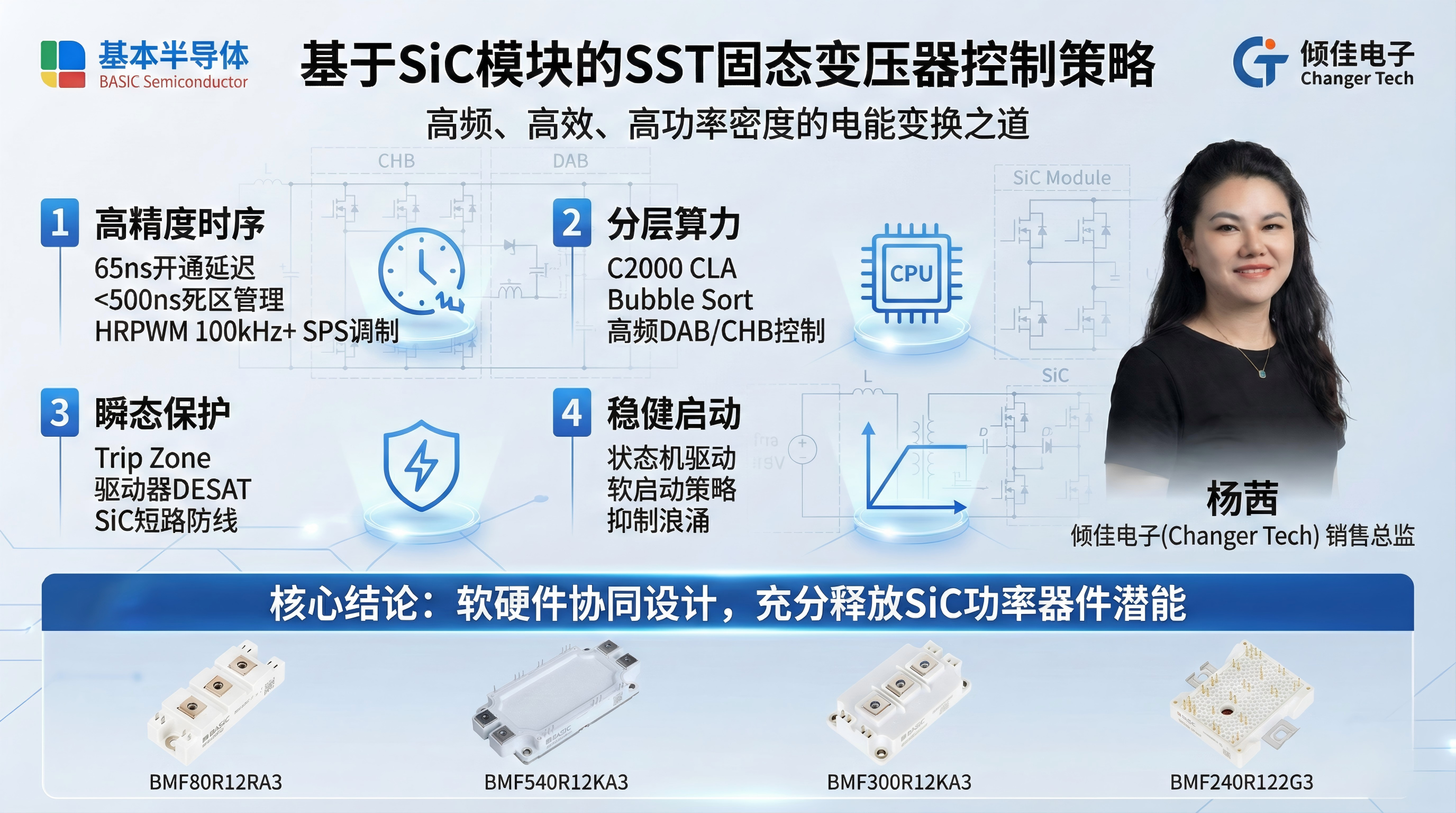

7. 结论

基于SiC模块的SST固态变压器的控制是一个高度复杂的系统工程,涉及多层级的控制策略与毫秒级至纳秒级的时序管理。倾佳电子杨茜详细阐述了基于TI C2000 DSP的实现方案,核心结论如下:

SiC特性决定控制细节: 65ns的开通延迟和极低的开关损耗要求控制软件必须实现高精度的死区管理(<500ns)和高频SPS调制(>100kHz),这必须依赖HRPWM等专用外设。

分层架构是必然选择: CHB的均压排序算法与DAB的高频移相控制对算力要求极高,利用CLA分担高频计算任务、利用Bubble Sort优化算法效率是系统稳定运行的关键。

保护必须硬件化: 面对SiC脆弱的短路承受能力,依靠Trip Zone和驱动器DESAT的硬件直连保护机制是不可或缺的最后一道防线。

软启动不可忽视: 状态机驱动的分阶段软启动策略能有效抑制浪涌电流,防止变压器饱和与器件损坏。

通过上述软硬件协同设计,SST能够充分释放SiC功率器件的潜能,实现高效、高功率密度的电网电能变换。

| 章节 | 关键技术点 | 涉及代码/算法 | 硬件资源 |

|---|---|---|---|

| AC/DC | 电网同步 | SRF-PLL | ADC, PI |

| AC/DC | 电压平衡 | 气泡排序 (Bubble Sort) | CPU/CLA |

| DC/DC | 功率传输 | SPS移相控制 | ePWM (HRPWM), Global Load |

| DC/DC | 偏磁抑制 | 直流分量提取与补偿 | ADC, PI |

| System | 保护 | DESAT联动 | Trip Zone (TZ), GPIO |

| System | 启动 | 多阶段软启动状态机 | State Machine |

审核编辑 黄宇

-

固态变压器SST的拓扑架构深度解析与基本半导体SiC模块的工程应用研究2025-12-16 4263

-

SST固态变压器中NPC三电平架构的演进与SiC功率模块应用优势研究报告2026-01-11 1851

-

固态变压器SST配套SiC功率模块直流固态断路器的技术发展趋势2026-01-20 1321

-

固态变压器(SST)架构中高频 DC/DC 核心器件:国产 SiC 模块、驱动板与高频隔离变压器2026-01-26 539

-

62mm SiC半桥模块与双通道SiC驱动板设计固态变压器(SST)功率单元2026-02-20 4374

-

62mm半桥SiC模块设计固态变压器 (SST) DAB的工程落地2026-02-27 630

-

SiC模块构建固态变压器(SST)的 AC-DC 级方案及优势2026-02-28 1315

-

250kW固态变压器(SST)子单元设计方案-ED3封装SiC模块2026-03-05 490

-

能源互联网的基石:固态变压器(SST)与基于SiC模块的双向DAB拓扑解析2026-03-13 746

-

应对电网短路:具备“主动自愈”功能的35kV级基于SiC模块的固态变压器(SST)控制架构深度研究报告2026-03-21 873

-

基于双有源桥(DAB)的SiC固态变压器中间级:高频变压器偏磁饱和与控制算法2026-03-27 450

-

固态变压器(SST)谐振腔设计:利用主变压器漏感完全取代谐振电感2026-04-04 548

-

固态变压器(SST)AC-DC环节采用SiC模块高频整流的技术与商业逻辑综合报告2026-04-07 453

-

嵌入式磁集成:SST固态变压器PEBB内部80%寄生电感消除与电磁辐射抑制2026-04-14 163

-

“无极性”直流母排在基于SiC模块级联型SST固态变压器PEBB中的应用2026-04-19 34

全部0条评论

快来发表一下你的评论吧 !