零延迟时钟频率合成器技术应用分解

描述

零延迟指的是时钟频率合成器能够提供与时钟参考源边沿对齐的输出信号,其应用包括许多同步系统,如SONET和SDH网络、高速网络服务器、网络线路卡以及用于W-CDMA和Wi-Fi的基带定时等。

零延迟架构

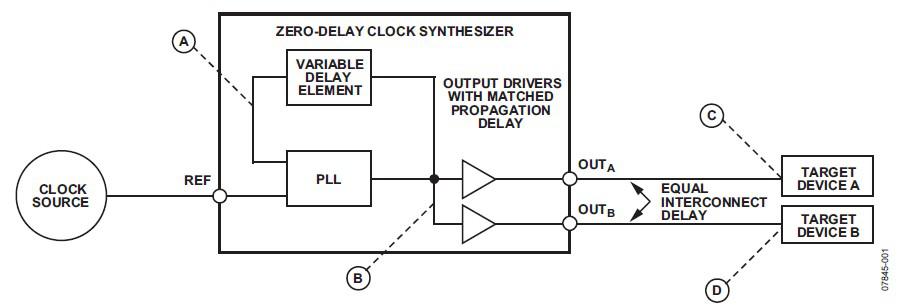

集成零延迟时钟频率合成器至少需要三个构建模块(见图1)。第一个构建模块是锁相环(PLL),它可以是常见的模拟类型或较新型的全数字设计。第二个构建模块是具有匹配传播延迟的两个(或更多)输出驱动器。第三个构建模块是PLL反馈路径中的可变延迟元件。此外,零延迟架构要求从合成器输出到关联目标器件的互连延迟等同。等同的互连延迟是零延迟架构的基本组成部分,没有它,目标器件将无法实现时钟沿对齐。

图1. 通用零延迟频率合成器

零延迟操作

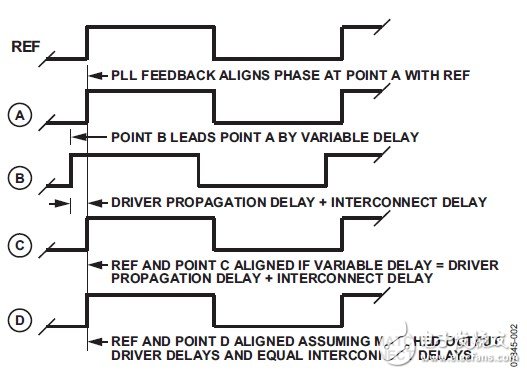

要了解零延迟操作,请参考图2,它是图1所示零延迟架构的时序图。注意,PLL的动作使得A点的时钟沿与REF时钟沿对齐。可变延迟元件位于PLL反馈路径中,这意味着B点的时钟沿比A点的时钟沿提前一个可变延迟量。

图2. 零延迟时序图

将可变延迟设置为输出驱动器传播延迟与互连延迟之和,这样C点的时钟沿就与A点的时钟沿重合,而A点的时钟沿与REF时钟沿重合,因此,REF与目标器件A的时钟沿对齐。此外,由于输出驱动器共享同一输入信号,并且该信号在经过各驱动器和各互连时均发生相同的延迟,因此REF时钟沿不仅与目标器件A的时钟沿对齐,而且与目标器件B的时钟沿对齐。事实上,只要所有驱动器表现出相同的传播延迟,并且所有互连具有相同的延迟,就可以将上述概念扩展到所需的许多输出。

图2中的时序图显示,PLL提供的频率转换比为1(即fREF = fOUT),这可以简化说明,但并不是必需的。事实上,任何能够提供整数(或整数倒数)输出/输入频率比的倍频或分频系数都是可以接受的。一般而言,输入和输出信号的频率必须谐波相关,时钟沿对齐才有意义。

必须注意,"零延迟"的适用对象是相对时间,而不是绝对时间。图2清楚地显示,可变延迟元件导致B点的时钟沿先于REF时钟沿。显然,在绝对时间中,时间无法倒流,B点的时钟沿不可能先于REF时钟沿。事实上,B点的绝对时钟沿至少比REF时钟沿落后一个完整的时钟周期(减去可变延迟)。在实际的定时应用中,时钟沿只需要相对于参考时钟对齐,因此使用"零延迟"这一术语完全妥当。

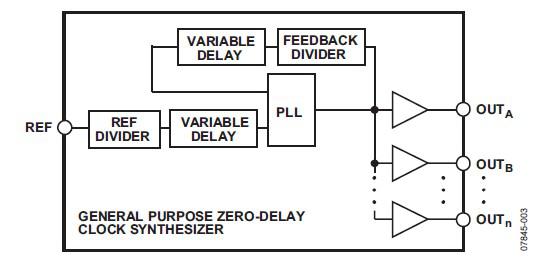

图1用于说明零延迟架构的概念是有益的,但要作为一种集成解决方案,它是有局限性的。更一般的解决方案是在PLL的REF和反馈路径中各包括一个可编程分频器(见图3)。利用REF和反馈分频器,单一器件就能设置不同的输入/输出频率比,从而满足许多应用的需求。然而,对于零延迟应用,只有谐波相关的输入/输出频率比才是有意义的。注意,REF路径中出现了第二个可变延迟单元,其主要作用是对REF分频器造成的延迟进行边沿时序补偿。

图3. 通用零延迟频率合成器

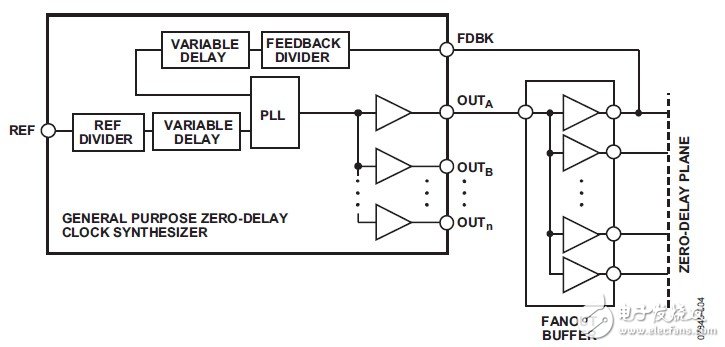

通用零延迟架构的进一步扩展是从外部访问PLL反馈路径,这将使得零延迟架构能够支持外部扇出缓冲器,如图4所示。

图4. 外部零延迟架构

集成解决方案

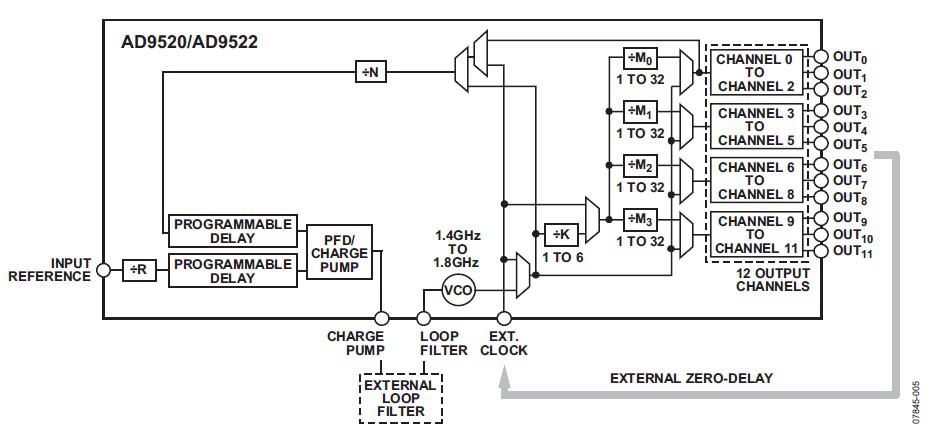

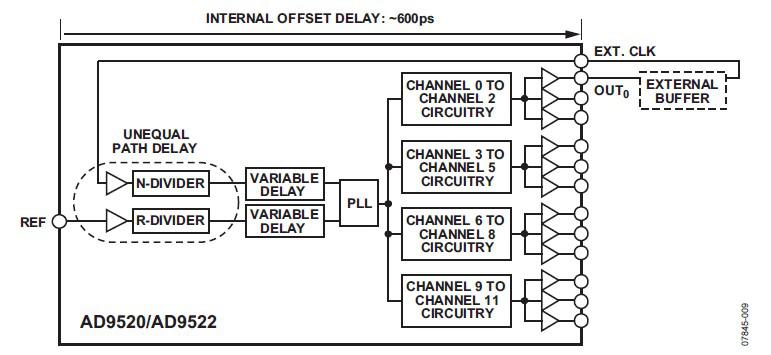

AD9520和AD9522是通用时钟频率合成器,能够为许多应用提供集成零延迟解决方案。两款器件的唯一区别是AD9520采用LVPECL输出驱动器,AD9522则采用LVDS驱动器。任一款器件的输出驱动器都可以编程为CMOS.图5所示为AD9520/AD9522的功能框图。

图5. AD9520/AD9522功能框图

该器件具有一个串行编程接口,支持广泛的时钟合成解决方案,灵活的架构同时支持内部和外部零延迟应用。AD9520/AD9522的PLL部分由PFD/电荷泵、外部环路滤波器和集成VCO(带可选K分频器)组成。R分频器为参考分频器,N分频器为反馈分频器。每个分频器后置一个可编程延迟单元。两个可编程延迟单元均以大约120 ps的步进提供大约1100 ps的延迟调整。AD9520/AD9522具有12个输出驱动器(通道0至通道11),分为4组,每组包括三个驱动器。此外,各组通道都能访问可选的通道分频器(M0至M3)。

通道分频器提供额外的分频功能,增强了器件在频率合成应用中的灵活性。除分频外,通道分频器还提供边沿时序

粗调功能。各通道分频器的输出边沿时序是可编程的,编程步进为ΔT(最多32步),其中ΔT = 1/fCLK,fCLK为通道分频器的输入频率。

通道分频器虽然增强了AD9520/AD9522的频率合成能力,但也使涉及零延迟的应用更加复杂,原因是零延迟架构要求从PLL输出端到各输出驱动器输入端的延迟等同,通道分频器的存在破坏了这种延迟等同性,除非用户采取适当的措施。具体而言,对于任何用来执行零延迟功能的通道必须同等对待。也就是说,如果一组零延迟输出采用通道分频器,则其他零延迟输出也必须采用通道分频器。此外,必须对零延迟输出相关的所有通道分频器应用相同的分频和延迟值。这些措施可以确保所有通道从PLL输出端到各通道驱动器输出端的延迟相同(至少通道之间的内部延迟匹配)。

时序误差:偏斜和偏移

理论上,如果外部互连延迟完全一致,则出现在零延迟平面的时钟信号与REF信号边沿对齐。然而,实际应用中通常存在两类时序误差。一类是时序偏斜,它是指边沿对齐存在细微的偏差,这些偏差随机分布于多个时钟信号中。另一类是时序偏移,它是指边沿对齐的恒定偏移(相对于REF信号),对所有输出时钟信号都相同。

时序偏斜的一个误差源是器件本身。器件各输出通道的传播延迟存在细微的差异,这是内部时序偏斜产生的原因。虽然AD9520/AD9522的设计人员力图将时序偏斜降至最小,但仍存在一些无法避免的偏差。时序偏斜的另一个是外部互连的物理或电气长度存在细微的误差。

在这两个时序偏斜源中,内部偏斜源相比于外部偏斜源通常可以忽略不计。当使用AD9520 LVPECL输出时,情况更是如此,所有通道间的偏斜只有大约50 ps.即便使用AD9520/AD9522 CMOS或AD9522 LVDS输出,所有通道间的偏斜分别也只有大约300 ps或200 ps.然而,如果用

户努力通过设计消除外部偏斜,那么内部偏斜就可能成为主要的偏斜源。应当注意,在实际应用中,一定量的时序偏斜是不可避免的,设计人员必须确定特定应用的最大容许时序偏斜,然后据此进行设计。

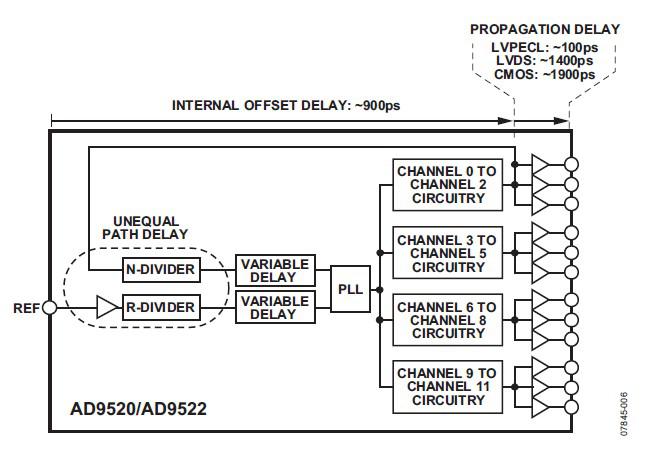

另一类时序误差,即时序偏移,在AD9520/AD9522的内部和外部零延迟架构中具有不同的表现。对于内部架构,需要考虑两点(见图6)。第一,输出驱动器位于PLL反馈路径外部,因此其传播延迟表现为相对于REF信号的时序偏移。对于AD9520 LVPECL驱动器,该偏移量约为100 ps,AD9522 LVDS驱动器约为1400 ps,AD9520/AD9522 CMOS驱动器约为1900 ps.第二点考虑涉及到REF与反馈驱动器路径之间的固有延迟不匹配,原因是N分频器与R分频器存在根本上的区别,导致延迟不匹配。此外,REF路径包括一个时钟接收器级,因此REF路径的延迟比反馈路径多出大约900 ps(假设可变延迟单元被旁路或具有相同的延迟值),这意味着LVPECL、LVDS和CMOS输出的总不可调整偏移分别为1000 ps、2300 ps和2800 ps.

图6. AD9520/AD9522内部零延迟时序偏移误差

通过旁路REF路径中的可变延迟单元,并且使能反馈路径中的可变延迟单元,可以减小该固有偏移。反馈路径中的可变延迟单元提供1100 ps的调整范围,因此全部1000 ps的固有偏移(使用LVPECL输出时)都能得以消除。然而,当使用LVDS或CMOS输出时,偏移仅可减小到大约1200 ps或1700 ps(固有偏移超出最大调整范围的量)。任何情况下,设计人员必须确保残余时序偏移不超过特定应用的最大容许限值。

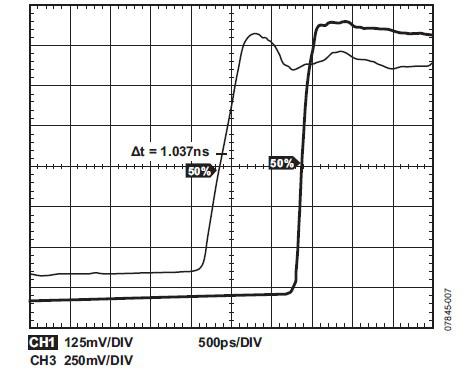

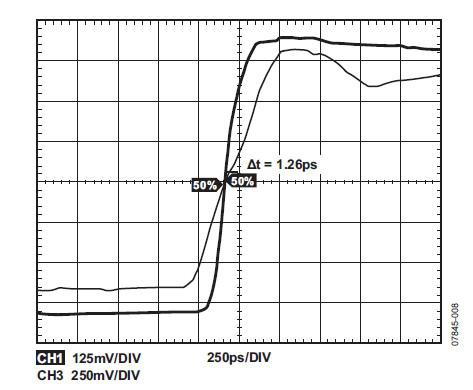

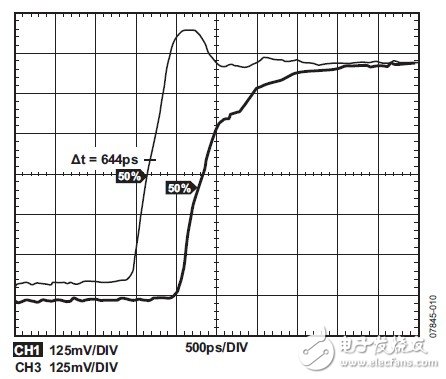

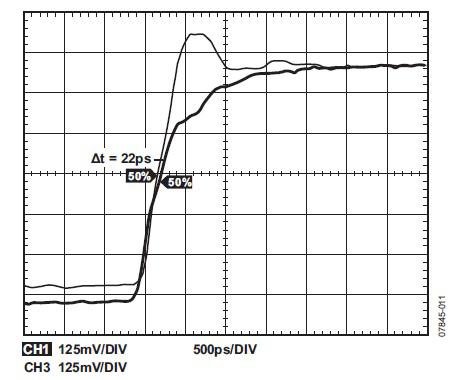

图7和图8所示为使用内部零延迟架构的实际时域测量结果。这些图证明,使用AD9520 LVPECL输出时,时序偏移几乎被完全消除。测量使用匹配的探针进行,探针直接连接到器件的REF输入和OUT1引脚。

图7. 内部零延迟固有偏移时序误差(AD9520)

图8. 内部零延迟调整后的偏移时序(AD9520)

使用外部零延迟架构时,驱动器(及任何外部缓冲器)包括在PLL的反馈路径中,因此输出驱动器的传播延迟对偏移时序误差无影响(见图9)。PLL能够有效吸收OUT0缓冲器(任选)的传播延迟和经过外部电路的延迟。然而,像内部零延迟架构一样,REF与反馈驱动器路径之间仍然存在固有的延迟不匹配,此外,对于外部架构,外部时钟输入需要一个时钟接收器(显示于N分频器的输入端)。整体偏移延迟为600 ps,比内部架构少300 ps,原因是外部时钟输入接收器具有额外的延迟。

图9. AD9520/AD9522外部零延迟时序偏移误差

由于固有偏移时序误差仅为600 ps,因此可以将反馈路径的可变延迟设置得比REF路径的可变延迟大600 ps,从而消除误差。当然,可变延迟单元的粒度为120 ps,这意味着仍可能有最多60 ps的残余偏移。因此,设计人员必须确保最多60 ps的残余时序偏移不超过特定应用的最大容许限值。

图10和图11所示为使用外部零延迟架构的实际时域测量结果,证明时序偏移误差几乎被完全消除。测量使用匹配的探针进行,探针直接连接到器件的REF输入和外部时钟引脚,OUT0反馈到外部时钟输入(类似于图9)。

图10. 外部零延迟固有偏移时序误差(AD9520)

图11. 外部零延迟调整后的偏移时序(AD9520)

涉及外部零延迟的考虑

在要求外部零延迟架构的应用中,务必避免引入过大的外部延迟以及将无用信号耦合到PLL反馈路径。外部延迟可能导致PLL环路不稳定,进入PLL反馈路径的无用信号则可能破坏输出时钟信号。

注意,外部信号路径中出现的任何延迟都会成为PLL反馈环路的一部分。如果PLL环路带宽太宽,外部路径的额外延迟可能会使环路不稳定。用户应选择外部环路滤波器,使得环路带宽能够支持额外的延迟,同时仍能确保环路稳定。

外部零延迟架构的PLL反馈路径中包括外部电路,意外进入反馈路径的无用信号可能会带来严重问题,原因是进入PLL反馈路径的任何信号都会被PLL放大。因此,即使非常小的信号,也可能变大到输出端无法接受的程度。适当的印刷电路板布局和屏蔽技术是防止无用信号侵入的最佳防护手段。

-

敏捷合成器的技术原理和应用场景2025-02-20 776

-

pll频率合成器工作原理与pll频率合成器的原理图解释2023-02-24 11793

-

锁相环频率合成器是什么原理?2021-04-22 2649

-

什么是频率合成器2019-08-19 5767

-

如何利用FPGA设计PLL频率合成器?2019-07-30 4561

-

基于DDS的频率合成器设计介绍2019-07-08 3034

-

Σ-Δ调制频率合成器【转】2012-08-02 4076

-

多环锁相频率合成器的设计2010-05-13 2654

-

频率合成器,频率合成器原理及作用是什么?2010-03-23 15337

-

ΣΔ技术在锁相环频率合成器中的应用2009-08-19 831

-

AD9850 DDS 频率合成器的原理及应用2008-04-10 1545

全部0条评论

快来发表一下你的评论吧 !