针对物理设计难点进行分析及提出解决方案

描述

1、前言

集成电路具有体积小,重量轻,引出线和焊接点少,寿命长,可靠性高,性能好等优点,同时成本低,便于大规模生产。它不仅在工、民用电子设备如收录机、电视机、计算机等方面得到广泛的应用,同时在军事、通讯、遥控等方面也得到广泛的应用。

但随着半导体工艺的不断发展和通信技术的不断提高,以超大规模、高集成度和复杂性为特征的通信集成电路芯片物理设计,相比于普通的消费类产品芯片(如LED芯片,FLASH芯片等),在超深亚微米工艺下面临着更为严峻的挑战:一、工艺特征尺寸的不断缩小、电源电压的不断降低、电源噪声对芯片性能的影响日益凸显,已成为超大规模通信集成电路物理设计中一个不可忽视的问题;二、高速通信集成电路芯片的时序对于芯片制造过程中产生的偏差越来越敏感,精确的电路模型及准确的时序分析方法成为制约通信集成电路芯片能否实现快速时序收敛的关键;三、通信集成电路芯片通常需要支持各种高速接口电路的应用,从而造就了独特的时钟树拓扑结构——网状时钟树,而通信芯片固有的超大规模的特性更加重了这种复杂高速时钟树优化的难度;四、随着数据传输速度和容量的不断提高、信道噪声对信号质量的影响越来越大,高速串并/并串转换器(HighSpeedSerdes,HSS)的抗噪性、传输信道数量及其建模仿真的精确度成为影响通信系统设计的重要因素。IBM针对这些通信芯片的物理设计难点,较为详细地介绍了相应的解决方案。

2、物理设计难点分析及解决方案

微电子技术发展的基本特征就是遵循摩尔定律。器件特征尺寸不断地缩小,但在尺寸缩小的同时,要保证芯片的高性能/价格比,低成本,可靠性高。针对该物理设计难点,IBM提出了相应的解决方案,具体介绍如下。

2.1 电源噪声分析

任何电源及输电线都存在内阻,正是这些内阻引起电源的噪声干扰。如果没有内阻存在,无论何种噪声都会被电源短路吸收,在线路中不会建立起任何干扰电源。当芯片上的信号开始跳变时,如由0到1,电源网络的阶跃响应会如图1所示。最低电压值由芯片上的静态电容值与翻转电容值的比例决定,跳变后的谐振则为典型的LC谐振,静态电压降则是平均功率的体现,由网络中的寄生电阻导致。稳态的交流响应与工作频率相关,其波动的电压值随着工作频率的增加而减小.

由于大规模通信集成电路芯片通常带有各种复杂的高速接口,并在整个产品的工作过程中要求有很高的可靠性,因此芯片的电源设计起着极其关键的作用。为保证芯片的电源完整性,在芯片的设计流程中必须对IO的同步开关噪声SSN(SimultaneousSwitchNoise)、芯片上的动态电源噪声、静态压降、ESD(Electro-StaticDischarge)静电保护以及电迁移EM(ElectroMigration)进行有效的检查和签收。

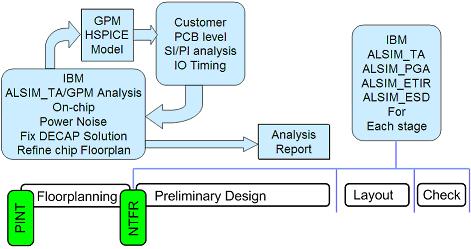

在进行超大规模集成电路的设计过程中,IBM有一套完整的流程对电源噪声进行分析(如图1所示),能够在芯片的布局阶段尽早发现和解决芯片布局与电源设计上存在的问题,以减少设计反复的时间。电源噪声检查在芯片设计过程中是一个重要的签收环节,完整的设计和分析流程保证了IBM能够提供高质量的专用集成电路芯片。

图1 电源噪声分析流程

IBM的电源噪声分析流程贯穿了整个芯片设计过程,包含了两个噪声评审会议和一系列分析工具。在芯片布局之前,噪声分析小组会和项目的物理设计工程师一起召开PINT(Post-IDRNoiseTeamReview)会议,对芯片的设计规格进行审查,找出设计中可能存在的风险,提出在布局时需注意的事项,让物理设计工程师在布局前对整个芯片的电源噪声情况有所了解,避免由于电源噪声无法满足而反复修改布局,造成不必要的浪费。在芯片布局阶段,负责电源噪声分析的工程师紧跟芯片布局的变化,充分利用IBM的GPM(GenericPackageModel)和ALSIM(AustinLinearSimulator)系列工具及时评估芯片的电源噪声。

GPM是一个可以快速分析IO同步开关噪声的建模和分析工具。GPM针对芯片中包含IO的局部区域建立HSPICE模型,其中包含通用的封装RLC模型,芯片上的电源分配网络,IO驱动器模型和模拟一般逻辑电路翻转的等效模型。GPM的分析流程可以简单总结为以下几个步骤:一、使用AutoGPM在芯片上自动找到IO最密集的区域,然后生成Hspice的网表;二、在网表中填入仿真所需要的参数;三、分析仿真结果,可调整电容数量来满足动态压降的要求。由于GPM分析不需要成熟的芯片布局,建模和仿真速度快,因此可以尽早分析IO对电源噪声的影响,为芯片的IO布局提供快速的参考,评估IO所需的电源滤波方案,避免在设计中形成电源噪声的热点。一旦芯片布局确定,GPM模型可以代表实际芯片的IO翻转情况,该模型可以交付客户,让客户联合系统的板级模型进行芯片、封装和PCB的信号完整性分析和时序分析。分析的结果可以帮助客户在芯片设计早期评估系统的性能,同步地进行PCB的设计,确定更加合理的芯片时序约束。

ALSIM_TA(TransientAnalysis)是一个高效的全芯片动态电源噪声仿真分析工具。相对于GPM侧重于对整个芯片进行局部仿真,ALSIM_TA更着重于分析芯片的全局噪声情况,其主要工作在两种模式下,Floorplan(可以在设计的早期来运行,为设计的布局提供指导,有效地减少Iteration) 和FinalAnalysis(当设计已基本成型时,基于规划好的电源网络,封装的寄生参数,准确的电流波形和频率信息,这时ALSIM_TA就可以进行更为精确的噪声分析。)分析流程可以简单归纳为以下几个步骤:一、建立电流模型;二、建立电源网络分布模型并简化;三、将各模型和封装参数结合,进行暂态仿真分析。仿真过程中使用了芯片的封装模型,片上电源网络模型和代表各种逻辑电路翻转的电流波形。通过ALSIM_TA仿真可以得到整个芯片电源噪声峰峰值,动态压降等信息在芯片上的分布情况,并以二维图形直观地显示(如图2所示)。ALSIM_TA的结果可以直观地评估芯片的布局和电源滤波方案对电源噪声的影响。

图2 ALSIM_TA仿真结果

根据早期的ALSIM_TA和GPM分析结果,物理设计工程师可以尽早优化芯片布局,通过增加噪声源和噪声敏感的器件之间的距离,增加片上去耦电容等方式获得较好的噪声性能。

:

-

芯和半导体最新发布“SI/PI/多物理场分析”EDA解决方案2024-02-18 1361

-

DesignCon2024 | 芯和半导体发布针对下一代电子系统的“SI/PI/多物理场分析”EDA解决方案2024-02-02 1386

-

新唐针对BMS提出完整解决方案2023-08-21 1843

-

通信芯片的物理设计难点及IBM应用解决方案2021-06-21 4592

-

通信芯片有哪些物理设计难点?如何去解决?2021-05-25 3168

-

单片机之间的通信方式/难点/解决方案2020-12-31 1820

-

无线充电测试难点和解决方案2020-08-14 2440

-

什么是WiMAX物理层信号测试解决方案?2019-08-08 1801

-

无线充电测试难点及解决方案2019-01-26 11104

-

ADI提出针对伺服电机控制的解决方案2018-11-16 4214

-

专家提出MicroLED显示屏幕的全彩化解决方案2018-11-10 2749

-

基于IP存储物理安全解决方案2012-12-18 1439

-

R&S对WiMAX物理层的测试解决方案2010-06-23 851

-

世平集团所代理产线ADI针对DSC提出一系列解决方案2009-05-08 1146

全部0条评论

快来发表一下你的评论吧 !