Vivado+Vitis将程序固化的Flash的操作流程

描述

ZYNQ 的程序固化是指将程序代码永久存储到非易失性存储器中,使系统上电后能自动加载运行的过程。主要固化方式:QSPI Flash固化:常用方式,容量小,如启动代码、FPGA 配置。NAND Flash固化:适合大容量程序存储,如文件系统。SD卡固化:方便更新,适合开发阶段。

1 VIVADO

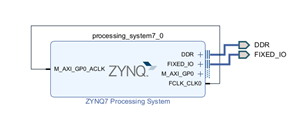

创建block design,添加ps ip。使能QSPI外设,其他不需要的外设或者引脚可以取消勾选。

运行block automation,校验。

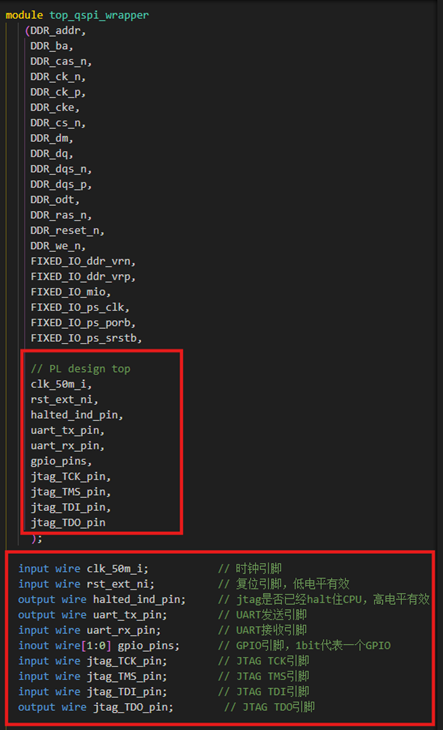

对刚才配置好的PS生成HDL wrapper。

修改打包的顶层文件,将PL部分实现的顶层设计作为一个模块实例化到Wrapper里,线网同名调用即可。

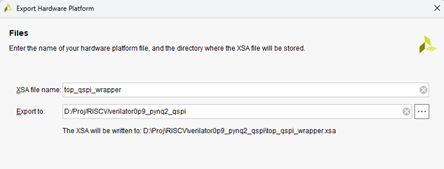

生成比特流,导出硬件(xsa格式的文件)。

2 VITIS

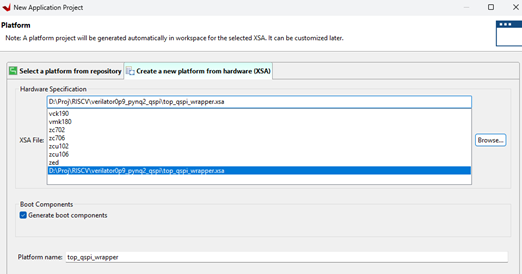

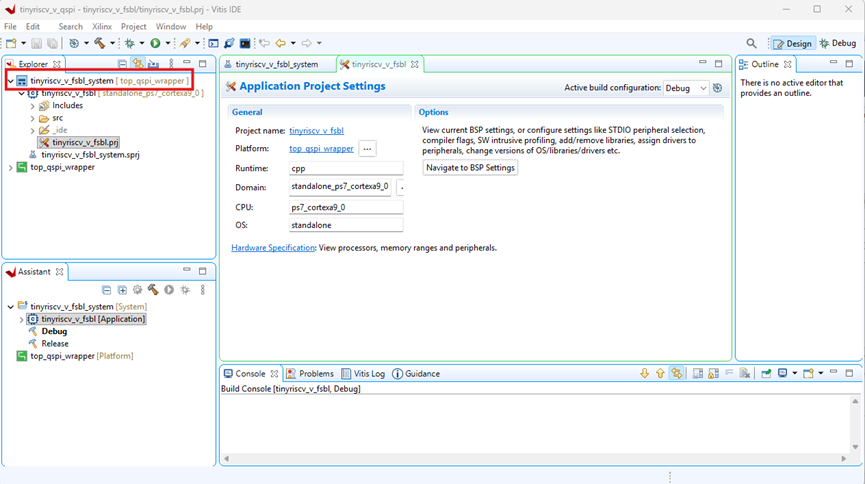

启动vitis IDE,创建app project。有三个创建project选项。platform project是一个工程的平台工程,通过xsa文件生成,也就是你在vivado里设计的工程,它在vitis里作为一个平台,其上搭建application project。选择application project,如果没有platform的话,软件会引导你生成platform。选择platform project的话,会先创建platform,然后再手动创建application project。也就是说,我们在vitis里的工程,就是application project,而我们又必须使用xsa文件生成一个硬件平台承载application project。这就是两个工程的区别和联系。

选择vivado中导出的硬件xsa文件,勾选启动部件。

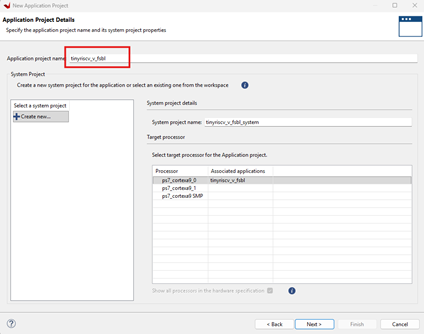

注意这里的app project名称不要直接写fsbl。因为会生成

保持默认。

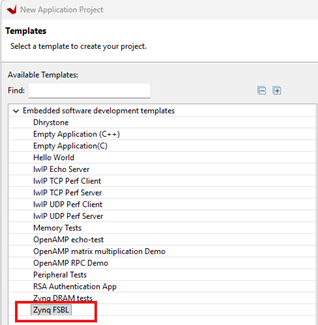

选择FSBL模板。

右击xxx_system,Build project。

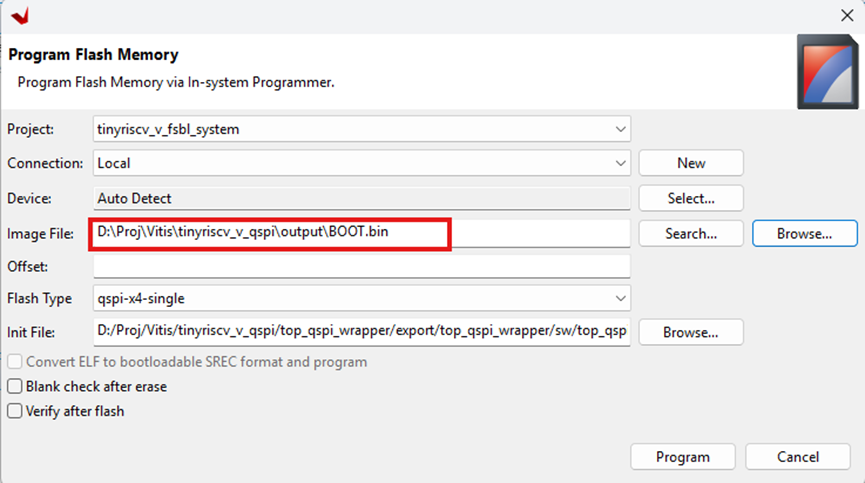

Create boot image。创建一个名为output的文件夹用于存放启动文件:output.bif和BOOT.bin。制作启动镜像需要添加3个源文件:fsbl作为bootloader,比特流文件bit和顶层可执行文件elf作为data partition。

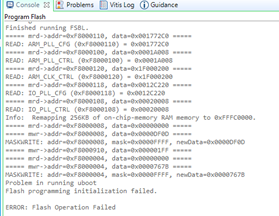

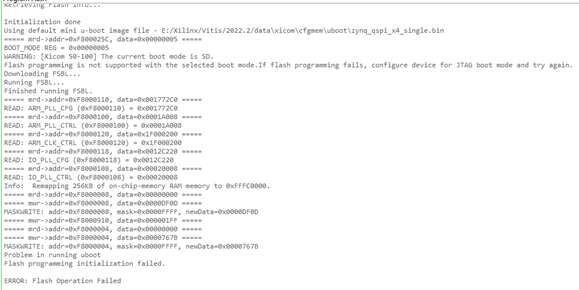

烧录到flash。

如果是第一次烧录,直接把跳帽偏置在QSPI即可,否则会出现初始化失败错误。如果flash已经烧录了一个版本,需要将跳帽偏置在JTAG,然后烧录,否则也会报错。烧录结束后再把跳帽放会QSPI。

-

使用AMD Vitis Unified IDE创建HLS组件2025-06-20 2672

-

vitis和vivado有什么区别和联系呢?2023-10-16 1180

-

【KV260视觉入门套件试用体验】+02.开发环境安装Vitis/Vivado(zmj)2023-08-27 1190

-

如何在Vitis中把设置信息传递到底层的Vivado2022-08-02 1924

-

Vitis HLS工具简介及设计流程2022-05-25 3784

-

Flash程序是如何去实现自动加载固化的呢2022-01-18 2200

-

如何基于Vitis中把设置信息传递到底层的Vivado2021-07-28 3128

-

Vivado生成、固化烧录文件2021-04-21 1808

-

Vitis初探—1.将设计从SDSoC/Vivado HLS迁移到Vitis上2021-01-31 2210

-

Vivado硬件平台更新后Vitis工程如何快捷更新2021-01-28 1986

-

Vivado硬件平台更新后Vitis工程要如何快捷更新2021-01-22 3225

-

Vivado HLS和Vitis HLS 两者之间有什么区别2020-11-05 41447

-

基于Vivado下固化FLASH的压缩和提高加载速度2019-04-20 11756

-

vivado固化flash失败2017-09-03 17236

全部0条评论

快来发表一下你的评论吧 !