Samtec深度工艺分享 | 触点擦拭行程至关重要吗?

描述

摘要前言

答案是肯定的。 触点擦拭行程是互连器件设计与开发过程中需重点考量的关键要素。

通过合格性测试确认连接器在完全配接状态下 具备充足的擦拭行程 ,可确保终端应用中,连接器接触面的 污染物与氧化沉积物被有效清除 ,保障连接可靠性。

像Samtec这样的互连器件厂商,在产品研发阶段就会将触点擦拭行程纳入考量 ,因为它是连接器设计本身的固有组成部分。

什么是触点擦拭行程?

触点擦拭行程,指的是连接器 在一次标准插拔循环中,接触件的有效配接长度,其核心作用是清除接触面的沉积物 。

另一种定义方式为: 端子插入插座的有效深度,通过该深度的相对位移,可刮除接触面的氧化层及其他异物 。

镀锡工艺与氧化膜去除

终端应用环境中的各类因素,都会导致连接器接触面产生污染物沉积。周边生产工序产生的微小颗粒、腐蚀性氧化膜(例如镀锡层暴露于空气或潮湿环境中形成的氧化层)、灰尘与油污等,均会干扰连接器配接界面的电气接触,进而引发连接失效。因此,在连接器的常规插拔过程中,必须通过“擦拭” 动作清除接触面的污染物,才能维持稳定的信号连接。

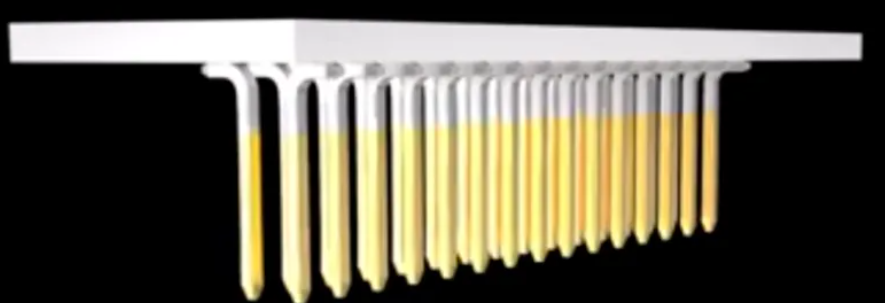

在需耐受强振动与冲击的高可靠性应用场景中,触点擦拭行程的重要性更为凸显。这类场景下,具备充足擦拭行程的多触点冗余设计,能 大幅提升连接稳定性 。Samtec的 Tiger Eye™ 系列产品就是典型代表,其采用的 多触指铍铜接触件 ,可充分保障触点擦拭行程与连接可靠性。

堆叠高度与触点擦拭行程

堆叠高度,即 连接器配接后两块印制电路板之间的间距 ,会直接 影响接触件的有效配接长度 。因此,严格遵循厂商给出的板级堆叠设计规范,控制印制电路板间距在端子插拔深度的最大与最小允许范围内,是确保触点擦拭行程充足的关键。

公差累积也可能对触点擦拭行程造成影响,因此建议开展公差分析。

以Samtec SEARAY™系列0.8毫米间距连接器为例,下图将展示其在完全配接状态下的最大擦拭行程与极限工况下的最小擦拭行程参考值。

矮型连接器与触点擦拭行程

矮型连接器凭借 紧凑的结构 ,在嵌入式与高密度设计中备受青睐。但在这类连接器的设计中,触点擦拭行程面临着两难挑战: 既要尽可能缩小连接器体积(对应更短的配接长度),又要保证足够的触点擦拭行程以实现接触面清洁功能 。

针对这一难题,可采取的优化方案是 在接触区域局部镀覆黄金 , 黄金具备优异的 抗氧化性 ,可最大限度降低接触面 腐蚀风险 ,同时提供 低接触电阻 、高耐磨的稳定连接。

Samtec此前发布的一篇文章 Samtec连接器小课堂 | 连接器电镀常识Q&A ,详细阐释了不同镀层方案的适用场景。

部分核心结论: 对于矮型精密间距连接器,镀金往往是唯一的优选方案。 原因在于,与镀锡等其他镀层相比,镀金工艺所需的接触 正向力更低 ,更适矮型连接器的结构设计。而**“局部镀金 + 整体镀锡” **的复合镀层方案,是Samtec目前最受欢迎的选择,该方案兼具黄金镀层的高可靠性与锡镀层的易焊性、经济性双重优势。

对产品的影响与测试验证

触点擦拭行程对板对板互连解决方案的信号连接性能与终端应用可靠性至关重要,是互连器件设计过程中不可或缺的核心环节。基于此,Samtec会对旗下产品的触点擦拭行程、端子插入深度及堆叠高度等关键参数开展全面的合格性测试,并形成标准化技术文档,方便客户随时查阅。

客户可登录Samtec官网,在对应产品系列页面查询上述信息:进入产品页面后,点击 “图纸” 选项卡,再选择 “配接视图” 文档即可查看详细参数。

若你对特定Samtec产品的触点擦拭行程参数存在疑问,欢迎随时 联系我们Samtec中国的应用技术支持团队 ,期待与你深入交流!

-

新一代小区网关:灵活性与高性能至关重要2009-10-05 3679

-

太阳能市场竞争激烈 太阳能充电管理至关重要2015-10-13 3030

-

为什么DSP对音频设计至关重要?2018-10-30 2214

-

天线系统在NFC设备中至关重要2019-07-17 2831

-

实现下一代机器人至关重要的关键传感器技术介绍2020-12-07 6227

-

为什么视觉系统对自动驾驶至关重要看了就知道2020-12-29 1868

-

请问磁珠的选型重要吗?2021-03-17 2002

-

请问选择合适的FPGA千兆位收发器为什么至关重要?2021-04-13 1714

-

示波器衡量指标中至关重要但常被忽略的两个概念是什么?2021-05-12 1459

-

线程如何与CPU工作,为什么对系统性能至关重要2020-06-30 4705

-

物联网基础设施至关重要2020-07-15 3644

-

选择合适的无线技术至关重要2022-05-31 2955

-

基于硬件的信任对于保护物联网至关重要2023-01-03 1459

-

Samtec技术漫谈 | 样品至关重要2023-08-16 710

-

为什么ESD静电防护区域的湿度至关重要?2023-12-20 3702

全部0条评论

快来发表一下你的评论吧 !