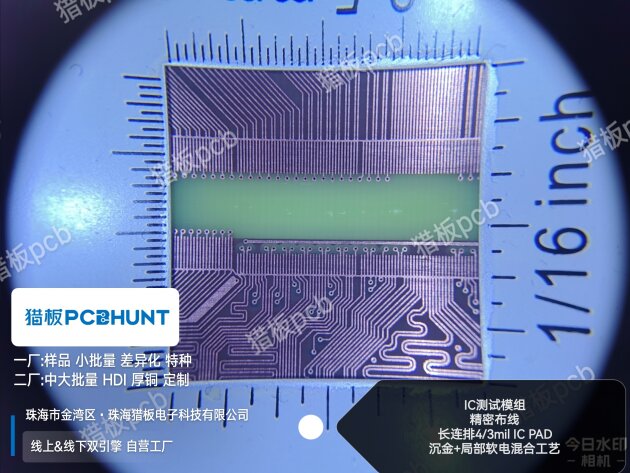

猎板PCB IC测试模组(4/3mil级)工艺能力技术说明

描述

一、订单核心工艺参数

本订单交付的IC测试模组半成品,采用以下关键工艺实现,各项指标均满足客户对高密度测试载体的技术要求:

长连排IC PAD:采用线宽4mil、PAD尺寸3mil的长连排布局,PAD尺寸偏差控制在±0.2mil以内。

精密布线:实现线宽/线距最小3mil的多层高密度走线,阻抗偏差控制在±5%以内。

表面处理:采用沉金+局部软电混合工艺,沉金层厚度控制在0.05-0.1μm,软电区域延伸率>15%。

二、关键工艺能力详解

1.长连排4/3mil IC PAD制造能力

适配场景:本订单针对多引脚窄间距IC的测试需求,采用长连排PAD布局,需满足探针的精准接触与信号稳定传输。工艺实现:

采用激光直接成像(LDI)设备进行高精度曝光,分辨率达2μm,确保PAD图形的精细还原。

优化蚀刻液配比与蚀刻速率,结合在线AOI检测,实现长连排PAD的尺寸均匀性达99.5%以上,避免因PAD偏差导致探针接触不良。

采用微蚀处理提升PAD表面粗糙度,增强后续镀层结合力,保障测试过程中的电气稳定性。

2.高密度精密布线能力

适配场景:本订单模组需承载多通道高频测试信号,布线密度直接决定模组的小型化与信号完整性。工艺实现:

基于客户DFM需求,采用分层阻抗仿真设计,对差分对、高速信号走线进行优化,降低串扰与信号损耗。

通过LDI曝光与干膜显影工艺,实现最小3mil线宽/线距的精细布线,在有限基板面积内完成多通道信号链路布局。

采用接地屏蔽层设计,对高频信号走线进行隔离,保障10Gbps以上信号传输的完整性。

3.沉金+局部软电混合工艺能力

适配场景:本订单模组需同时满足探针接触的耐磨性与局部区域的耐弯折性,单一表面处理无法兼顾。工艺实现:

采用局部阻镀工艺,精准划分沉金区域与软电区域,通过预镀镍层优化界面结合力,避免镀层脱落。

沉金区域控制镀层厚度在0.05-0.1μm,保障探针耐磨寿命>10万次,满足高频次测试需求。

软电区域采用特殊电镀配方,提升镀层延伸率至>15%,增强模组在复杂测试场景下的抗疲劳能力。

三、本订单制造保障

产线配置:本订单由一厂(样品/小批量/特种工艺产线)完成,配备LDI、AOI、阻抗测试仪等高精度设备,保障工艺精度与稳定性。

制程管控:关键工序采用SPC统计过程控制,对蚀刻速率、镀层厚度等参数进行实时监控,确保制程能力指数CPK≥1.33。

交付周期:从订单接收至半成品交付仅需2天,体现小批量特种订单的快速响应能力。

审核编辑 黄宇

-

国内一流PCB制板厂的PCB工艺能力及设计建议2012-01-01 27199

-

华强PCB工艺能力解读2012-08-27 3143

-

诚聘PCB 工艺工程师2016-10-14 3714

-

有靠谱6层1阶HDI板PCB样板厂推荐吗?谢谢!!2017-02-24 8296

-

制作工艺分析2018-10-24 28393

-

PCB工艺DFM技术要求综述2020-06-06 9182

-

PCB工艺制程能力介绍及解析2023-08-25 1553

-

PCB工艺制程能力介绍及解析(上)2023-08-28 2150

-

PCB工艺制程能力介绍及解析(下)2023-09-01 1798

-

PCB表面镀金工艺,还有这么多讲究!2023-10-24 2045

-

爆款福利来袭!猎板PCB打样5元/款史上最低!2021-03-15 4323

-

为行业焕新生,猎板PCB上海慕尼黑电子展圆满落幕2021-04-20 2539

-

猎板新工艺—镍钯金官网上线!新的表面处理技术值得关注的问题?2021-10-14 4769

-

电路板级的EMC设计(3) PCB布线技术2021-11-07 1187

-

别再让板厂头疼了!高精密PCB DFM自查清单(工程师必备)2026-01-30 610

全部0条评论

快来发表一下你的评论吧 !