半导体制造中刻蚀工艺技术介绍

描述

文章来源:学习那些事

原文作者:小陈婆婆

多项目圆片(MPW)与多层光掩模(MLR)显著降低了掩模费用,而无掩模光刻技术如电子束与激光直写,在提升分辨率与产能的同时推动原型验证更经济高效。刻蚀工艺则向原子级精度发展,支撑先进制程与三维集成,共同助力集成电路研发与应用降本提速。

掩模成本降低

在半导体制造的小批量生产场景中,降低掩模成本的技术创新持续推动原型验证与教学应用的成本优化。

多项目圆片(MPW)通过将多个设计集成于同一组掩模,显著分摊了单次流片的掩模成本,成为学术机构与初创企业验证创新设计的首选路径。而多层光掩模板(MLR)则通过组合同一产品的多层掩模,减少实际掩模数量,在保持设计独立性的同时降低物理掩模的制造与存储成本,尤其适用于工艺开发阶段的快速迭代需求。

直写技术作为无掩模光刻(MLL)的核心载体,正通过电子束与激光束系统的协同进化突破生产率瓶颈。电子束直写凭借5nm以下的高分辨率,在关键层修复、小批量样品制造中展现不可替代性,而多电子束阵列技术的引入,通过并行写入大幅提升吞吐量,逐步缩小与传统光刻的效率差距。激光束直写则凭借无需真空环境、设备成本低廉的优势,在非关键层图案化中快速渗透,其通过动态聚焦与智能路径规划算法,实现亚微米级线条的精准控制,同时结合导电层沉积技术,有效抑制电子充电效应,保障图形转移的保真度。

无掩模光刻的商业化进程在2026年迎来新突破:日本NuFlare推出多电子束直写系统,通过32束并行写入实现每小时10片晶圆的产能,良率提升至95%,设备单价控制在2000万美元以内,较传统光刻机更具成本优势。中国在激光直写领域加速追赶,中科院苏州纳米所研发的激光直写设备实现8nm线宽,通过智能曝光算法优化,生产率提升30%,已应用于MEMS传感器与先进封装基板的制造。此外,无掩模光刻在缺陷控制方面取得进展,通过实时监测与闭环反馈系统,将颗粒污染率降低至0.1%,满足大批量生产的质量要求。

这些技术不仅降低了小批量生产的门槛,更通过设计制造协同(DFM)工具的深度融合,实现从设计到制造的全流程优化。例如,光刻友好设计通过规则化版图、固定多晶节距,降低直写过程中的图形复杂度,提升生产效率;而EDA平台集成直写路径规划与缺陷预测功能,实现从设计到制造的无缝衔接。

刻蚀工艺

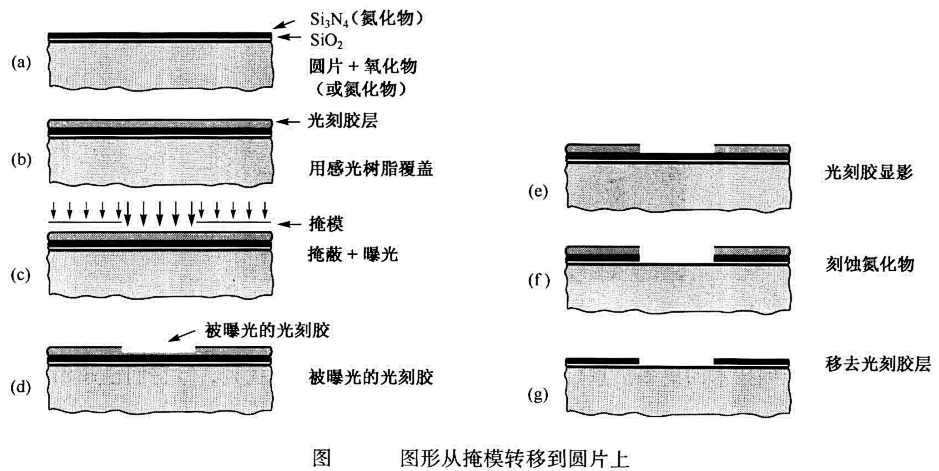

刻蚀工艺作为半导体制造中图形转移的关键环节,其核心在于实现高精度、高选择性的各向异性刻蚀,以满足先进制程对线宽控制、侧壁垂直度及材料选择性的严苛要求。

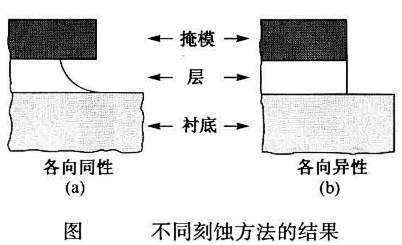

湿法刻蚀虽工艺成熟、成本低廉,但受限于各向同性特性,在亚微米节点下易引发“钻蚀”问题,导致图形失真,故逐渐被干法刻蚀替代。

干法刻蚀通过等离子体或离子束实现物理与化学过程的协同,其中反应离子刻蚀(RIE)凭借电场加速的活性离子与表面原子反应生成挥发性产物,在实现高各向异性的同时,通过调整气体成分(如CHF₃等碳质衬底)优化选择性,减少对下层材料的损伤。高密度等离子(HDP)技术通过感应耦合等离子体源提升等离子密度与电离度,在低压环境下实现高深宽比结构的精确刻蚀,广泛应用于浅沟槽隔离(STI)、接触孔形成等关键步骤。

随着制程节点推进,刻蚀技术持续演进。原子层刻蚀(ALE)通过循环交替的表面修饰与刻蚀步骤,实现单原子层级别的精度控制,有效降低侧壁粗糙度与等离子损伤,成为3nm以下节点的重要技术方向。深硅刻蚀(DSE)则通过博世工艺(交替沉积钝化层与刻蚀)实现高深宽比硅通孔(TSV)的垂直侧壁,支撑三维集成与先进封装需求。此外,针对新型材料(如高k介质、金属栅)的刻蚀挑战,业界开发了专用气体配方与工艺窗口,如采用含氟气体与氢气的混合气体提升对高k材料的选择性,同时通过实时终点检测与闭环控制确保工艺一致性。

天线效应与等离子损伤问题在先进制程中尤为突出,工业界通过天线设计规则限制导电区域与栅氧面积的比值,并引入保护二极管、虚拟接地等措施降低电荷积累风险。例如,在逻辑门输入端并联保护二极管可有效泄放等离子诱导的电荷,避免栅氧击穿。同时,工艺优化如低压刻蚀、脉冲等离子体技术等进一步减少电荷积累与材料损伤,提升器件可靠性。

当前,刻蚀技术正与先进光刻、薄膜沉积等工艺深度协同,推动集成电路向三维集成、异构集成演进。例如,在3D NAND闪存中,深硅刻蚀与原子层沉积(ALD)的组合实现多层堆叠结构的高精度制造;在先进封装中,刻蚀工艺支撑硅中介层、混合键合等技术的实现,提升系统性能与集成度。随着新材料、新工艺的不断涌现,刻蚀技术将持续突破物理极限,支撑半导体产业向更小节点、更高性能方向发展,延续摩尔定律的生命力。

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1780

-

《半导体制造工艺》学习笔记2012-08-20 67956

-

半导体制造2012-07-11 5176

-

半导体制造技术经典教程(英文版)2014-03-06 26534

-

半导体工艺技术的发展趋势2019-07-05 4632

-

半导体工艺技术的发展趋势是什么?2019-08-20 4574

-

半导体制造的难点汇总2020-09-02 4918

-

半导体光刻蚀工艺2021-02-05 7110

-

半导体工艺技术2016-05-26 1255

-

MEMS工艺——半导体制造技术2021-04-08 4456

-

半导体制造关键工艺:湿法刻蚀设备技术解析2025-04-27 3033

-

半导体boe刻蚀技术介绍2025-04-28 7314

-

半导体刻蚀工艺技术-icp介绍2025-05-06 5668

-

台阶仪在半导体制造中的应用 | 精准监测沟槽刻蚀工艺的台阶高度2025-08-01 1169

-

半导体制造中的侧墙工艺介绍2026-04-09 274

全部0条评论

快来发表一下你的评论吧 !