新思科技IP产品组合助力光网络芯片与边缘AI落地

描述

开发片上系统(SoC)的第一步,是正确构建模块:将预先设计并经过严格验证的 IP,用于逻辑、存储器、输入/输出(I/O)以及其他核心功能。

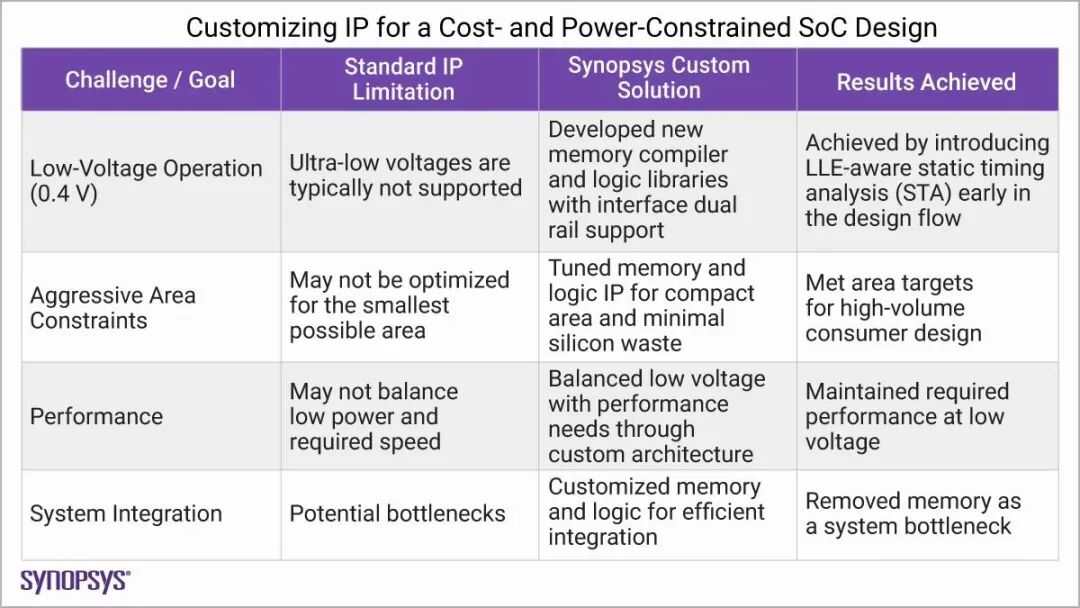

虽然标准 IP 产品能够满足大多数设计需求,但在某些项目中要求会更高——尤其当创新是首要目标,或项目对功耗、性能、面积(PPA)提出极为严苛的指标时。

因此,定制 IP 的重要性正日益凸显。

而这正是新思科技的真正独到之处。我们不仅拥有业内最广泛的经过硅验证的 IP 产品组合,而且更愿意为客户量身打造专属的 IP 解决方案。

客户案例:为功耗敏感的光网络芯片定制基础 IP,助力边缘 AI 落地

阶段 1:确认需求,接受挑战

近期,一位客户带着独特的应用场景和严苛需求找到我们。他们计划开发一款用于构建光网络基础设施的新型芯片,以应对边缘 AI 激增的算力需求。这款芯片须在仅 0.4V 的电压下稳定运行,而市场上没有任何现成的 IP 能满足如此低电压的要求。更具挑战的是,项目交付周期只有 8 个月。

面对挑战,我们从不退缩。依托业内最全面、且经硅验证过、性能优化且高灵活度的基础 IP 产品组合,新思科技 IP 研发团队迅速启动项目,全力以赴。

在全面评估客户的 PPA 目标后,我们意识到,该设计的低电压要求对存储器编译器和逻辑库来说都是一项不小的挑战。

阶段 2:迎难而上,定制 IP

存储位单元——芯片内部的微型存储元件——在 0.5V 及以下电压下通常难以保持稳定。为解决这一问题,我们团队开发了全新的存储器编译器架构:优化存储位单元设计、调整外围电路,并采用先进的低泄漏晶体管,确保在低电压下依然稳定运行。

针对其他类型的存储器,我们增强了双轨供电支持——这是该技术节点的首选方案,允许芯片不同部分能够在不同电压下工作。例如,存储器阵列通常需要比逻辑电路更高的最低工作电压,而我们的双轨供电优化确保逻辑电路不受存储器电压限制。这种灵活性有效降低了整颗芯片的功耗。

除了实现低电压运行,我们的团队还致力于缩小设计的硅片面积,同时最大化能效。具体措施包括:

优化存储器架构,减少面积。

采用更小、更高效的构建模块定制逻辑组件。

实施电源门控技术,并引入低泄漏单元库,降低空闲期间能耗。

利用先进制造工艺,在更小面积内集成更多功能。

这些优化措施协同作用,使芯片各部分功耗更低、面积更小,这对于成本和功耗受限的芯片设计而言,都至关重要。

阶段 3:全面达成 PPA、可靠性与交付目标

在实现客户的能效目标后,我们开发了对应的测试芯片,用于验证该定制化的存储器编译器,并确保其在实际应用中表现稳健。通过全面的压力测试和基准测试,我们确认其性能及稳定性,排除了潜在问题,并为长期可靠性建立了坚实保障。

该设计不仅全面达成所有 PPA 指标,还在客户要求的 8 个月的紧凑周期内完成所有设计。目前芯片正处于等待流片阶段,预计很快将进入量产。

总结:卓越的 IP 定制能力与协作模式

当项目需要同时满足苛刻的 PPA 指标和紧凑的交付周期时,量身定制 IP 模块并非易事。这不仅要求多方紧密协作,还需要设计与工程具备高度灵活性,并有勇气攻克深层技术挑战。而多数 IP 供应商对于这样的投入程度,是难以做到的。

但这正是新思科技的优势所在。

新思科技凭借着业内最全面、适应性最强的基础 IP 产品组合,一流的研发引擎,以及高度协作的现场工程师团队,随时准备帮助客户突破复杂技术难题,实现他们野心勃勃的 PPA 目标。

-

EdgeBoard FZ5 边缘AI计算盒及计算卡2020-08-31 2669

-

新思科技发布业界首款全栈式AI驱动型EDA解决方案Synopsys.ai2023-04-03 1633

-

Synopsys提供业界最完整的IP产品组合来加速物联网设计的开发2015-10-21 1580

-

新思科技将开发广泛DesignWare IP核产品组合2020-11-03 3249

-

新思科技助力基于下一代Armv9架构的SoC设计成功2021-06-02 2973

-

高通AI软件栈产品组合提供从边缘到云端的AI功能2022-06-23 2350

-

新思科技推出业界领先的广泛车规级接口IP和基础IP产品组合2023-10-31 2131

-

新思科技加入“Arm全面设计”生态系统并提供IP和芯片设计服务2023-11-17 1908

-

研华携手Hailo,扩展高算力边缘 AI 产品组合2023-12-12 627

-

Supermicro全新系统产品组合将前沿AI性能推向边缘计算环境2024-02-24 1849

-

高通推出面向AI时代的全新工业物联网产品组合2024-11-08 1339

-

新思科技推出全新硬件辅助验证产品组合2025-02-18 1433

-

聆思科技获得Ceva-Waves Wi-Fi 6 IP授权2025-02-19 1406

-

新思科技旗下Ansys仿真和分析解决方案产品组合已通过台积公司认证2025-10-21 784

-

格罗方德收购新思科技处理器IP产品组合2026-01-19 1548

全部0条评论

快来发表一下你的评论吧 !