高效能计算核心:三相交错并联LLC拓扑发展趋势

电子说

描述

高效能计算核心:三相交错并联LLC拓扑发展趋势与SiC MOSFET在AI算力电源中的深度赋能

BASiC Semiconductor基本半导体一级代理商倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 绪论:AI算力时代的能源变革与电源挑战

随着生成式人工智能(Generative AI)、大语言模型(LLM)以及高性能计算(HPC)的爆发式增长,全球数据中心的算力需求正在经历一场前所未有的指数级跃迁。这场算力革命的背后,是一场更为严峻的能源与热管理挑战。传统的服务器电源架构,曾长期服务于以CPU为中心的通用计算场景,如今在面对以GPU和专用AI加速器为核心的高密度计算集群时,正显露出效率、功率密度和热管理的瓶颈。

1.1 从千瓦到兆瓦:AI集群的功率密度跃升

在过去十年中,标准服务器机架的功率密度通常维持在5kW至10kW之间。然而,随着NVIDIA H100、Blackwell架构以及未来Rubin架构等高性能GPU的引入,单芯片功耗已突破700W甚至1000W大关。对于由数千张GPU组成的AI训练集群,单机架功率密度正迅速攀升至40kW、100kW,甚至在液冷技术的加持下向1MW迈进 。

这种功率密度的急剧提升对电源供应单元(PSU)提出了极其苛刻的要求。在有限的机架空间内(通常不增加占地面积),PSU不仅需要提供成倍增长的功率输出,还必须保持极高的转换效率。在100kW的机架中,即便电源效率高达97%,剩余3%的损耗也意味着3kW的热量产生——这相当于三台家用电热炉在机柜内部持续全功率运行。因此,提升电源转换效率不再仅仅是节能的环保口号,而是保障AI集群稳定运行、降低散热成本(TCO)的生存基石。

1.2 架构演进:从12V到48V/54V与高压直流(HVDC)

为了应对电流急剧增加带来的配电损耗(Ploss=I2R),数据中心电源架构正在经历深刻的变革。传统的12V中间总线架构在面对AI服务器数百安培的电流需求时,铜排损耗和连接器应力已变得不可接受。Open Compute Project (OCP) 推出的Open Rack v3 (ORv3) 标准,明确将机架母线电压提升至48V或54V,这一改变理论上将配电损耗降低了16倍 。

在输入端,为了进一步提升端到端效率,行业正在探索从传统的交流输入向高压直流(HVDC)输入过渡,例如400VDC甚至800VDC架构。这种架构消除了机架层面的AC-DC整流环节,或者允许PSU在更高的直流电压下工作,从而提升整体能效。在这一背景下,DC-DC转换级的性能成为了决定系统整体效率的关键短板 。

1.3 99%效率的终极目标

面对极为严苛的能效要求,行业标准如80 PLUS Titanium规定了96%的半载效率。然而,为了满足AI数据中心的极致需求,电源设计工程师们正在向97.5%、98%乃至99%的峰值效率发起冲击。实现这一目标,仅靠传统的硅(Si)基功率器件和硬开关拓扑已难以为继。必须引入宽禁带(WBG)半导体材料——特别是碳化硅(SiC)MOSFET,并结合先进的软开关拓扑结构。

在此背景下,三相交错并联LLC(Three-Phase Interleaved LLC)谐振转换器拓扑,凭借其天然的纹波抵消特性、自动均流能力和极高的功率密度潜力,成为了AI算力电源DC-DC级的首选方案。结合基本半导体(Basic Semiconductor)等厂商推出的先进SiC MOSFET技术,这一拓扑正在重新定义高性能电源的标准。

2. 三相交错并联LLC拓扑:原理、优势与技术演进

LLC谐振转换器因其能够在全负载范围内实现原边零电压开通(ZVS)和副边零电流关断(ZCS),长期以来一直是高效电源的核心拓扑。然而,单相LLC在处理大功率(>3kW)时面临着谐振电流有效值(RMS)大、输出纹波电流高、变压器体积庞大等局限。三相交错并联LLC拓扑应运而生,它通过巧妙的相位控制和磁路设计,完美解决了这些痛点。

2.1 三相交错运行的基本原理

三相交错并联LLC本质上是将三个独立的半桥或全桥LLC谐振单元并联,但在控制上对驱动信号施加120°(2π/3)的相移。也就是A相、B相、C相的开关动作在时间轴上依次错开三分之一的开关周期 。

2.1.1 纹波抵消效应(Ripple Cancellation)

这是三相交错拓扑最核心的优势。在单相LLC中,输出整流电流呈现为两倍开关频率(2fsw)的脉动波形,且在半个周期内归零,导致巨大的交流纹波分量流向输出电容。这不仅要求使用大容量的电解电容或大量的陶瓷电容来吸收纹波,还会导致电容发热,影响系统寿命。

在三相交错系统中,总输出电流Itotal(t)是三相电流之和:

Itotal(t)=ia(t)+ib(t−Ts/3)+ic(t−2Ts/3)

由于各相电流波形之间存在120°的相位差,其基波和低次谐波分量在汇流点相互抵消。数学分析表明,总输出电流的纹波频率提升至开关频率的6倍(6fsw),而纹波幅值大幅下降。这种“纹波交错抵消”效应使得设计者可以使用极小容量的输出电容,甚至仅靠陶瓷电容即可满足纹波电压要求,从而显著提升了功率密度并延长了电源寿命 。

2.1.2 热分布与RMS电流降低

在单机架功率高达5.5kW至12kW的AI电源中,单相处理全部电流会导致功率器件和磁性元件承受极高的热应力。三相交错结构将总功率三分流,每相仅承担1/3的功率。由于导通损耗与电流的平方成正比(P=I2R),分散电流可以有效降低局部的热点温度。更重要的是,这种分布式的热源设计更利于散热系统的布局,无论是风冷还是液冷,都能获得更均匀的温度场 。

2.2 谐振腔的连接方式:星型(Y)与三角形(Δ)

三相LLC并非简单的三个模块并联,其原边谐振腔的连接方式决定了系统的均流特性和控制复杂度。

2.2.1 星型(Y)连接与自动均流

最常见的连接方式是原边谐振腔(或变压器原边绕组)呈Y型连接,且中性点悬空。根据基尔霍夫电流定律(KCL),流入中性点的电流之和必须为零:

ia+ib+ic=0

这一物理约束强制三相电流必须保持平衡。如果某一相的谐振参数(如Lr,Cr)与其他相存在偏差导致电流试图增大,中性点电位会自动发生漂移(Neutral Point Shift),从而抑制该相电流的增加并提升其他相的电流,直至达到新的平衡。这种**固有的自动均流(Automatic Current Sharing)**机制是三相LLC相对于简单并联LLC的巨大优势,它极大地简化了控制算法,无需复杂的逐相电流控制环路即可保证三相功率的均衡 。

2.2.2 三角形(Δ)连接

三角形连接通常用于对电压增益有特殊要求的场合。虽然Δ连接在某些工况下能提供更高的输出电压能力,但它缺乏Y型连接的强制均流特性,且容易在闭合回路中产生环流(Circulating Current),特别是在三相参数不完全一致时。因此,在追求高可靠性和简化控制的AI服务器电源中,Y型连接更为普遍 。

2.3 磁集成技术(Integrated Magnetics)

为了进一步提升功率密度,三相LLC通常采用磁集成技术。传统的单相LLC需要独立的谐振电感和变压器。而在三相系统中,可以利用三相磁通在时间上的相位差,将三个变压器集成到一个磁芯结构中(例如E-E core的三个柱)。在中心柱或磁轭部分,三相磁通相互抵消,从而减小了磁芯截面积和磁损耗。

“矩阵变压器”(Matrix Transformer)是近年来的技术热点。它将变压器分散为多个主要通过PCB绕组实现的小型变压器单元,通过原边串联、副边并联的方式组合。这种结构非常适合扁平化的ORv3电源设计,能够利用PCB绕组实现高度一致的参数控制,进一步增强三相LLC的均流效果,并极大地降低了变压器的高度,适应1U甚至更薄的服务器机箱 。

2.4 控制策略的演进

虽然三相LLC具有自动均流特性,但在极高效率要求下(>98%),微小的参数差异仍可能导致效率下降。现代控制策略已从模拟转向全数字控制(Digital Control)。利用高性能MCU(如ST STM32G4或TI C2000系列),可以实施更复杂的控制算法:

切相控制(Phase Shedding): 在轻载时,关闭其中一相或两相,使剩余相工作在更高效率的负载点,从而解决LLC在轻载下效率通过循环能量损耗降低的问题 。

自适应死区时间控制: 根据负载电流实时调整死区时间,确保在所有工况下实现ZVS,同时最小化体二极管导通时间。

同步整流(SR)精准控制: 在三相交错中,SR信号的生成需要精确的相位控制,数字控制器可以基于感测到的原边电流过零点,精准生成互补的SR驱动信号 。

3. 碳化硅(SiC)MOSFET:突破硅基极限的关键赋能者

三相交错并联LLC拓扑虽然在理论上具有诸多优势,但要实现99%的转换效率,物理层面的器件性能至关重要。传统的硅基超结(Superjunction)MOSFET在开关速度、反向恢复特性和高温性能上已逼近物理极限,难以满足AI算力电源对高频、高压和高密度的需求。碳化硅(SiC)作为第三代宽禁带半导体,以其卓越的物理特性成为了这一领域的破局者。

3.1 宽禁带材料的物理优势

SiC的禁带宽度是硅的3倍,临界击穿电场是硅的10倍,热导率是硅的3倍。这些物理属性转化为器件层面的巨大优势:

超低导通电阻(Specific RDS(on)): 得益于高击穿场强,SiC MOSFET可以采用更薄、掺杂浓度更高的漂移层。这意味着在相同的耐压等级(如650V或750V)下,SiC芯片的面积可以比硅小得多,或者在相同面积下实现极低的导通电阻(如10mΩ至25mΩ)。这直接降低了LLC原边的大电流导通损耗 。

高温稳定性: 硅MOSFET的导通电阻随温度升高而急剧增加(在150°C时可能增加2.5倍以上),导致高温下效率雪崩式下跌。相比之下,SiC MOSFET的导通电阻温度系数较小(通常增加1.3-1.5倍)。在AI服务器长期满载、环境温度较高的工况下,SiC的这一特性对于维持高效率和防止热失控至关重要 。

3.2 开关特性的革命性提升

LLC虽然是软开关拓扑,但要实现高频化(>200kHz甚至500kHz)以减小磁性元件体积,器件的动态参数极为关键。

极低输出电容(Coss)与关断能量(Eoff): SiC MOSFET的Coss远小于同规格的硅器件。在LLC中,实现ZVS需要谐振电流在死区时间内抽走Coss上的电荷。较小的Coss意味着只需要较小的磁化电流(Im)即可实现ZVS。这允许设计者增大励磁电感(Lm),从而减小原边环流损耗,提升轻载效率。同时,极快的关断速度将关断损耗(Eoff)降至忽略不计 。

体二极管特性(Body Diode): 虽然LLC正常工作时体二极管不导通,但在启动、过载或动态跳变瞬间,体二极管可能会导通。硅MOSFET体二极管的反向恢复电荷(Qrr)极大,一旦发生硬反向恢复,可能导致器件失效或产生巨大EMI。SiC MOSFET的体二极管Qrr极低(通常仅为硅的1/10),使其极其坚固,且反向恢复损耗极低,大幅提升了系统的鲁棒性 。

3.3 封装技术的创新:Kelvin Source与银烧结

为了释放SiC芯片的潜能,封装技术必须同步进化。

Kelvin Source(开尔文源极): 传统的3引脚封装(如TO-247-3)中,源极引脚同时承载功率回路的大电流和栅极驱动回路的回路电流。大电流变化率(di/dt)在引脚寄生电感上产生的感应电压会反馈到栅极,减缓开关速度并增加开关损耗。TO-247-4或TOLL封装引入了独立的Kelvin Source引脚,将驱动回路与功率回路解耦,消除了源极电感的负反馈效应,使SiC MOSFET能够以极高的速度开关,显著降低Eon和Eoff 。

银烧结(Silver Sintering): 随着功率密度的提升,芯片散热成为瓶颈。传统焊料的导热率仅为50 W/mK左右,且熔点低,耐功率循环能力差。基本半导体等厂商在先进SiC模块和分立器件中采用了银烧结工艺。纳米银膏在烧结后形成纯银连接层,熔点高达962°C,导热率超过200 W/mK。这不仅将结壳热阻(Rth(j−c))降低了20%-40%,还极大地提升了器件在高温波动下的可靠性,完美契合AI服务器频繁的算力突发带来的热冲击 。

4. 基本半导体(Basic Semiconductor)SiC产品线对AI电源的赋能解析

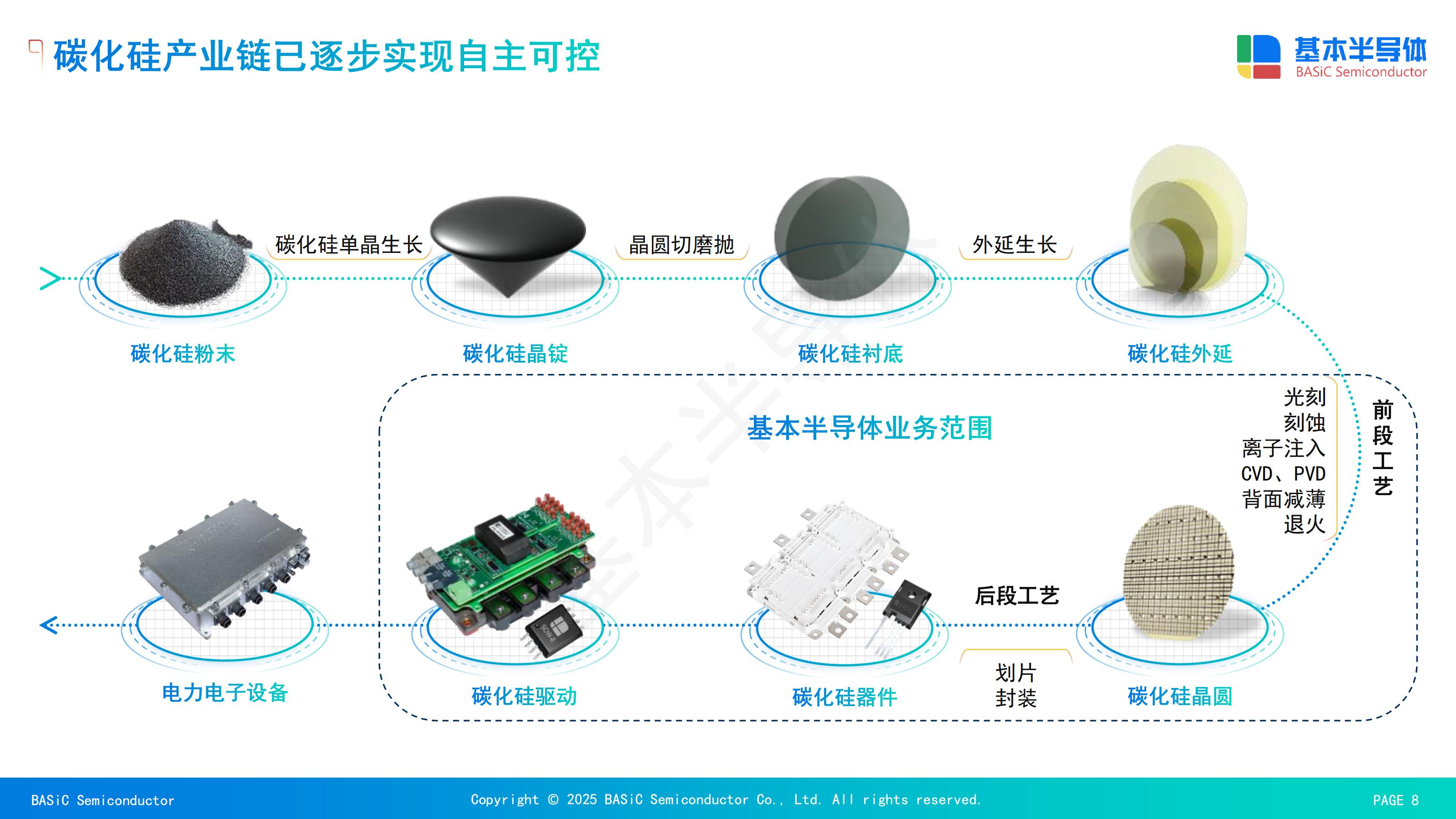

基本半导体(BASiC)已经构建了完整的SiC生态系统,覆盖了从分立器件到功率模块,再到驱动芯片的全链条,精准对接AI算力电源的高效能需求。

4.1 B3M系列第三代SiC MOSFET:为效率而生

基本半导体的B3M系列SiC MOSFET代表了当前行业的一流水平,其参数针对高频硬/软开关拓扑进行了深度优化。

4.1.1 750V电压等级的战略意义

在资料中,B3M010C075Z、B3M025075Z等型号均采用了750V的耐压设计 。

设计洞察: 传统的650V器件在400V输入总线的应用中,电压裕量较小(仅250V),在应对电网浪涌或负载瞬变时风险较高。而1200V器件虽然耐压足够,但导通电阻和成本较高。750V电压等级是一个完美的平衡点,它为400V/48V直流变换器提供了充足的安全裕量,同时保持了接近650V器件的优异导通性能。这对于追求零故障率的AI数据中心至关重要 。

4.1.2 关键型号性能解析

B3M010C075Z (TO-247-4, 750V, 10mΩ):

极致低阻: 10mΩ的导通电阻意味着在有效值电流高达50A-60A(对应单相约20kW级别)时,导通损耗依然极低。这是实现超大功率(如30kW以上)电源模块的核心器件。

银烧结技术应用: 该器件明确采用了银烧结工艺,热阻Rth(j−c)低至0.20 K/W。这意味着在同样的散热条件下,它可以承受更大的损耗,或者在同样的损耗下保持更低的结温,从而进一步降低RDS(on)(利用SiC的正温度系数特性),形成良性循环。

应用场景: AI服务器电源架的主PFC级或LLC原边主开关。

B3M025065B (TOLT, 650V, 25mΩ):

顶部散热(Top-Side Cooling): TOLT封装是当前高密度电源的宠儿。它将热量直接从器件顶部导出到散热器,而不经过PCB。这不仅大幅降低了热阻,还释放了PCB底部的布线空间,使得在有限的体积内实现复杂的信号走线(如三相交错控制信号)成为可能。

应用场景: 超高密度(>100W/in³)的刀片式AI服务器电源模块。

B3M025065L (TOLL, 650V, 25mΩ):

低寄生电感: TOLL封装具有极低的引脚电感(约2nH),配合Kelvin源极,非常适合MHz级别的超高频开关,有助于将无源元件体积缩减到极致。

4.2 BTP1521P:被忽视的幕后英雄——辅助电源芯片

在讨论大功率SiC时,往往容易忽视辅助电源的作用。资料中提到的BTP1521P是一款正激DC-DC开关电源芯片 。

高频特性: 其工作频率可编程高达1.3MHz。这一点至关重要。在SiC驱动应用中,为了隔离高压侧和低压侧,同时也为了抑制高dv/dt带来的共模噪声,驱动电源的变压器往往需要极小的原副边电容。高频化允许使用体积极小、匝数极少的变压器,从而减小寄生电容,提升驱动电路的抗干扰能力(CMTI)。

系统赋能: 它为SiC MOSFET的栅极驱动器(如基本半导体的BTD25350系列)提供稳定、隔离的电源,确保SiC MOSFET能够快速、可靠地开关。没有高性能的辅助电源,SiC的高频优势将无从发挥 。

5. 实现接近99%效率的系统级设计方案

要达成99%的转换效率,单一器件的替换是不够的,必须进行系统级的损耗预算与优化。以下基于三相交错并联LLC拓扑与基本半导体SiC器件的组合,构建一个高效率设计模型。

5.1 损耗分解与优化策略

在一个典型的3kW-12kW AI服务器电源DC-DC级中,损耗主要来源于以下几部分:

| 损耗类型 | 来源 | 传统Si方案瓶颈 | SiC与三相交错方案的优化 |

|---|---|---|---|

| 原边导通损耗 | MOSFET Irms2×RDS(on) | Si MOSFET RDS(on)随温度升高快,且难以做到极低阻值而不牺牲开关速度。 | 采用B3M010C075Z (10mΩ) 或 B3M025075Z (25mΩ) 。三相交错使单管Irms降为1/3,配合SiC低阻特性,导通损耗降低50%以上。 |

| 原边开关损耗 | 关断损耗 Eoff (开通为ZVS) | Si器件关断拖尾电流大,Eoff显著。 | SiC MOSFET关断速度极快,TO-247-4封装消除源极电感反馈,将Eoff降至微焦耳级别,几可忽略。 |

| 驱动损耗 | Qg×Vgs×fsw | Si Superjunction器件Qg较大。 | Basic Semi SiC MOSFET具有更低的Qg,降低驱动功率需求。 |

| 变压器损耗 | 铜损 + 铁损 | 单一大变压器集肤效应严重,散热难。 | 三相交错矩阵变压器。磁通抵消减小铁损;分散绕组降低电流密度减小铜损;PCB绕组提升一致性。 |

| 副边整流损耗 | SR MOSFET导通损耗 | 大电流下的I2R损耗。 | 采用低压高性能Si MOSFET(如OptiMOS)配合精准的数字同步整流控制,利用三相交错带来的低纹波特性,优化滤波电感损耗。 |

5.2 关键设计参数考量

为了实现99%效率,设计必须在全负载范围内保持ZVS,并让励磁电感电流造成的导通损耗最小化。

死区时间(Dead Time)优化: 由于SiC MOSFET的Coss极小(如B3M025075Z仅190pF),谐振腔充满Coss所需的时间非常短。这意味着死区时间可以设置得非常小(例如<100ns)。过大的死区时间会导致体二极管导通,引入额外压降损耗;而SiC允许极短的死区,最大化了有效占空比,提升了传输效率 。

谐振参数(Lm/Lr)选择: 较大的Lm可以减小原边环流,从而降低轻载和满载时的导通损耗。SiC MOSFET优异的开关速度和低Coss使得即使在较大Lm(较小励磁电流)的情况下也能实现ZVS,从而打破了传统设计中为了ZVS而牺牲导通损耗的妥协。

5.3 实战案例数据支撑

根据行业参考设计数据 ,采用650V/750V SiC MOSFET构建的5.5kW三相交错LLC转换器,在半载(50%负载)条件下可测得效率高达98.95% 。

输入电压: 400V DC

输出电压: 50V DC

开关频率: 200kHz - 300kHz

功率密度: >170 W/in³

这一数据有力证明了“三相拓扑 + SiC器件”是通往99%效率的必由之路。

6. 未来技术趋势展望(2025-2026)

随着AI算力需求的持续井喷,电源技术并未止步。

6.1 垂直供电(Vertical Power Delivery)与TOLT/TOLL/QDPAK封装

为了减少主板上从电源到GPU的“最后一厘米”路径上的I2R损耗,电源模块正在从机箱后部移至GPU芯片的正下方,即“垂直供电”。这对电源模块的高度和散热提出了极致要求。基本半导体的B3M025065B (TOLT) 和 B3M025065L (TOLL) 封装器件,凭借其超薄的外形和卓越的顶部/底部散热能力,正是为这一趋势量身定制的 。

6.2 800V HVDC生态的成熟

NVIDIA等巨头正在推动数据中心向800V直流母线迁移,以支持单机柜1MW的功耗 。这将推动1200V SiC MOSFET在LLC中的应用。基本半导体已布局了1200V的SiC MOSFET及模块(Pcore系列),为下一代架构做好了技术储备。

6.3 数字化与智能化的深度融合

未来的三相LLC将不再仅仅是电力转换单元,更是数据中心能源网络的智能节点。通过集成高速MCU和AI算法,电源将能够实时预测GPU负载波动,动态调整三相的相位和频率,甚至在毫秒级时间内响应瞬态负载,实现“比特与瓦特”的联动优化。

7. 结论

AI算力的爆发式增长将数据中心电源技术推向了一个新的历史转折点。传统的电源方案已无法应对当前的高密度与高效率挑战。三相交错并联LLC拓扑,凭借其卓越的纹波抵消与自动均流特性,构建了高功率密度电源的架构基础。而SiC MOSFET,特别是以基本半导体B3M系列为代表的采用银烧结、开尔文源极封装和优化沟槽栅结构的先进器件,则为这一架构注入了灵魂。

二者的结合,不仅在物理上实现了接近99%的极致效率,大幅降低了散热成本,更为未来单机架100kW乃至MW级的AI超算集群提供了坚实的能源保障。对于电源工程师而言,掌握这一组合的设计精髓,即是掌握了通往AI时代的能源钥匙。

8. 附录:基本半导体SiC MOSFET选型参考表(针对AI服务器电源)

为了方便工程师针对不同功率等级的AI电源进行选型,基于现有资料整理如下对比表:

| 型号 | 封装 | 电压 (VDS) | 电流 (ID @25°C) | 导通电阻 (RDS(on) Typ) | 热阻 (Rth(j−c)) | 特性与推荐应用场景 |

|---|---|---|---|---|---|---|

| B3M010C075Z | TO-247-4 | 750 V | 240 A | 10 mΩ | 0.20 K/W | 超大功率首选。银烧结工艺,超低热阻。适合10kW+模块的主功率管。 |

| B3M025075Z | TO-247-4 | 750 V | 111 A | 25 mΩ | 0.38 K/W | 平衡之选。750V高耐压,适合400V/480V输入母线,兼顾成本与性能。 |

| B3M025065B | TOLT | 650 V | 108 A | 25 mΩ | 0.40 K/W | 高密度首选。顶部散热,适合结构紧凑、风道优化的刀片服务器电源。 |

| B3M025065L | TOLL | 650 V | 108 A | 25 mΩ | 0.40 K/W | 小型化首选。低寄生电感,适合超高频开关应用,减小磁性元件体积。 |

| B3M040075Z | TO-247-4 | 750 V | 67 A | 40 mΩ | 0.60 K/W | 性价比之选。适合功率较低的模块或作为并联单元使用。 |

审核编辑 黄宇

-

突破新兴高效能电源要求上的限制2009-02-04 3222

-

有谁清楚LLC的Q值应该如何取值及计算?2018-12-13 13300

-

什么是三相交流电源对称?2021-07-12 1710

-

什么是三相交流电?2008-10-04 7814

-

三相交流电路简介2010-04-14 3052

-

两种高效能电源设计及拓扑分析2011-11-24 2211

-

交错并联双向BuckBoost集成LLC谐振型三端口直流变换器2021-09-27 1936

-

Ti 6.6kw三相交错式PFC参考设计2022-06-15 3285

-

不同功率器件在充电桩三相LLC拓扑中的应用探讨2022-11-23 5039

-

基于dsPIC33CK256MP508实现的三相交错LLC PWM发波逻辑2023-07-22 8821

-

三相交流电路的功率计算2023-09-22 12870

-

中频三相焊接电源技术在现代制造业中的应用与发展探析2024-11-16 987

-

如何实现480V/60Hz变380V/50Hz三相变频电源的高效能转换2024-11-20 2509

-

三相交流恒流源每相独立可调2026-01-04 654

-

新品 | 碳化硅SiC 5.5kW三相交错并联LLC谐振变换器评估板2026-01-26 649

全部0条评论

快来发表一下你的评论吧 !