如何避免晶振不起振?(附检查清单)

电子说

描述

晶振是电路的心脏,它不起振,整个系统就无法工作。要系统地解决这个问题,可以从“设计、布局、物料、调试” 四个层面入手。

设计阶段:从根源上规避风险

这是最关键的一步,正确的设计可以避免90%以上的问题。

1、正确选择负载电容

晶振数据手册上会指定一个负载电容值。这个值并不是晶振本身的电容,而是指从晶振两个引脚向电路看进去的总等效电容。它包括MCU的内部电容、PCB的寄生电容以及外部匹配电容。

2、选择合适的反馈电阻

这个电阻(通常标记为Rf,阻值为1MΩ )并联在晶振的两个引脚之间。它为内部反相放大器提供直流负反馈,使其工作在线性区,便于起振。

3、考虑串联电阻

这个电阻(Rs)串联在晶振的一个引脚和MCU的振荡器输入引脚之间。它主要用于限制振荡幅度和抑制高次谐波,防止过驱动而损坏晶振,同时也能提高稳定性。

PCB布局与布线:减少寄生效应

糟糕的布局是导致不起振的隐形杀手。

靠近MCU放置:晶振、匹配电容必须尽可能地靠近MCU的振荡器引脚放置,以最小化走线长度。

走线短而粗:晶振的走线应尽可能短、粗,以减少寄生电感和电容。

用地平面隔离:在晶振电路下方设置一个完整的地平面,并用地过孔将匹配电容的地端直接连接到地平面。这可以为高频噪声提供最短的返回路径。

避免与其他信号线交叉:晶振走线周围要用“地护卫”包围,并远离任何高频、快速变化的信号线(如时钟线、数据线、电源线),防止噪声耦合。

外壳接地:如果晶振有金属外壳,通常建议将其接地,以起到屏蔽作用。

物料选择:保证器件质量

晶振质量:使用来自知名、可靠供应商的晶振(例如:晶宝股份生产的晶振)。劣质晶振可能导致参数不达标、一致性差或易损坏。

电容精度:匹配电容应使用高精度、低温漂的陶瓷电容,如NP0/C0G材质。避免使用精度差、温漂大的Y5V/X7R电容。

MCU配置:确认MCU的振荡器模式配置正确(例如,是HSI还是HSE,是高增益模式还是低增益模式)。某些MCU需要软件配置正确的驱动强度。

调试与故障排查

当问题已经发生时,可以按照以下步骤排查:

1.确认软件配置:首先检查MCU的固件是否正确配置了外部高速时钟,并正确完成了时钟树的初始化。

2.用示波器测量

使用高阻抗探头(如10X),因为1X探头本身的电容(通常10-15pF)会严重干扰振荡电路。

测量晶振的两个引脚,观察是否有正弦波。注意:探头接触的瞬间可能导致停振或起振,这是正常的。

如果完全没有波形,说明未起振。

如果波形幅度很小或失真,可能是负载电容不匹配或驱动强度不合适。

3.替换法

尝试更换一个已知良好的晶振。

尝试更换匹配电容。

4.调整匹配电容

如果没有起振,可以尝试减小匹配电容的值(例如从22pF换为15pF),这会降低负载电容,可能更容易起振。

如果起振但波形不稳定或幅度过大,可以尝试增大匹配电容或串联电阻来优化。

5.检查焊接和电源

检查晶振、电容是否有虚焊、连锡。

确保MCU的电源电压稳定、干净。不稳定的电源也会导致振荡不稳定。

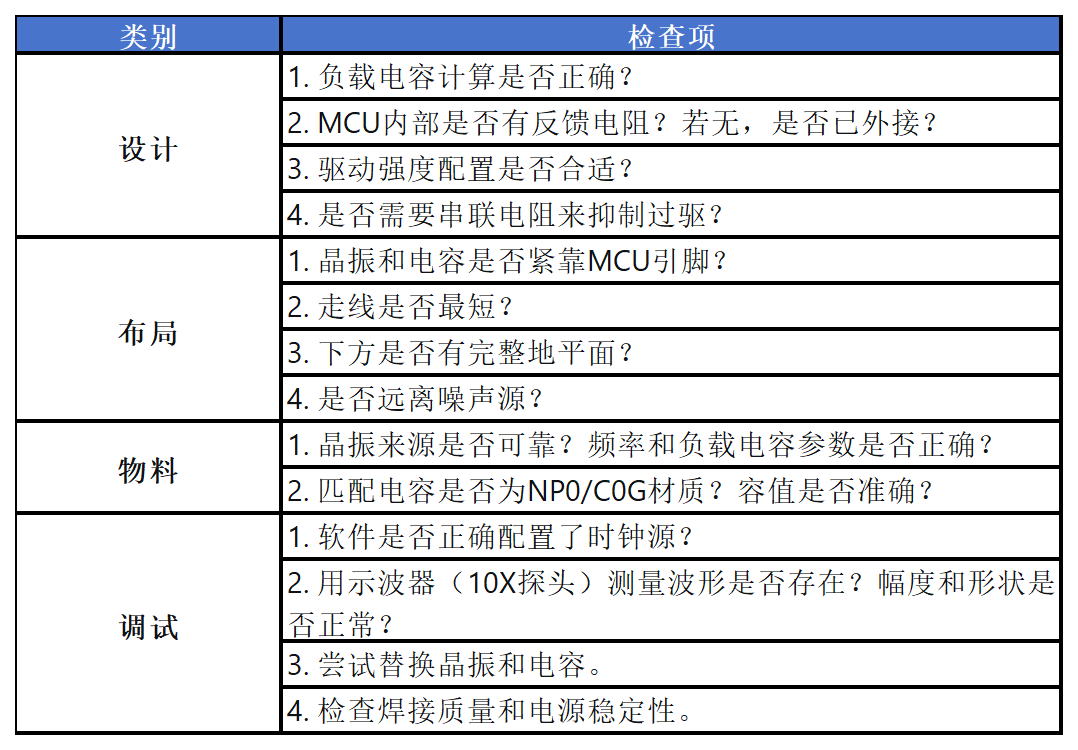

附:避免晶振不起振的检查清单

审核编辑 黄宇

全部0条评论

快来发表一下你的评论吧 !