瑞萨RA系列FSP库开发实战指南之SPI通讯协议的结构和功能

描述

22.2

瑞萨SPI功能框图

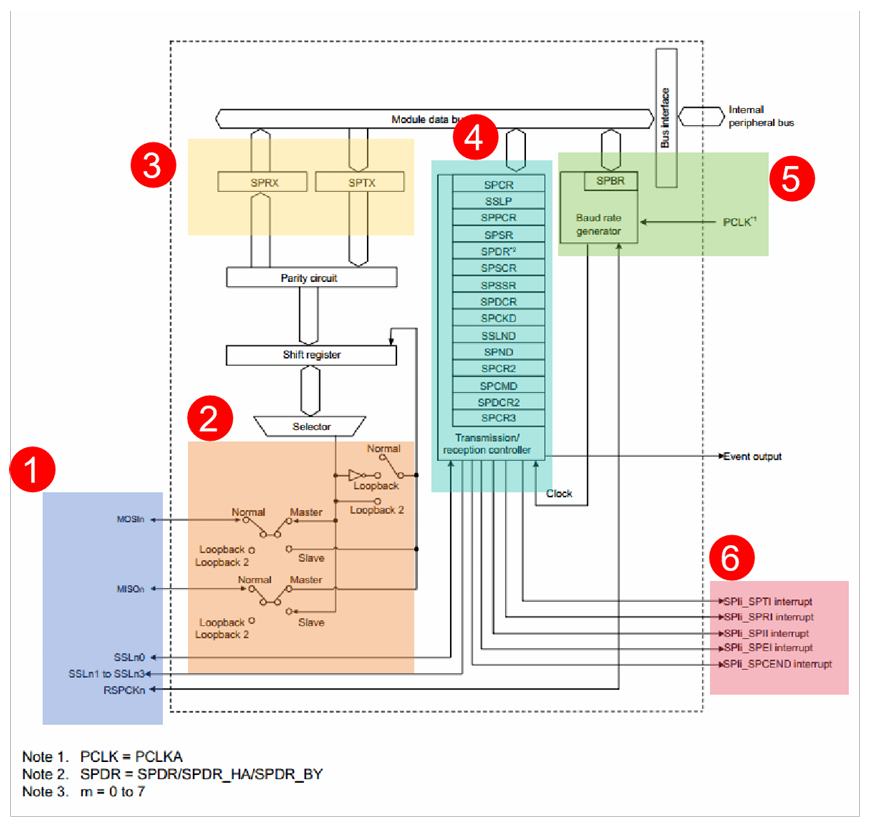

以RA6M5为例,SPI的功能结构框图如下图所示。接下来我们大致地研究一下它的结构和功能。

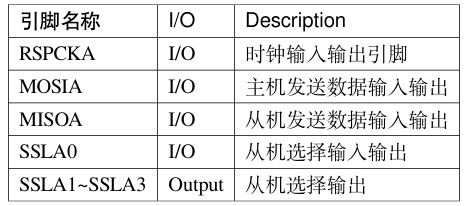

见图注1,瑞萨RA6M5有两个SPI外设,分别是SPI0,SPI1,每个SPI都有2~3组,下面是关于SPI各引脚的说明,以SPI0_A为例,见下表,其中值得一提的是,当MCU作为主机时,有多个从机时,从机可通过SSLA0~SSLA3作为片选信号线来连接主机,而当MCU作为从机时,则通过SSLA0作为片选线连接主机。

SPI_0的IO引脚描述:

注

SPI0的引脚名称表示为“⋯A”或“⋯An”,SPI1的引脚名称表示为“⋯B”或“⋯Bn”(n=0、1、2或3)。

见图注2,其中:

• Master:主机通讯模式

• Slave:从机通讯模式

• Normal:正常通讯模式

• Loopback:环回模式1(接受数据=反转发送数据)

• Loopback:环回模式2(接受数据=发送数据)

见图注3,其中:

• SPTX:发送缓冲器

• SPRX:接受缓冲器

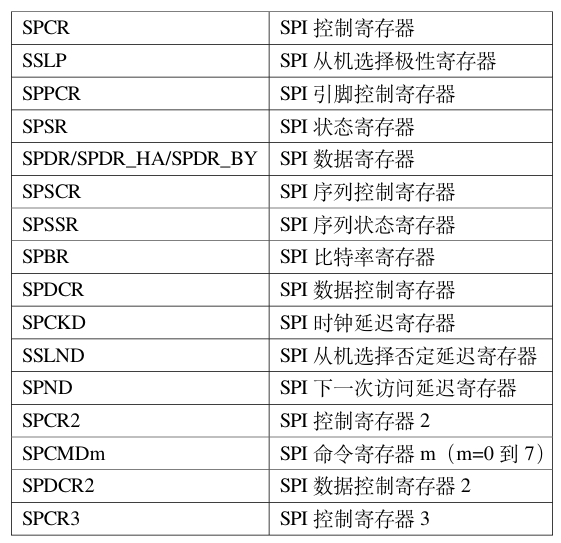

见图注4,对于瑞萨RA6M5的SPI外设的寄存器介绍,见下表:

SPI的寄存器

注

我们这里主要介绍的是瑞萨的fsp库的使用,所以在这里寄存器我们在这里做一些简单的介绍。

见图注5,SPI波特率设置由寄存器SPBR与SPMDm.BRDV[1:0]设置的组合在主模式下设置。当SPI处于从机模式时,比特率取决于输入时钟PCLKA的比特率,与SPBR和SPMDm.BRDV[1:0]位(比特率分频设置)的设置无关。

见图注6,其中:

• SPIi_SPRI:接收缓冲区满事件输出。

• SPIi_SPTI:发送缓冲区空事件输出。

• SPIi_SPEI:模式故障、欠载、溢出或奇偶校验错误事件输出。

• SPIi_SPII:SPI空闲事件输出。

• SPIi_SPCEND:传输完成事件输出。

-

瑞萨RA系列FSP库开发实战指南之QSPI通讯协议简介2026-03-03 4804

-

瑞萨RA系列FSP库开发实战指南之SPI通讯协议的物理层和协议层简介2026-02-04 12300

-

瑞萨RA系列FSP库开发实战指南之I2C读写EEPROM实验2026-01-27 3788

-

瑞萨FSP6.2:RA8新品支持与功能大升级!2025-12-17 755

-

瑞萨电子RA系列微控制器的可扩展性强的配置软件包 (FSP)安装下载与使用指南2025-06-11 2250

-

【瑞萨RA2L1入门学习】RA2L1开发环境搭建2025-03-07 2046

-

瑞萨e2studio(1)----瑞萨芯片之搭建FSP环境2024-09-30 6863

-

使用瑞萨e² studio FSP基于RA2E1定时器配置PWM输出2023-08-01 2251

-

基于瑞萨RA4M2的表盘设计2023-03-22 1547

-

【瑞萨RA4系列开发板体验】体验过程2022-12-18 2691

-

【瑞萨RA4系列开发板体验】10. 我的试用总结2022-12-10 3224

-

【视频教程】瑞萨RA单片机FSP开发(3)FSP架构-解释Blinky架构[上]2022-12-06 2148

-

【瑞萨RA4系列开发板体验】开发环境搭建和新手点灯指南2022-11-24 6065

-

【有奖直播预报名】瑞萨电子RA系列产品开发工具之FSP4.0.0新特性介绍2022-11-22 1715

全部0条评论

快来发表一下你的评论吧 !