与非门逻辑介绍

电子说

描述

与非门介绍

先通过文章《非门(反相器)介绍》了解什么是PMOS,什么是NMOS,以及基本的上下拉CMOS逻辑的概念。

与非门实现的逻辑功能为所有的输入信号,只要有一个为低电平(0),则输出为高电平。以2输入与非门为例,其图示如下。其中in1,in2为两个输入信号,out为输出。

其逻辑真值表如下。

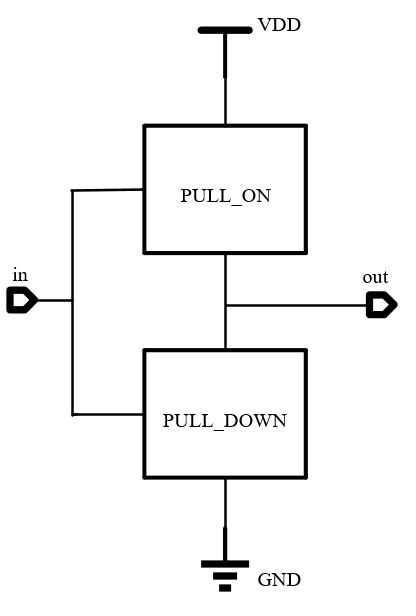

所有逻辑门电路的CMOS结构分为上下拉两部分,上拉为PMOS结构,下拉为NMOS结构。

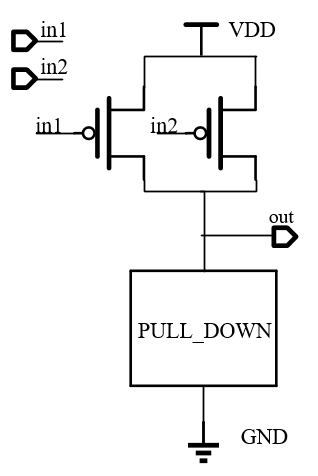

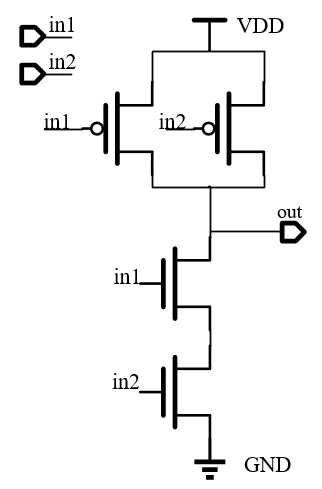

我们来分析一下对于2输入与非门上拉逻辑要实现的功能:即当in1,in2有任何一个为0时,上拉通路就导通,使得out与VDD相连。故上拉逻辑由两个PMOS管并联。PMOS管只有当G端为0时,D与S两端才导通,故如下图所示,当in1,in2任何一个为0时,out便与VDD导通,满足条件。

我们接着分析2输入与非门下拉网络要实现的功能:只要当两个输入都为1时(高电平),那么下拉网络才导通,使得out与地相连,输出为0。根据这个要求,故下拉网络由两个NMOS管串联。NMOS管只有当G端为1时,D与S两端才导通,故两个NMOS管串联,当两个NMOS管都导通,out才跟地端相连了,符合要求。

故同样分析,3输入与非门上拉网络为3个PMOS管并连,下拉网络为3个NMOS管串联。

或逻辑的Verilog描述符为 “&”。

当用数据流方式描述时,Verilog语言如下:

assign out = in1 & in2;

当用结构级语言描述时(即与门电路的例化),Verilog语言如下,and为或的关键字:

and(out,in1,in2);

或非的关键字为nand,如果是做或非操作,例化或非门的方式如下:

nand(out,in1,in2);

问题:那么怎么由CMOS结构实现与门呢?

答:在与非门后面加个反相器。

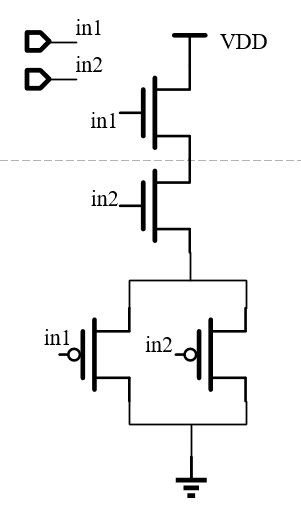

问题:为什么不能如下图所示,由NMOS做上拉网络,而PMOS做下拉网络实现与逻辑呢?

答:因为NMOS做上拉网络会有阈值损失,PMOS做下拉网络也会有阈值损失。

-

TTL与非门的电压传输特性 TTL与非门的静态输入与输出特性2024-01-23 7570

-

仅使用与非门的基本逻辑门2022-09-12 13681

-

【数字电路】关于逻辑与非门电路设计的教程分析2021-01-22 11312

-

与非门搭接的逻辑电路原理图免费下载2020-10-12 1156

-

逻辑与非门等效教程和功能2019-06-26 11788

-

MOS与非门或非门构成原理2019-06-25 28396

-

两个与非门电路的介绍2019-01-09 5370

-

与非门实现非门功能方法介绍2018-07-26 56970

-

与非门,与非门是什么意思2010-03-08 12481

-

与非门逻辑符号2009-04-06 2927

-

逻辑与非门2008-06-12 2016

全部0条评论

快来发表一下你的评论吧 !