射频CC1000电路连接图分析 浅谈CC1000应用电路

无线通信电子电路图

描述

本文主要是关于CC1000电路的相关介绍,并着重射频CC1000电路连接图进行了详尽的阐述。

CC1000

CC1000是根据Chipcon公司的SmartRF技术,在0.35μm CMOS 工艺下制造的一种理想的超高频单片收发通信芯片。它的工作频带在315、868及915MHz,但CC1000很容易通过编程使其工作在300~1000MHz范围内。它具有低电压(2.3~3.6V),极低的功耗,可编程输出功率(-20~10dBm),高灵敏度(一般-109dBm),小尺寸(TSSOP-28封装),集成了位同步器等特点。其FSK数传可达72.8Kbps,具有250Hz步长可编程频率能力,适用于跳频协议;主要工作参数能通过串行总线接口编程改变,使用非常灵活。

三线串行数据口

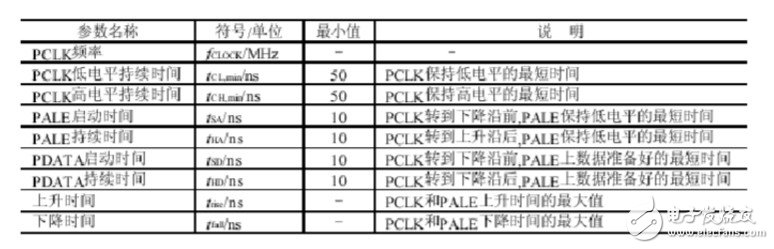

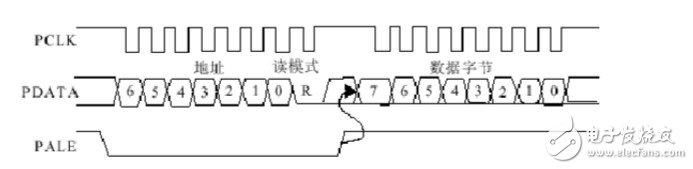

CC1000 可通过简单的三线串行接口(PDATA、 PCLK 和PALE) 进行编程,有36个8位配置寄存器,每个由7位地址寻址。一个完整的CC1000配置,要求发送29个数据帧,每个16位(7个地址位,1个读/写位和8个数据位)。PCLK 频率决定了完全配置所需的时间。在10MHz的PCLK频率工作下,完成整个配置所需时间少于60μs。在低电位模式设置时,仅需发射一个帧,所需时间少于2μs。所有寄存器都可读。在每次写循环中,16位字节送入PDATA通道,每个数据帧中7个最重要的位(A6:0)是地址位,A6是MSB(最高位),首先被发送。下一个发送的位是读/写位(高电平写,低电平读),在传输地址和读/写位期间,PALE (编程地址锁存使能)必须保持低电平,接着传输8 个数据位(D7: 0),如图3所示。表1是对各参数的说明。PDATA 在PCLK 下降沿有效。当8位数据位中的最后一个字节位D0 装入后,整个数据字才被装入内部配置寄存器中。经过低电位状态下编程的配置信息才会有效,但是不能关闭电源。

微控制器通过相同的接口也能读出配置寄存器。首先,发送7位地址位,然后读/写位设为低电平,用来初始化读回的数据。接着,CC1000从寻址寄存器中返回数据。此时,PDATA 用作输出口,在读回数据期间(D7:0),微控制器必须把它设成三态,或者在引脚开路时设为高电平。

CC1000采用锁相环技术,发射频率是通过内部的频率合成器来配置的,可配置的范围为300~1000MHz,适合应用跳频协议,一般可配出10或20个频点,该芯片灵敏度为-109dBm,并可自动校准,可编程输出功率为-20dBm~+10dBm,通信速率可达78.6Kbps。

CC1000的主要工作参数可由一个串行接口编程设定,使用非常方便并且具有灵活性。CC1000芯片的外围元件较少,且对精度要求不高,并提供三种编码方式与微控制器接口。所以CC1000与一个微控制器和少数几个外接元件便可组成一个完整的RF收发系统。

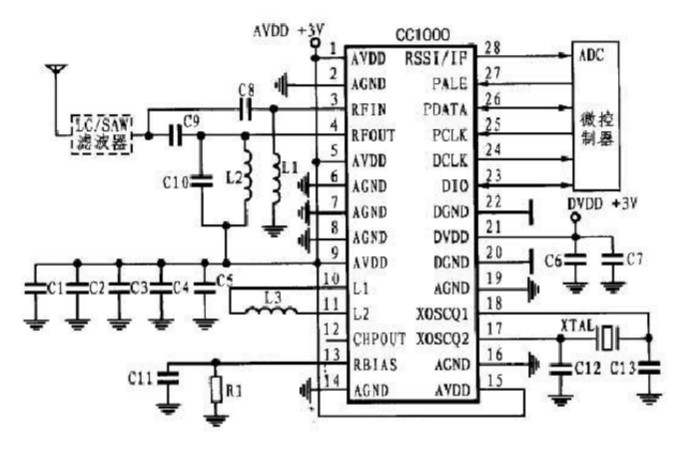

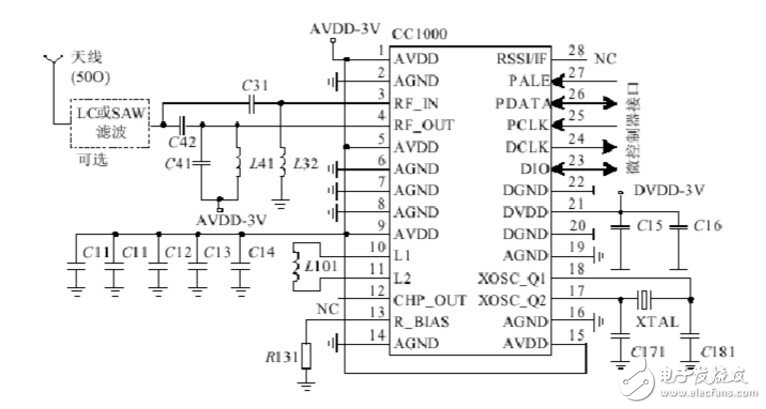

射频CC1000电路连接图分析

上图是CC1000的一个典型的应用电路,调节元器件C1-C13 、L1-L3、R1的参数值可使

CC1000工作在不同工作频率(300~1000MHz)。

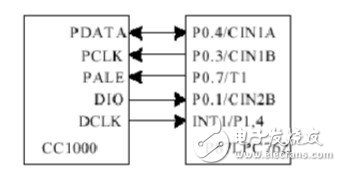

微控制器可以通过CC1000的串行接口(PDATA、PAlE和PCLK)对CC1000进行设置,通过CC1000的DIO完成数据的接收和发送。

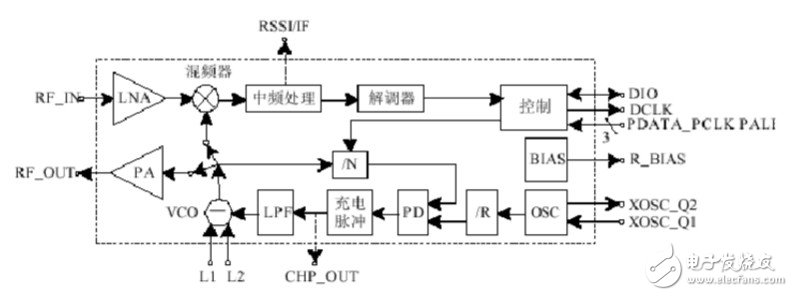

图1显示了cc1000的简化框图。在接收模式下,可以将cc1000视为传统的超外差接收机。射频(RF)输入信号由低噪声放大器(LNA)放大并翻转到混频器中。中频(IF)信号是通过将RF输入信号混入混频器而产生的。在中频处理阶段,在将信号发送到解调器之前,对信号进行放大和滤波。可选的RSSI信号和IF信号也可以通过引脚混合RSSI/IF产生。解调后,CC1000从管脚DIO输出解调后的数字信号,通过芯片上的PCLK提供的时钟信号完成解调信号的同步。

在发送模式中,压控振荡器(VCO)的输出信号直接馈送到功率放大器(PA)中。射频输出是由添加到DIO脚的数据控制的,称为FSK。这种内部T/R切换电路使得天线连接和匹配的设计更容易。它

由频率合成器产生的本地振荡器在接收状态下被馈送到功率放大器。频率合成器由晶体振荡器(XOSC)、鉴相器(PD)、充电脉冲、VCO和分频器(/R和/N)组成。外部晶体必须连接到XOSC引脚,只有外围电感需要连接到VCO。(2)应用电路

当cc1000工作时,很少有外部组件。典型的应用电路如图2所示。在配置不同的cc1000传输频率时,外围组件的参数也不同。

表1 串行接口时序说明

微控制器还可以通过相同的接口读出配置寄存器。首先,发送7位地址位,然后将读/写位设置为低电平以初始化读取数据。接下来,cc1000从可寻址寄存器返回数据。此时,PDATA被用作输出端口,并且微控制器必须在回读(D7:0)期间将其设置为三个状态,或者在管脚打开时将其设置为高电平。读取操作的时间如图4所示。

与微控制器连接

微控制器使用3个输出引脚用于接口(PDATA、PCLK、PALE),与PDATA相连的引脚必须是双向引脚,用于发送和接收数据。提供数据计时的DCLK 应与微控制器输入端相连,其余引脚用来监视LOCK 信号(在引脚CHP_OUT)。当PLL 锁定时,该信号为逻辑高电平。图5为P87LPC762单片机与CC1000接口示意图。

结语

关于射频CC1000电路连接图的相关介绍就到这了,如有不足之处欢迎指正。

-

基于FSK调制芯片的CC1000编程2018-09-06 4232

-

用于开闭键控(OOK)系统的CC1000的详细资料概述2018-08-01 1717

-

CC10002018-02-05 1812

-

CC1000实现射频光传输模块FSK通信2011-11-21 4231

-

CC1000内部结构框图2010-08-13 1507

-

CC1000,pdf(Single-Chip Very Lo2010-07-06 1111

-

可编程RF收发器芯片CC1000的原理及应用2009-04-29 775

-

cc1000典型应用电路图2008-06-24 1512

-

cc1000中文资料pdf2008-04-14 1521

-

无线收发芯片比较与选择——CC10002006-03-13 3502

-

极低功耗无线收发集成芯片CC10002006-03-11 1873

全部0条评论

快来发表一下你的评论吧 !