PCIe物理层接口定义了物理层中的,媒介层和物理编码子层之间的统一接口

电子说

描述

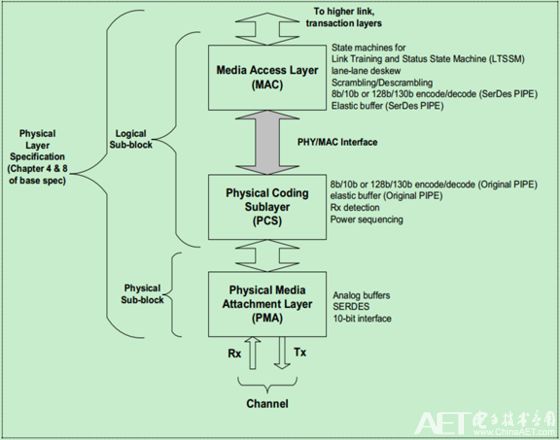

PCIe物理层接口(Physical Interface for PCI Express,PIPE)定义了物理层中的,媒介层(Media Access Layer,MAC)和物理编码子层(Physical Coding Sub-layer,PCS)之间的统一接口,旨在为提供一种统一的行业标准。如下图所示:

其中MAC和PCS都属于PCIe中的物理层逻辑子层部分,而PMA(Physical Media Attachment Layer)则属于物理层电气子层。需要注意的是,PIPE规范是由Intel提出的行业建议,并非PCI-SIG规定的PCIe标准之一。PCIe设备厂家完全可以自主选择是否采用PIPE规范。

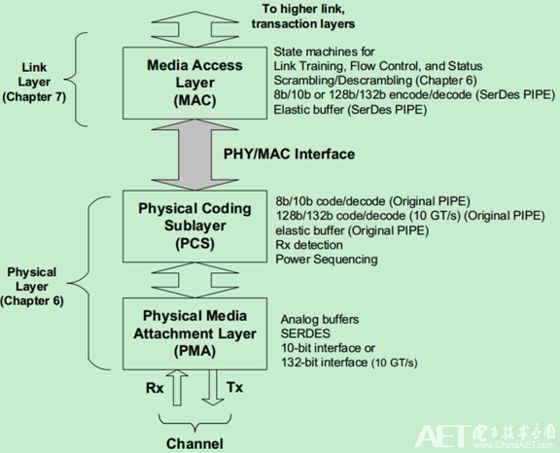

由于业界通常采用SerDes器件(包括FPGA中集成的SerDes模块)来实现PCIe中的PCS和PMA,所以往往MAC(以及事务层和数据链路层等)和PCS/PMA是独立设计的,甚至是不同厂家设计的。为这之间提供统一的行业标准——PIPE,有助于使不同厂家之间的设备有更好的兼容性。当然,也有很多PCIe设备完全是由一个厂家设计的(如部分基于PCIe的ASIC等),此时是否采用PIPE的必要性就不是那么重要了。

随着高速串行技术的发展,各种串行通信技术的物理层逐渐走向了统一,用户甚至可以基于FPGA中的SerDes/PCS完成多种高速串行通信接口的设计。这些通信接口的区别往往只是体现在高层协议(数据链路层与事务层等),在物理层上(尤其是物理层电气子层上)基本上是一致的。

虽然PIPE规范最早是用于PCIe总线中的(从命名方式就可以看出来),但是该规范的后续版本逐渐开始支持了其他的串行接口。以Intel发布的最新版本的PIPE Spec为例(v5.1),该版本涉及PCI Express、SATA、USB、DisplayPort和Converged IO等多种高速串行接口。

USB中的PHY/MAC接口,如下图所示:

详细的PHY/MAC接口(PIPE)的示意图如下(PCIe、USB等):

-

CAN XL物理层揭秘(下):物理层组合与兼容性2024-11-29 1195

-

WLAN物理层关键通信技术2023-05-19 596

-

分析802.11标准在物理层的定义2022-11-09 6774

-

CCIX物理层详解2022-08-15 3217

-

串口通信的物理层与协议层的相关资料推荐2022-02-17 886

-

IIC物理层是由哪些部分组成的2021-12-13 2193

-

什么是以太网物理层?Ethernet物理层有哪些功能?2021-03-18 6094

-

三种不同类型以太网物理层的编码规则和测试分析2019-08-29 29424

-

CAN总线不同的物理层2019-05-23 2832

-

PCIe物理层的基本概念2018-05-02 11371

-

物理层的成帧过程2010-02-09 1413

-

物理层网络编码分组的机会中继2009-11-13 596

-

WCDMA系统的物理层(FDD)2009-06-14 757

-

物理层的作用2008-07-22 7087

全部0条评论

快来发表一下你的评论吧 !