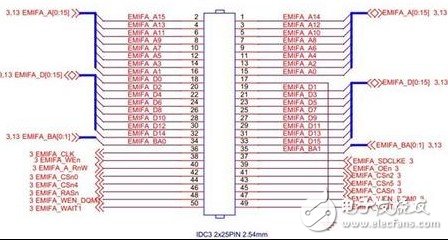

tms320c6748 原理图 浅谈tms320c6748下的DSP系统

电子说

描述

本文主要是关于tms320c6748的相关介绍,并着重对tms320c6748原理图及其DSP子系统进行了详尽的阐述。

tms320c6748

TMS320C6748是德州仪器 (TI) 推出浮点功能的全新高性能处理器 ,这款芯片也是业界功耗最低的浮点数字信号处理器 (DSP),可充分满足高能效、连通性设计对高集成度外设、更低热量耗散以及更长电池使用寿命的需求。不仅具备通用并行端口 (uPP),同时也是 TI 首批集成串行高级技术附件 (SATA)的器件。 广州创龙推出的TL6748-EVM评估套件为开发者使用TI TMS320C6748处理器提供了完善的软件开发环境,系统支持:裸机、SYS/BIOS、DSP/BIOS。提供参考底板原理图,DSP C6748入门教程、丰富的Demo程序、完整的软件开发包,以及详细的C6748系统开发文档,方便用户快速评估TMS320C6748处理器、设计系统驱动及其定制应用软件,也大大降低产品开发周期,让客户产品快速上市。主要面向电力、通信、工控、音视频处理等数据采集处理行业。 TL6748-EVM评估套件是一个功能丰富的开发板,为嵌入式设计人员提供快捷简单的实践方式来评估TMS320C674x系列处理器,是一个完整的实验评估平台。

德州仪器 (TI) 推出浮点功能的全新高性能处理器 —— TMS320C6748,这款芯片也是业界功耗最低的浮点数字信号处理器 (DSP),可充分满足高能效、连通性设计对高集成度外设、更低热量耗散以及更长电池使用寿命的需求。不仅具备通用并行端口 (uPP),同时也是 TI 首批集成串行高级技术附件 (SATA)的器件。

广州创龙推出的TL6748-EVM评估套件为开发者使用TI TMS320C6748处理器提供了完善的软件开发环境,系统支持:裸机、SYS/BIOS、DSP/BIOS。提供参考底板原理图,DSP C6748入门教程、丰富的Demo程序、完整的软件开发包,以及详细的C6748系统开发文档,方便用户快速评估TMS320C6748处理器、设计系统驱动及其定制应用软件,也大大降低产品开发周期,让客户产品快速上市。主要面向电力、通信、工控、音视频处理等数据采集处理行业。

TL6748-EVM评估套件是一个功能丰富的开发板,为嵌入式设计人员提供快捷简单的实践方式来评估TMS320C674x系列处理器,是一个完整的实验评估平台。

tms320c6748下的DSP系统

DSPSS包括C674X核心模块和几块内部存储器。本章给出了DSPSS的概述和以下几条相关内容:

·内存映射

·中断

·电源管理

2.2 TMS320C674X核心模块

由以下几部分组成:

·TMS320C674X CPU

·内存控制器:

-1级程序存储器控制器(PMC)

-1级数据存储器控制器(DMC)

-2级统一内存控制器(UMC)

-扩展内存控制器(EMC)

-内部直接内存访问(IDMA)控制器

·内部外设

-中断控制器(INTC)

-断电控制器(PDC)

-带宽管理(BWM)

·高级事件触发(AET)

2.2.1 内存控制器

C674X核心模块实现了一个两级的存储器架构,其内部存储器基于缓存,外部存储器给予支持。1级存储器(L1)可分成独立的程序存储器(L1P)和数据存储器(L1D)。L1可以通过CPU无延迟地访问。L2也可以分为L2 RAM(正常可寻址的片上内存)和作缓存外部存储器位置用的L2缓存。IDMA管理L1P,L1D和L2存储器之间的DMA。

2.2.2 内部外设

2.2.2.1 INTC

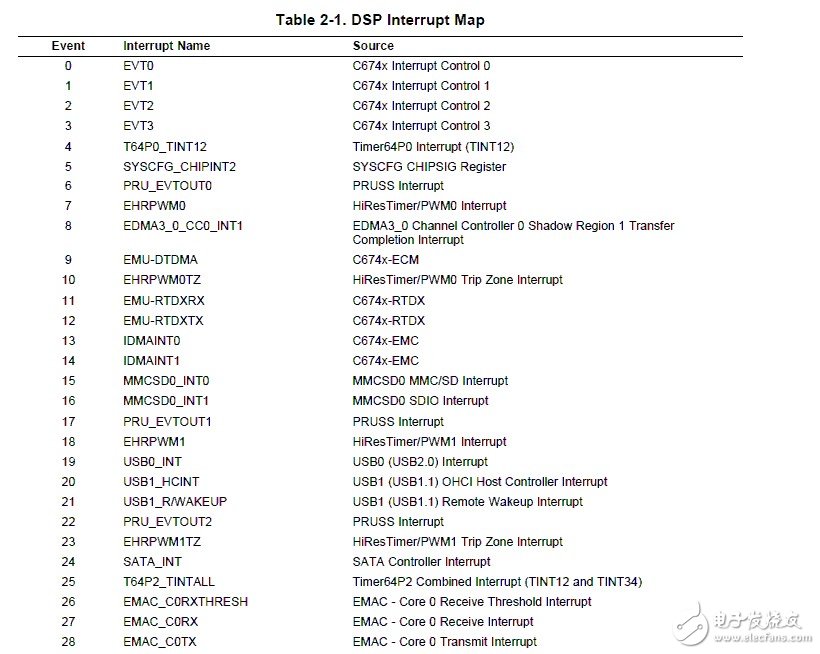

INTC将DSP设备事件映射到12个CPU中断。所有的DSP设备事件都列举在下表中了。

2.2.2.1.1 中断控制寄存器

2.2.2.1.2 NMI中断

除了表2-1中的中断,DSP还支持一个特殊的中断,即不可屏蔽中断(NMI),这个中断表现地更像一个异常。NMI中断受系统配置模块中的两个寄存器控制,芯片信号寄存器(CHIPSIG)和芯片信号清除寄存器(CHIPSIG_CLR)。

2.2.2.2 断电控制器

PDC可以将DSP子系统中的C674X核心模块和内部存储器的所有部分断电,即:

·CPU

·1级PMC

·1级DMC

·2级UMC

·EMC

·IDMA控制器

·L1P存储器

·L1D存储器

·L2存储器

该设备支持C674X核心模块的静态断电特性。

*静态断电:PDC接受软件指令后立即引发整个C674X核心模块和所有内存的断电(时钟门控)。

静态断电(时钟门控)影响C674X核心模块和内存的所有部分。软件可以通过控制PDC命令寄存器(PDCCMD)的一个位来引发断电。

2.2.2.3 BWM

BWM为资源请求程序间的优化带宽提供一个可编程接口,这些请求包括:

·EDMA3引发的DMA传输(并导致一致性操作)

·DSPSS IDMA引发的传输(并导致一致性操作)

·可编程缓存一致性操作

-基于块的一致性操作

-全局一致性操作

·CPU直接引发的传输

-数据存取(加载/存储)

-程序存取

资源包括:

·L1P存储器

·L1D存储器

·L2存储器

·C674X核心模块意外的资源:外部存储器,片上外设,寄存器

由于任何的请求都有可能阻塞资源,造成额外时间损失,带宽管理可以保证所有请求之间的公平。

带宽管理实现了加权优先级驱动的带宽分配。再每次传输时,每个请求(EDMA3,DSPSS IDMA,CPU等)都分配到一个优先级。在整个系统中可编程优先级都是单一不重复的。一共有9个优先级,0是最高优先级而8是最低的。当有几个请求对一块资源产生竞争时,会访问最高优先级的请求。当竞争发生在连续周期时,竞争计数器会保证低优先级请求在每n次仲裁循环中得到1次访问,n是可编程的。-1优先级代表一个由于竞争计数器终止而优先级增加的传输(不懂?),或者是对特定资源有最高优先级的传输。

2.2.2.4 IDMA控制器

IDMA实现C674X核心模块本地任何两块内存位置之间的快速数据块传输。本地内存位置被定义为在L1P,L1D和L2存储器,或者在外部外设配置(CFG)端口。IDMA不能将数据从内部DSP内存映射寄存器空间传入或导出。

2.3 内存映射

2.3.1 DSP内部存储器

2.3.2 外部存储器

(有关章节会详细介绍)

2.4 AET

C674X核心模块支持AET。这一性能可以用来调试复杂问题和理解用户应用程序的性能特点。AET提供了以下功能:

·硬件程序断点:指定可以产生事件的地址或地址序列,例如中断处理器或触发路径捕获。

·数据监视点:指定可以产生事件的数据可变地址,地址序列,或数据值,如中断处理器或触发路径捕获。

·计数器:为性能监测而计算事件或循环发生次数。

·状态排序:为复杂序列精确产生事件而允许硬件程序断点和数据监视点的组合。

结语

关于tms320c6748的相关介绍就到这了,如有不足之处欢迎指正。

- 相关推荐

- 热点推荐

- dsp

- TMS320C6748

-

TMS320C6748/46/42配套产品2024-10-14 478

-

使用TPS650061为TMS320C6742、TMS320C6746和TMS320C6748供电2024-10-10 578

-

TMS320C6748定点和浮点DSP数据表2024-08-07 569

-

德州仪器DSP的TMS320C6748技术手册2022-08-24 1120

-

请问TMS320C6748参考设计2020-05-22 1961

-

基于TI TMS320C6748定点/浮点DSP C674x处理器2019-11-10 4201

-

TMS320C6748 TMS320C6748 Fixed/Floating Point DSP2018-10-15 2024

-

tms320c6748主要参数和原理图 tms320c6748 IO图浅析2018-09-07 16942

-

TMS320C6748固定和浮点DSP硅修订2.3_2.1_2.0_1.1_1.0_英版2016-11-14 866

-

基于StarterWare的TMS320C6748裸机程序开发入门详解教程2016-09-06 1893

-

【TL6748 DSP申请】广州创龙TMS320C6748 DSP开发板免费申请试用2015-09-10 2269

-

TI推出TMS320C6748 DSP与OMAP-L138 DSP+ARM处理器2011-06-17 3804

-

TMS320C6748 Fixed/Floating-Poi2010-12-07 621

全部0条评论

快来发表一下你的评论吧 !