PCB设计软件allegro蓝牙音箱案例实操讲解

电子说

描述

PCB设计软件allegro蓝牙音箱案例实操讲解,以蓝牙音箱为案例将PCB设计基础知识融进实际案例中,通过操作过程讲解PCB设计软件功能及实用经验技巧,本次课程将通过对高速信号布线相关知识的学习,完成PCB布线设计。

本期学习重点:

高速信号设计

高速信号处理

高速信号优化

本期学习难点:

高速信号布线

高速信号优化

一、高速信号布线

高速信号目前已经成为PCB设计的主流,以通信产品为代表的电子类产品呈现高速化、高密化的技术发展趋势,给电路板设计师带来新的技术挑战。电路板设计师除了在实战项目设计中逐步积累高速信号工程经验外,也需要不断刷新自身的知识结构、尤其需要补充在高速信号完整性方面的知识。

常见的高速信号以物理接口分类,包括:USB、RJ45、S-Video、VGA、DVI、HDMI、PCIExpress、PCI、SAS/SATA等等;按照逻辑电平分类,包括:LVDS、CML、PECL 等等。

二、高速信号设计

当前的电子产品设计,需要更加关注高速信号的设计与实现,PCB设计是高速信号最终得以保证信号质量并实现系统功能的关键设计环节。

传统的电路板设计方式不关注PCB设计规则的前期仿真分析与制定,从原理图到PCB的设计实现没有高速信号规则约束,这样的传统设计方式在当前的高速信号产品研发体系中已经不可行,造成的后果一般是多次无效投板加工、不断测试优化与返工设计,造成研发周期变长、研发成本居高不下。

高速信号电路板设计流程:

(1)高速信号前仿真分析

根据硬件电路模块划分与结构初步布局,仿真评估关键高速信号质量是否过关,如果不过关则需要修改硬件模块架构甚至系统架构;仿真信号质量通过的情况下,给出电路板大体模块布局方案及高速信号拓扑结构与设计规则。

(2)电路板布局及布线设计

根据电路板实际布线的情况,如果与前仿真制定的设计规则有出入,则需要再次仿真分析高速信号质量是否满足要求,例如:电路板线路布线密度过高、实际设计的线宽比前仿真设计规则要小、可能造成高速信号线路损耗过大、接收端信号幅度不满足芯片输入要求而导致电路板功能无法实现。

三、电路板设计师需要掌握的高速信号知识

信号完整性基础知识和电源完整性基础知识可以查阅学习SI、PI理论书籍。PCB原材料料基础知识需要在设计实践中不断的积累,下面中间介绍信号拓扑结构知识:

(1)常见信号拓扑结构

①点对点拓扑 point-to-point scheduling

该拓扑结构简单,整个网络的阻抗特性容易控制,时序关系也容易控制,常见于高速双向传输信号线;常在源端加串行匹配电阻来防止源端的二次反射。

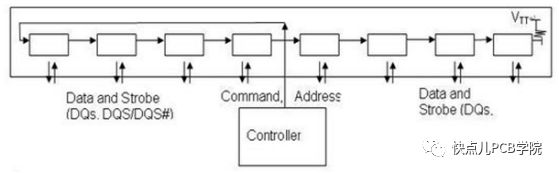

②菊花链结构 daisy-chain scheduling

如下图所示,菊花链结构也比较简单,阻抗也比较容易控制。菊花链的特征就是每个接收端最多只和2个另外的接收端/发送端项链,连接每个接收端的stub线需要较短。该结构的阻抗匹配常在终端做,用戴维南端接比较合适。

③fly-by scheduling

该结构是特殊的菊花链结构, stub线为0的菊花链。不同于DDR2的T型分 支拓扑结构,DDR3采用了fly-by拓扑结构,以更高的速度提供更好的信号完整性。

fly-by信号是命令、地址,控制和时钟信号。如下图所示,源于存储器控制器的这些信号以串行的方式连接到每个DRAM器件。通过减少分支的数量和分支的长度改进了信号完整性。然而,这引起了另一个问题,因为每一个存储器元件的延迟是不同的,取决于它处于时序的位置。通过按照DDR3规范的定义,采用读调整和写调整技术来补偿这种延迟的差异。

fly-by拓扑结构在电源开启时校正存储器系统。这就要求在DDR3控制器中有额外的信息,允许校准工作在启动时自动完成。

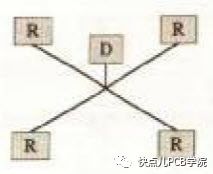

④星形结构 star scheduling

结构如下图所示,该结构布线比较复杂,阻抗不容易控制,但是由于星形堆成,所以时序比较容易控制。星形结构需要特别注意D点到适合于单项数据传输,从D-R,而不适合于从R-D。匹配方式一般在R端做匹配,消除终端反射。

⑤远端簇结构 far-end cluster scheduling

远端簇结构可以算是星形结构的变种,要求是D到中心点的长度要远远长于各个R到中心连接点的长度。各个R到中心连接点的距离要尽量等长,匹配电阻放置在D附近,常用语DDR的地址、数据线的拓扑结构。

四、高速信号处理方法

通用的高速信号PCB设计处理原则有:

(1)层面的选择:处理高速信号优先选择两边是GND的层面处理

(2)处理时要优先考虑高速信号的总长

(3)高速信号Via数量的限制:高速信号允许换一次层,换层时加GND VIA如图

(4)如果高速信号在连接器有一端信号没有与GND 相邻PIN时,设计时应加GND VIA 如下图:

(5)高速信号在连接器内的走线要求:在连接器内走线要中心出线。

(6)高速信号应设置不耦合长度及本对信号的长度误差,在做长度误差时须考虑是否要加PIN DELAY

(7)高速信号处理时尽量收发走在不同层,如果空间有限,需收发同层时,应加大收发信号的距离

(8)高速信号离12V 要有180 MIL的间距要求,距离时钟信号65mil间距

五、高速信号优化方法

以LVDS信号为例,说明高速信号的通常优化方法:

LVDS(Low Voltage Differential Signaling,低电压差分信号)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

LVDS信号不仅是差分信号,而且是高速数字信号。因此,对用来传输LVDS的PCB线对必须采取措施,以防止信号在媒质终端发生反射,同时应减少电磁干扰以保证信号的完整性。在PCB布线时需要注意的一些问题如下:

以上便是PCB设计软件allegro中的高速信号布线讲解.

-

谁有蓝牙音箱电路原理图和PCB讲解2022-11-14 10549

-

Altium18软件实操、Altium19预览及PCB设计学习思路方法详解2018-09-29 25646

-

以蓝牙音箱为案例的PCB设计布线综合知识详解2018-08-24 8828

-

PCB设计之以蓝牙音箱为例讲解静态铜箔和动态铜箔的设计2018-08-22 4970

-

PCB设计软件蓝牙音箱实操讲解2018-08-17 3996

-

PCB设计软件allegro蓝牙音箱案例实操讲解2018-08-15 4413

-

PCB布局及原理图交互式抓取2018-08-10 4426

-

PCB设计软件allegro操作中封装调入及常见错误2018-08-08 9659

-

PCB设计│网表导入的雷区,你还在踩?2018-08-06 2170

-

PCB设计软件蓝牙音箱实操│网表导出导入和封装路径设置2018-07-31 3392

-

以蓝牙音箱为案例的PCB设计软件实操2018-07-27 4507

-

PCB设计蓝牙音箱实操过程详解2018-07-24 3498

-

PCB设计:制作封装的详细步骤(蓝牙音箱实战案例)2018-07-14 4972

全部0条评论

快来发表一下你的评论吧 !