PCIe弹性缓存主要用于解决跨时钟域问题

电子说

描述

前面在介绍PCIe物理层逻辑子层的文章中,有提到过弹性缓存(Elastic Buffer,又称为CTC Buffer或者Synchronization Buffer)。其本质上是一种FIFO,主要用于解决跨时钟域问题。当然,PCIe的弹性缓存还用于补偿时钟误差(Compensate for the clock differences)。实际上,除了PCIe,弹性缓存还广泛应用于其它的高速串行接口——USB、InfiniBand、Fibre Channel、Gigabit Ethernet等基于SerDes的应用。

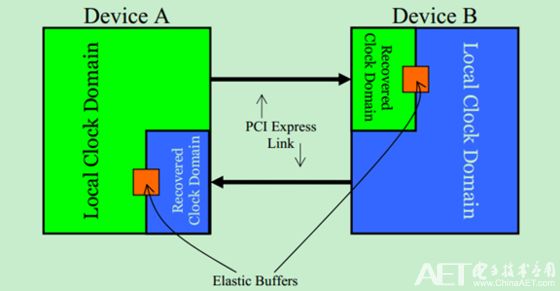

由于PCIe采用的基于8b/10b的嵌入式源同步时钟,接收端存在两个时钟域:一个是通过CDR从数据流中解析出来的时钟,用该时钟对数据进行采样;另一个是本地时钟域,用于其他的逻辑的。借助弹性缓存(FIFO),可以实现数据在这两个时钟域的转换。

以PCIe Gen1为例,链路上的数据速率为2.5Gbps。但实际上,任何晶振(或者其他频率发生器)都是有误差的,PCIe Spec允许的误差范围为±300ppm(Parts Per Million)。即,链路上实际的频率范围为2.49925GHz~2.50075GHz。借助弹性缓存,通过删除或者插入SKP Ordered Set可以消除链路频率误差的影响。如下图所示:

需要注意的是PCIe Spec并没有规定弹性缓存的具体位置,设计者可以将弹性缓存放在8b/10b解码器之前,也可以把弹性缓存放在8b/10b解码器之后。不过,Mindshare的建议是将弹性缓存放置于8b/10b解码器之前的。

当本地时钟域的时钟(Local Clock)的速度比数据流通过CDR解析出的时钟(Recovered Clock)的时钟要快时,且弹性缓存即将被读空之前,可以向SKP Ordered Set中插入1~2个SKP。如下图所示:

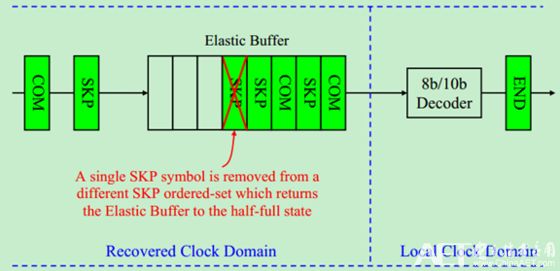

当本地时钟域的时钟(Local Clock)的速度比数据流通过CDR解析出的时钟(Recovered Clock)的时钟要慢时,且弹性缓存即将溢出之前,可以从SKP Ordered Set中移除1~2个SKP。如下图所示:

需要特别注意的是,Intel提出的PIPE规范(并非PCI-SIG强制的规范,具体参考前面关于PIPE的文章)中,只允许每次从一个SKP Ordered Set中插入或者移除一个SKP。如果需要插入或者移除两个SKP,则需要对两个SKP Ordered Set进行操作。如下图所示:

-

如何处理跨时钟域这些基础问题2024-01-08 1526

-

FPGA跨时钟域处理方法(一)2023-05-25 3223

-

跨时钟域电路设计总结2023-05-18 1596

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2688

-

调试FPGA跨时钟域信号的经验总结2022-11-15 1164

-

关于跨时钟域信号的处理方法2022-10-09 8598

-

SpinalHDL里用于跨时钟域处理的一些手段方法2022-07-11 3195

-

FPGA跨时钟域处理简介2022-02-23 1201

-

介绍3种方法跨时钟域处理方法2021-09-18 23628

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1730

-

关于跨时钟域的详细解答2021-04-27 5312

-

FPGA设计中解决跨时钟域的三大方案2020-11-21 5307

-

关于FPGA中跨时钟域的问题分析2019-08-19 4083

-

cdc路径方案帮您解决跨时钟域难题2017-11-30 8861

全部0条评论

快来发表一下你的评论吧 !