从低速Flash到高速Dram,输出电路有哪些不同?

电子说

描述

这篇文章聊一聊输入输出(IO)中的输出。大家都知道IO是芯片跟系统交互的直接路径,IO做的好与坏系统很容易就能检测出来。比如输出无法达到VOH/VOL、输出波形爬的太慢或者太快、输出的上升沿或下降沿不对称等等。输出特性的好坏更专业的是用如下的眼图来描述。

图中的阴影部分表示眼睛,眼睛睁开的越大,表示传输特性越好,有机会IC君会好好的研究一下眼图,先给自己留个作业。

1

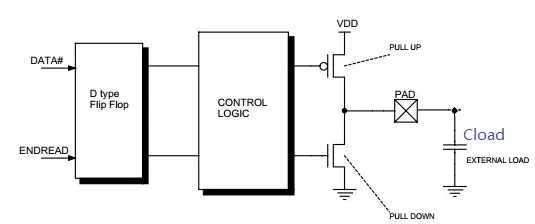

对于中低速的应用而言,比如Flash的数据输出速度大概是100MHz左右,基本的CMOS输出电路如下图所示:

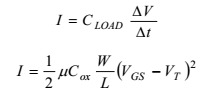

原理也很简单,输出“1”的时候,PMOS作为上拉管对Cload进行充电,从0到VOH;输出“0”的时候,NMOS作为下拉管对Cload进行放电,从VOH到0。根据MOS的充放电电流,假设MOS管一直工作在饱和区(实际平均电流是饱和区和线性区的平均),得到以下公式:

当电压达到VDD/2时所消耗的时间为:

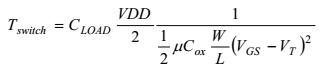

最终可以得到MOS管子的宽长比如下:

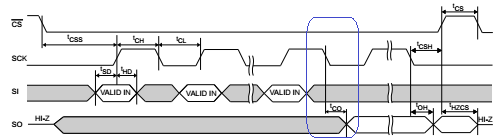

输出电路的最重要的设计spec通常如下图蓝色框图所示:

从CLK的某个沿到输出数据valid的时间 tCO 举个例子 Cload=30pF ,tCO=9ns。

根据这个spec以及上面的公式可以得到PMOS/NMOS的尺寸,再通过hspice来确认自己设计的正确性。当然实际设计要留更多的Margin来cover一些工艺的偏差,还要考虑信号线和电源线的routing,另外在设计中要注意尽量降低数据在切换时候的PMOS/NMOS同时导通的cross bar 电流。

在整个设计过程中,芯片输出在PCB板上驱动至下一个芯片的路径看成了一根理想导线,被驱动的芯片作为负载简化成了Cload。这样的假设在中低频的应用中(200Mhz以下)可能问题不大,而且VDD通常也是1.8V或者3V,幅度也比较宽。信号在整个传输过程中,不用特别考虑信号完整性的问题。

2

对于高速应用而言,比如DRAM的速度都是Ghz量级的,低功耗DRAM LPDDR4 的VDD电压幅度为1.1V,而且有越来越小的趋势。 DRAM的性能趋势可以参考下图:

高速应用下芯片输出在PCB板上驱动至下一个芯片的路径不能只当作导线,必须考虑信号完整性的问题。

信号完整性大致受到以下2个方面的影响:

传输线效应,比如反射;

与通道其他因素的交互,比如串扰和电源线的噪声。

信号完整性问题和很多因素相关,频率提高、上升时间减少、摆幅降低、互联通道不理想、供电环境恶劣、通道之间延时不一致等都可能导致信号完整性问题。但究其根源,主要是信号上升时间减小了。上升时间越小,信号中包含的高频成分就越多,高频分量和通道间的相互作用(反射、串扰、电源噪声等)就可能使得信号产生严重的畸变。

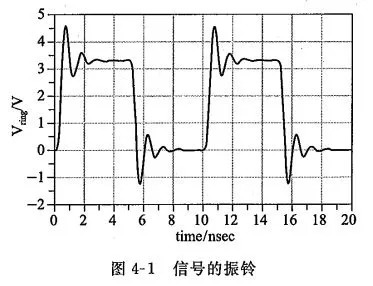

下图就是由反射引起的振铃现象:

信号在2个不同阻抗域传输的反射系数和传输系数:

反射系数为反射电压和输入电压的比值:

Xf =(Z2-Z1)/ (Z1+Z2)

传输系数是传输电压和输入电压的比值:

Xtran = 2*Z2 / (Z1+Z2)

反射的具体原理有兴趣可以找文章末尾的参考书籍阅读。

从反射系数的公式可以看到,要想消除反射的影响,必须阻抗匹配,也就是Z2=Z1。

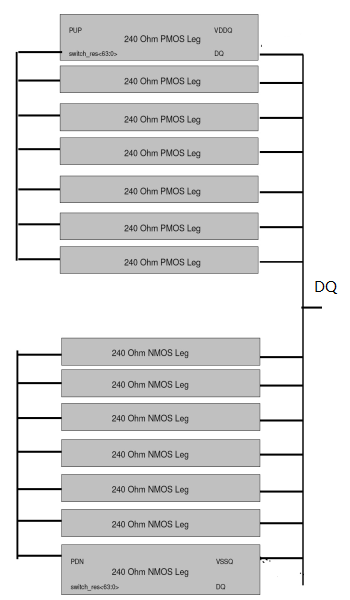

考虑到反射的消除以及输出上升下降时间的控制,输出电路的示意图如下:

上拉由7条240欧姆的PMOS分支构成,具体enable哪几条可以调整,在DRAM中可以通过模式寄存器控制。比如enable其中3条,那上拉电阻就是3条并联,最终电阻为80欧姆;下拉也是也是由7条240欧姆的NMOS分支构成,工作原理与上面类似。

有人肯定要问,这个电路就能做到精确的电阻匹配吗?

答案是不能。

因为我们的芯片在制造过程中会引入工艺的偏差,而且实际使用过程中温度电压也不一样,那怎么办呢?

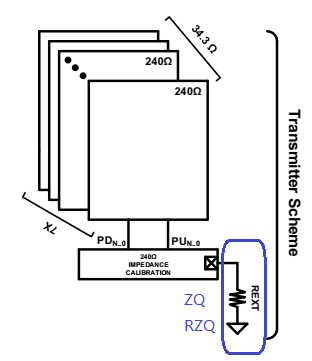

引入校准机制,校准之后就可以得到相对精确的阻抗。首先要引入一个精确外部电阻作为标准,不然后续的校准基础都是错误的。

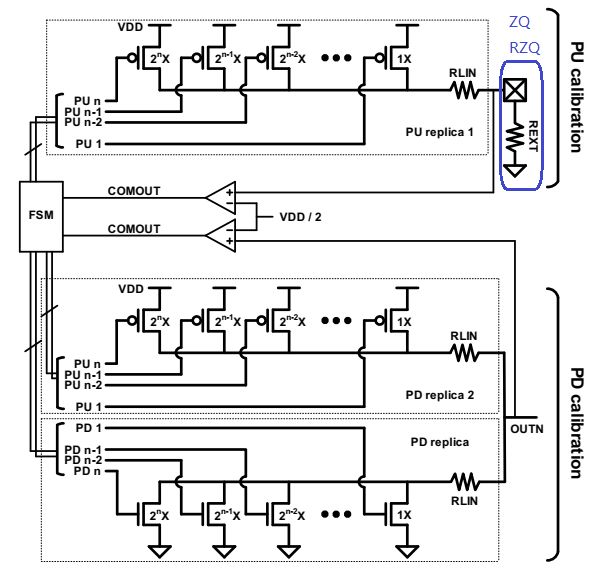

DRAM引入了ZQ pin, 这个pin 外接了一个精确的电阻240欧姆。DRAM在上电之后就会进行ZQ 校准,校准出系统需要的阻抗,传递给所有的输出pin。

电路示意图如下图所示:

每一个分支的具体电路示意图如下:

可以看出,每一个分支是由一堆并联的PMOS或者NMOS,再串联一个电阻RLIN得到。我们的目标就是将这个分支精确匹配到240欧姆。

从MOS管的IV特性得出MOS管的等效阻抗其实不是线性的,希望阻抗得到精确匹配,就不能完全用MOS来作为等效电阻。

串联电阻RLIN可以取一个比较大的值,比如100欧姆,那剩下的MOS就要匹配240-100=140欧姆的电阻。可以通过PU1 PU2 ... PUN来确定到底开多少个MOS管,然后用分压去跟VDD/2去作为比较,根据比较结果动态调整PU[5:1]的值。通常这里用的是逐次逼近SAR算法,这个算法也蛮有意思的,ADC中也经常会用到,IC君会在后续的文章中研究,又留一次作业。

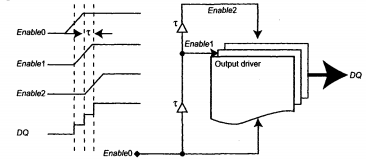

说完电阻匹配,再来聊一聊信号的上升下降沿的时间(斜率)控制。输出信号的斜率可以通过打开分支的时间来控制,示意图如下:

逐步打开分支,使得输出DQ信号的斜率相对缓慢的上去。

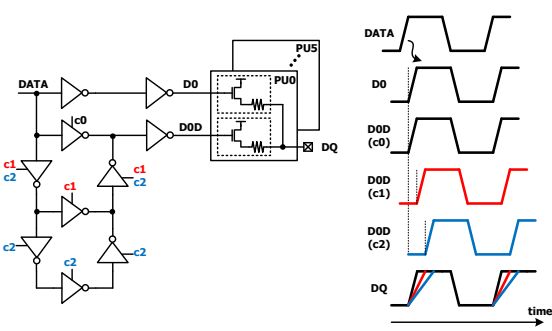

同时我们还可以在分支内部做精细的控制,示意图如下:

把MOS的gate控制信号进行延迟,可以通过C0、C1、C2这3条路径得到不同的D0D。D0D驱动的DQ与D0驱动的DQ叠加,调整最终DQ的斜率。

3

从低频到高频,对于CMOS类型的输出电路设计而言,基本的原理其实差不多。但是高频需要考虑信号完整性的问题,电路也因此变得更复杂。

-

EEPROM、EPROM、FLASH、SRAM、DRAM、SDRAM的区别.2012-12-20 32403

-

高速信号和低速信号有什么区别,怎么定义高速和低速呢2014-12-18 35330

-

如何区分电路设计中高速和低速2017-04-20 11739

-

浅析DRAM和Nand flash2019-09-18 5455

-

DRAM,SRAM,FLASH和新型NVRAM:有何区别?2020-09-25 4954

-

请问高速和低速的UART编码的区别是什么?2020-12-07 2285

-

ROM/RAM/DRAM/SRAM和FLASH的区别是什么2021-02-05 2646

-

stm32高速时钟与低速时钟2021-08-13 2489

-

高速低速测速器2009-01-10 1245

-

如何区分高速和低速板2016-07-26 4893

-

全球存储发展简史(DRAM、NAND Flash和Nor Flash)2018-03-31 24193

-

2019年6月DRAM与NAND Flash跌价趋势持续2019-07-06 4445

-

DRAM、SRAM和Flash原理解析2020-07-29 14891

-

如何区分高速和低速.zip2022-12-30 291

-

高速can和低速can区别2023-12-07 6575

全部0条评论

快来发表一下你的评论吧 !