模拟信号源阻抗对ADC的影响是什么

描述

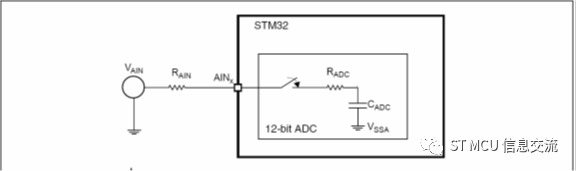

这里我们简单地把在信号源与ADC引脚之间的阻抗或者说两者之间的串行电阻(RAIN)称之为外部信号源电阻。在ADC转换部件内部,还有个开关电阻(RADC)和采样保持电容CADC。这个开关电阻可以理解为ADC转换过程中开关电路导通时的等效电阻,其大小一般就几K上下,视具体的芯片而定。

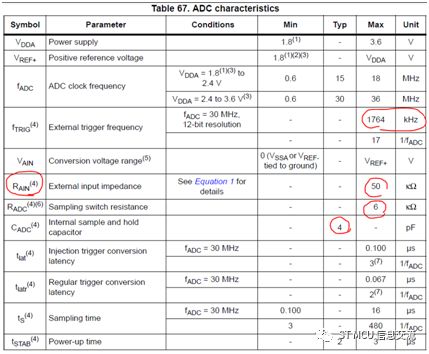

关于这个开关电阻和采用保持电容以及可允许的最大信号源电阻(RAIN)的取值范围,在STM32芯片的数据手册里都有明确介绍。比如我们可以从STM32F407的数据手册中ADC特性参数部分可以看多许多与ADC特性有关的数据。

从表格中可以到ADC能接受的最大外部触发频率,最大外部输入阻抗RAIN【50K欧姆】,以及内部ADC通道的采样保持电容的典型值【4pf】等。

在做AD转换时,信号源通过外部输入电阻和内部开关电阻【RADC + RAIN】对采样保持电容CADC进行充电,正常情况下,直到采样电容上的电压被充到与外部待测信号一致后再进行AD转换才合理。显然,对采样保持电容CADC的有效充电由外部电阻和内部开关电阻之和所控制,因为那采样保持电容是固定的。

其充电时间常数是tc =(RADC + RAIN) × CADC。

那么,如果内部采样时间【Ts】小于采样保持电容CADC通过RADC + RAIN 的有效充电的时间【tc】,则经过ADC转换得到的数值会小于实际数值, 这时就会产生AD误差。

这种情形下如何应对呢?

1、软件上调整内部采样时间。STM32 ADC的采样时间可以软件配置。调整范围从几个时钟多达几百个ADC时钟,这样便于尽量满足各类充电时间的实际需要。

2、硬件上调整外部信号源的电阻,通过调整信号源电阻而改变RC充电时间,进而与实现采样时间相匹配。

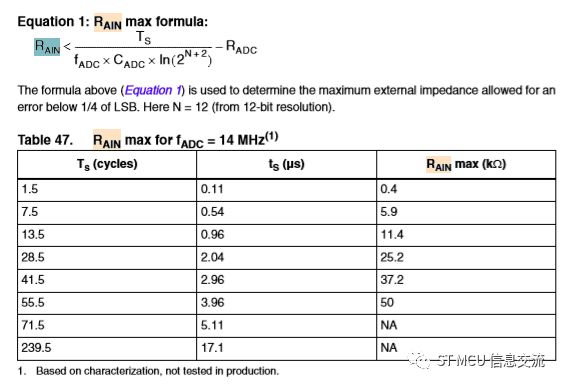

关于这个信号源电阻最大允许值,我们可以根据手册中给定的公式进行计算。不过,一般来讲无须用这个公式做多么精确的计算。倒是可以通过公式看出可允许的最大外部信号源电阻与哪些因素有关,它们之间有些什么样的数学关系,这样便于我们分析、估算和判断。何况,各stm32芯片的数据手册里往往都有基于不同采样时间下可接受的最大信号源电阻推荐值,可供我们参考使用。

整体上,较大的外部信号源输入电阻往往需要较长的采样时间与之相匹配。同时,它还跟ADC时钟、ADC转换的分辨率等有关。

总体上讲,在ADC应用中加大采样时间或减小信号源电阻对于提高ADC结果的精度是有利的。当然,在实际应用中我们往往需要结合具体情况,灵活地综合考虑。

因为加大采样时间,势必会导致转换速率的下降,有些对转换速率有要求时,加大采样时间可能就行不通。所以,除了加大采样时间的调整外,我们还可以考虑减小外部信号源电阻,但有些情况下一味减小信号源电阻又可能带来其它困扰,比如功耗方面的挑战。所以,我们在具体应用中可以依据不同的需求做调整、做取舍和平衡。

刚才提到,我们可以通过加大内部采样时间来与外部充电时间相匹配,但是,当外部信号源电阻超过一定限度时,由于STM32芯片内部采样时间的调整也是有限度的。当过了这个度后,加大采样时间也就无能为力了。

实际ADC应用中,有人在外部随随便便弄个几百K、甚至几兆的电阻在信号源与采样脚之间,因为这时候信号源电阻超过了芯片允许的范围,即使你再怎么加大采样时间也解决不了问题。

当然,我们还有种方法。使用运放做一个电压跟随器,这样可以减小信号源的阻抗效应。因为放大器具有很高的输入阻抗和非常低的输出阻抗,它把信号源电阻RAIN与内部开关电阻RADC隔离开来,这样就避开了因信号源电阻过大导致外部充电时间偏长,而内部采样时间又难以匹配的问题。

小结,我们在使用STM32芯片的ADC功能时,因为外部充电时间与内部采样时间不匹配,准确的说外部充电时间长于内部采样时间,导致采样电容没有被充分充电而产生ADC误差是非常常见的情形。

-

是德科技AP5000系列模拟信号源在接收机测试中的应用2025-05-16 697

-

ATG-3080功率信号源:信号源原理介绍2024-05-30 1349

-

信号源阻抗对探头负荷的净效应影响2024-01-08 1041

-

射频模拟信号源和矢量信号源的区别2022-08-23 5232

-

ADC误差的产生以及如何提高ADC的精度2021-07-09 11858

-

光谱宽覆盖遥感图像模拟信号源设计论文免费下载2021-03-10 981

-

E8257D PSG模拟信号源和E8267D PSG矢量信号源的使用手册免费下载2019-07-12 3106

-

光谱宽覆盖遥感图像模拟信号源设计2016-08-29 975

-

基于ICL8038模拟信号源的研制2011-07-16 2399

-

基于并口通讯的双路高速可编程数字及模拟信号源设计2009-12-08 1229

-

考虑信号源阻抗的差动放大电路图2009-07-08 969

-

基于FPGA的模拟信号源系统设计2009-05-26 648

全部0条评论

快来发表一下你的评论吧 !