基于FPGA实现的冲击信号处理芯片的功能、设计参数及应用分析

描述

引 言

冲击信号的测量数据是确定飞行器工作环境条件的重要依据。冲击信号的带宽一般为10 Hz 到5 kHz ,采样频率不低于20 kHz/ s ,编码一般应大于10 bit (冲击信号的动态范围较大)。冲击信号的测量是遥测系统的难题,它要求遥测系统具有很大的传输带宽。例如:传输一个测点X/ Y/ Z三个方向的冲击信号测量数据,大约需要600 kbit/ s 信道容量。冲击信号的巨大数据量给飞行器遥测系统的设计带来了压力。

由于压电加速度计具有体积小、安装方便等优点,飞行器遥测系统一般采用压电加速度计直接测量冲击波。但是,冲击波大都是复杂的振荡型脉冲,它本身不便于分析和比较。工程上研究冲击的目的,不是研究冲击波形本身而更注重于冲击作用于系统的效果,或者说冲击运动对系统的损伤势。因此,飞行试验中获取的遥测冲击数据,事后一般被处理成最大绝对冲击加速度响应谱,来分析飞行器在飞行中的冲击环境。

本文介绍的基于可编程门阵列( FPGA) 实现的冲击信号处理芯片,能在飞行器飞行过程中,实时完成对三路冲击信号的分析和处理,将冲击信号的处理结果代 替冲击波的原始测量数据传到地面,利用冲击信号的处理结果(主要是最大绝对冲击加速度响应谱和加速度计输出零位、最大值、最小值) 的数据量远少于冲击波测量数据的特点,减小冲击信号传输所要求的带宽,实现冲击信号的频带压缩。

最大绝对冲击加速度响应谱计算方法

式(1) 为用改进的递归数字滤波法求固有频率为f i 单自由度系统冲击加速度Xf i( k) 的数学模型。

式中: u ( k) ——冲击信号幅值,Δt ——冲击信号采样间隔,N ——冲击信号采样点数, f i ——单自由度系统固有频率,ζ——单自由度系统阻尼系数, Nf ——具有不同固有频率的单自由度系统数量, Xf i( k) ———固有频率f i 单自由度系统加速度,| Xf i( k) | max ———Xf i( k) 时间轴上的最大绝对值。| Xf i( k) | max作为单自由度系统固有频率f i 的函数即为最大绝对冲击加速度响应谱。

芯片主要功能及设计参数

芯片主要功能

考虑到实际应用中一般测量X/ Y/ Z 三个方向的冲击加速度,为了减小产品体积,冲击信号处理芯片采用SoC 设计思想,将三路冲击信号的处理、数据存储及输入输出管理集成在一个芯片上;同时,为了简化产品电路设计,冲击信号处理芯片还提供所有与之相连外围电路的控制信号。为了减小误差积累,冲击信号处理芯片对冲击信号实现分段处理并总是保存当前测试时间段最大绝对冲击加速度响应谱,遥测系统可以根据系统容量和实时性要求,随机读取当前处理时间段的最大绝对冲击加速度响应谱,调整冲击数据压缩比。

冲击信号处理芯片的主要功能如下:

(1) 定时或外部触发方式实现冲击信号分段;

(2) 分段计算三路冲击信号最大绝对冲击加速度响应谱;

(3) 分段计算冲击信号零位;

(4) 实时捕获冲击信号最大值和最小值;

(5) 记录冲击信号最大值和最小值发生时刻;

(6) 提供A/ D 变换器、串行通信接口或并行通信接口控制信号。

芯片设计参数

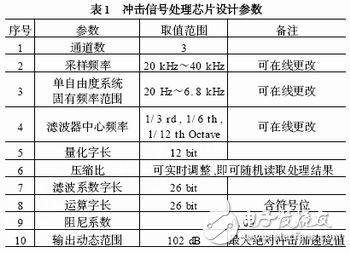

冲击信号处理芯片设计之前,有多个设计参数需要确定,如:采样频率、滤波系数字长、冲击响应谱运算字长、单自由度系统固有频率的取值范围等等。这些参数既互相关联、又互相制约,它们直接影响冲击信号处理芯片的综合性能。表1 为结合飞行器遥测系统容量、FPGA 硬件资源、处理器功耗,从减小冲击响应谱处理误差和确保滤波器稳定工作的角度,综合权衡多种因素后,确定的冲击信号处理芯片的设计参数。

芯片设计

芯片系统设计

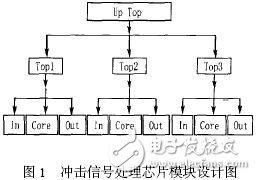

冲击信号处理芯片采用自顶向下( Top-Down) 的层次化结构设计方法。系统由三个独立的子系统组成( Top1 、Top2 、Top3) ,每个子系统又由三个完成不同功能的模块组成( In ,Core ,Out) 。图1 为冲击信号处理芯片模块设计。

从结构上看,冲击信号处理芯片采用模块化设计,共设计五个模块,它们的名称和功能分别为:

(1) Up- Top 模块 系统复位、输入输出数据管理、起飞信号“真”“伪”判断及自锁、定时(或外触发) 方式信号分段。

(2) Top 模块 完成一路冲击信号处理。

(3) In 模块 完成输入数据预处理、提供A/ D 控制信号、产生Core 模块流水运算控制信号、计算输入信号零位、捕获输入信号最大和最小值。

(4) Core 模块 计算最大绝对冲击加速度响应谱。

(5) Out 模块 产生特征码、单通道输出数据管理。

上述五个模块可以通过不同的组合,完成从一路到多路冲击信号的处理。

芯片存储器设计

合理的数据存储结构不仅有利于充分利用硬件资源,也为优化计算流程和提高处理速度创造条件。图2 为改进的递归数字滤波法信号流程图(直接型) ,它清楚地描述算法的步骤及实现该算法需要存储的参数。

由于计算结果为最大绝对冲击加速度响应谱,除图2 所示的参数外,还需要存储Xf i ( k) 的最大绝对值| Xf i( k) | max。

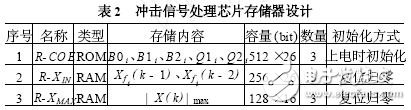

式(1) 中滤波系数B0i 、B1i 、B2i 、Q1i 、Q2i 是决定滤波器性能的基本参数,采用独立的ROM存储,每次FPGA 芯片加电时ROM初始化。Xf i( k - 1) 、Xf i( k - 2) 、| Xf i( k) | max如果共用一个存储器,控制电路设计简单,但Xf i( k - 1) 和Xf i( k - 2) 动态范围远远大于| Xf i( k) | max ,与| Xf i( k) | max存储在同一存储器中会造成存储资源 浪费,因此,设计了两个RAM将它们分开存储。表2 是根据表1 所示参数设计的存储器,该方案既保证了存储资源的有效利用,控制电路也相对简单。

Core 模块设计

Core 模块主要完成最大绝对冲击加速度响应谱计算。按表1 所示的设计参数,当滤波器中心频率为1/ 12 th 倍频程(Octave) 时,每采样一个u ( k) ,Core 模块需要按式(1) 计算出Nf = 102 个单自由度系统最大绝对加速度。

Core 模块采用流水运算计算Nf 个单自由度系统的最大绝对加速度。每一个单自由度系统最大绝对加速度的计算分(1) 、(2) 两拍流水完成, (1) 、(2) 两拍流水又各有自已独立的5 个节拍。设计了一个25 位乘法器和一个50 位累加器,用5 个芯片工作时钟周期,完成一个单自由度系统最大绝对冲击加速度的计算。下面以计算固有频率为f i 的单自由度系统最大绝对加速度为例,介绍Core 模块工作原理。

(1) 分5 步完成5 次乘及4 次累加操作,流程如下:

步骤1 u( k) 与B0i 相乘,累加器初始值为u( k) ×B0i ;

步骤2 u ( k - 1) 与B1 i 相乘,累加器累加步骤2 计算结果;

步骤3 u ( k - 2) 与B2 i 相乘,累加器累加步骤3 计算结果;

步骤4 Xf i( k - 1) 与Q1 i 相乘,累加器累加步骤4 计算结果;

步骤5 Xf i( k - 2) 与Q2 i 相乘,累加器累加步骤5 计算结果;

(2) 分5 步完成数据的准备和后处理,流程如下:

步骤1 读出f i - 1的Xf i( k - 1) ;

步骤2 f i - 1的Xf i( k - 1) 写入寄存器、科学计数法转换及数据截取、f i - 1的Xf i - 1 ( k) 写入f i - 1的Xf i - 1( k - 1) 位置、计算Xf i( k) 的绝对值| Xf i( k) | 并锁存结果;

步骤3 将f i - 1的Xf i - 1( k - 1) 写入Xf i - 1( k - 2) 位置、从R- XMA X中读取f i 的| Xf i( k) | max ;

步骤4 比较| Xf i( k) | 与| Xf i( k) | max大小,将大数写回R- XMAX ;

步骤5 从R- XMAX读取下一个要输出的最大绝对冲击加速度值,写入输出缓冲器。

流水运算保证5 个时钟周期计算一个单自由度系统的最大绝对响应加速度。设冲击信号处理芯片内部工作时钟频率为f m ,则计算Nf 个单自由度系统最大绝对响应加速度的时间Ts 为

Ts = (5 ×Nf ) / f m (2)

设冲击信号的采样频率为f s ,由式(2) 可得f s 与f m 的关系为

f s = f m/ (5 ×Nf ) (3)

由式(3) 可见,改变芯片的内部工作时钟频率即可改变冲击信号的采样频率。

遥测系统可通过冲击信号处理芯片的采样频率设置端口,在线控制冲击信号处理芯片内部的时钟分频器,设置冲击信号的采用频率,满足不同冲击信号处理器对峰值检测误差的要求和处理器功耗的限制。

芯片仿真结果分析

冲击信号处理芯片基于FPGA 实现,并按文献规定的最大绝对冲击加速度响应谱验证要求,对冲击信号处理芯片进行了各级设计仿真。

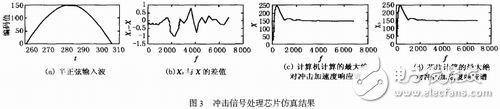

图3 为冲击信号处理芯片仿真结果之一。

图3 中f 为单自由度系统的固有频率。图3 (a) 为峰值150 (8 位编码) ,持续时间0. 125 s ,以512 Hz/ s 采样的64 点半正弦输入波。图3 (c) 为计算机计算的最大绝对冲击加速度响应谱, X 为最大绝对加速度。图3 (d) 为本文设计的冲击信号处理芯片计算的最大绝对冲击加速度响应谱, Xs 为最大绝对加速度。图3 (b) 是Xs 与X 的差值。仿真结果符合文献对最大绝对冲击加速度响应谱的验证要求。

试验结果及分析

基于冲击信号处理芯片设计的数据预处理器已在各种试验中应用。为了验证数据预处理器的性能,进行了如下对比试验。

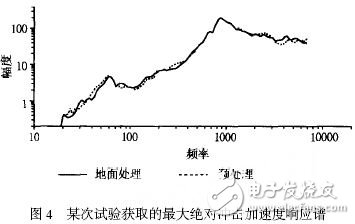

采用遥测系统速变通道和数据预处理器,同时获取冲击环境信息。具体试验方法为:遥测速变通 道和数据预处理器,同时接收同一加速度计的输出信号,前者完成加速度计输出电压信号编码并将编码结果通过无线信道传输,后者完成对加速度计输出电压信号的编码、处理和分析,并将处理结果代替原始测量数据通过无线信道传输,将二者的测量结果进行比较。图4 为某次试验获取的最大绝对冲击加速度响应谱。

图4 中实线为地面对遥测速变通道记录数据的处理结果, 虚线为数据预处理器输出结果。试验结果表明,除了有效压缩冲击信号传输带宽外,采用冲击信号预处理技术还具有如下优点:

(1) 更容易识别数据“真”“伪”。冲击加速度响应谱为缓慢变化的曲线,原始冲击信号属于宽带随机信号,从缓变信号中能更准确地剔除信道误码成份。

(2) 提高冲击信号的测量精度。采用数据预处理后,冲击信号的采样频率和编码位数不再受遥测系统容量限制,通过提高冲击信号的采样频率和编码位数可提高冲击信号动态测量范围,减小冲击信号峰值检测误差。

(3) 提高冲击信号测量值(奇异值) 的时间分辨率,为飞行故障分析创造更好的条件。

结 论

本文采用SoC 设计思想,基于FPGA 完成了三通道冲击信号处理芯片的设计。飞行试验表明,该芯片能实时完成三路冲击信号处理并将处理结果代替冲击波原始测量数据输出,能在大幅度压缩冲击信号传输带宽的同时,减小冲击信号峰值监测误差,扩大冲击信号测量动态范围,并为事后识别数据“真”“伪”创造了好的条件。

责任编辑:gt

-

数字信号处理的FPGA实现.第3版英文2021-10-18 1098

-

怎么实现基于FPGA的三通道冲击信号处理芯片的设计?2021-05-26 1041

-

基于FPGA和双GA3816处理器实现数字通用信号处理系统的设计2021-05-22 3003

-

利用FPGA怎么实现数字信号处理?2019-10-17 6394

-

一种基于实用AGC算法的音频信号处理方法与FPGA实现的分析研究2018-09-30 3626

-

多抽样率的数字信号处理及其FPGA实现2017-10-30 974

-

FPGA信号处理算法设计、实现以及优化(南京)2016-12-26 857

-

基于FPGA的数字信号处理算法研究与高效实现2016-08-29 850

-

基于FPGA的FFT信号处理器的设计与实现2016-03-21 987

-

数字信号处理的FPGA实现2015-12-23 1058

-

基于FPGA的心电信号处理研究与实现2015-10-30 673

-

基于FPGA的数字收发机信号处理研究与实现2011-11-01 600

-

基于FPGA的超声波信号处理设计与实现2010-09-30 647

全部0条评论

快来发表一下你的评论吧 !