DRM测试接收机信号处理流程及硬件平台的设计

描述

随着生活水平的不断提高.人们对音频广播的质量提出了更高的要求。但在传统的中短波频段广播中.由于中短波信道变化复杂、受干扰严重,且采用模拟幅度调制(AM),致使目前中短波广播的质量远远低于人们的收听要求。数字技术的迅速发展,为提高中短波广播质量提供了一种全新酌途径,音频广播从模拟到数字的过渡成为必然。

正是在上述背景下,DRM(Digital Radio Mondiale)系统应运而生。DRM系统采用OFDM调制方式,引入了先进的信源信道编码和调制技术,使得AM波段的音频广播质量大大提高,在保持现有10kHz带宽时接近了FM广播的质量。

本文首先简单介绍DRM系统,然后重点讨论DRM测试接收机的设计背景、信号处理流程及硬件平台的结构。

1 DRM系统介绍

1.1 系统概述

DRM系统采用OFDM调制方式,具有多种传输模式,适用于多种信道和带宽的传输方式,可以传送音频流及数据流。DRM标准同时提供了数模同播的广播方案,可以将模拟与数字信号同时以同一载波频率播出,有利于模拟广播向数字广播的平滑过渡。

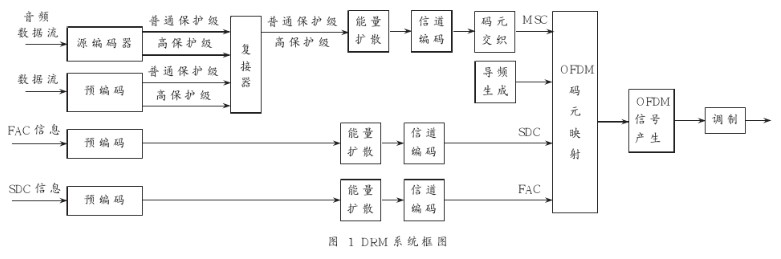

DRM系统框图如图l所示,主要由三个逻辑通道组成:主业务通道(MSC)、业务描述通道(SDC)和快速访问通道(FAC)。

FAC通道提供信号带宽、调制方式和交织长度等信息;SDC通道提供如何解调MSC、如何找到相同数据的其他数据源,以及在复接器中为业务提供属性等信息;MSC通道包含音频或数据业务,通过复接器对不同保护级别的数据和音频业务进行复接,MSC最多可以包括四路业务,任何一路都可以是音频或数据。

1.2 信源信道编码

DRM的信源编码采用先进的AACPlus等编码技术,有效地提高了信源的压缩比。

信道编码采用基于卷积编码的多级编码(MLC,Multi-Level Coding),可以分为标准映射(SM)、对称分级映射(HMsym)和混合分级映射(HMmix)三种QAM映射类型。通过交织克服时间和频率选择性衰落,根据信道特性可以选择2s的长交织或者0.4s的短交织。

1.3 导频

DRM在所传输的OFDM码元中插入了三种导频信息,可用于接收机同步、均衡处理。其中频率导频主要用于接收机频偏的估计;时间导频用于接收机帧同步的计算;增益导频用于接收机信道估计。

2 DRM测试接收机设计背景

我国已经在部分地区进行了DRM系统的现场测试,测试效果令人满意,这给DRM系统的应用奠定了基础。

目前,国内外采用的DRM接收机大多是基于PC的DRM软件接收机,已经比较成熟,但其应用范围终究受到一定限制。适于广泛应用的便携式硬件DRM接收机目前还处于研制阶段,尚未批量生产。而DRM系统只有在专用ASIC推出后才可以迅速降低接收机的成本,才能有利于DRM系统的推广。

基于上述考虑,asic,设计了DRM硬件测试接收机。一方面是对硬件实现DRM接收机的一种探讨,另一方面可以以此为原型机,进一步为设计拥有自主知识产权的DRM接收机ASIC积累经验。为此,笔者将设计目标确定为:可以验证DRM接收系统的各种算法,可以对相同模块的不同算法进行比较,可以对算法的硬件可行性、稳定性及复杂度进行评估。考虑到全数字接收机代替现有模拟接收机需要一个长期的过程,设计中同时考虑了数模同播的兼容性问题。

3 DRM测试接收机信号处理流程

根据数模同插的要求,在设计DRM接收机RF前端时采用了改造现有模拟收音机的方法。整合后的接收机既可以收听模拟信号,又可以完成数字信号的处理,这样就可以适应数模同播的需要。下文主要讨论数字接收机的信号处理过程。

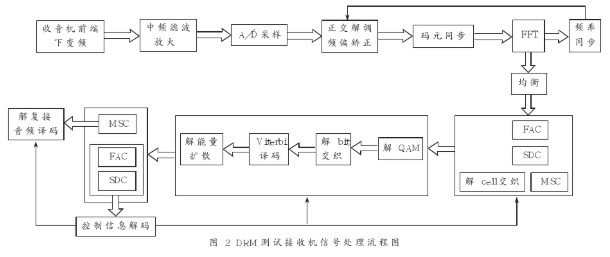

测试接收机系统框图如图2所示。接收信号通过模拟收音机前端下变频到中频,将中频信号引出,经过滤波送入AD采样,从而获得中频采样数据。

中频采样数据通过正交解调得到基带数据。首先通过码元同步找到OFDM码元的起始位置,然后通过FFT完成OFDM信号的解调,将时域数据变换到频域,并利用频率导频信息计算并校正频率偏差,因为OFDM系统对载波频偏非常敏感,经过频率校正后,频率误差应小于0.01倍子载波间隔。在此基础上,利用时间导频信息找到DRM系统的传输帧起始码元,此后接收机从传输帧起始位置开始进行后续处理。

由于短波信道变化复杂,时域及频域的选择性衰落都很强,造成丁接收信号的幅度和相位受到严重干扰,在解高阶QAM映射时会引入较大的误差,框图中的均衡模块用来解决上述问题。DRM系统设计了增益导频,分布在时间一频率域上,利用增益导频的信息进行信道均衡。

按图2所示流程,从均衡后的数据中提取FAC单元并将其解码,得到解调SDC的信息;再提取SDC单元,根据FAC的信息解码SDC,得到SDC数据实体;最后提取MSC,根据FACSDC的信息解码MSC。上述单元分别经过解交织、解OAM映射、Viterbi译码、能量解扰等模块的处理后,最后将MSC解复接后的数据进行音频译码或者数据解码。

4 DRM测试接收机硬件结构

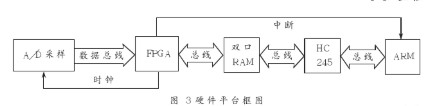

测试接收机基带信号处理部分主要采用ARM与FPGA联合处理的硬件平台实现。ARM处理器可以在不改变硬件结构的情况下,通过下载不同的软件程序实现不同的功能,这样非常有利于不同算法的验证,而且ARM公司可以提供处理器内核,为进一步设计接收机ASIC奠定基础。由于ARM以half-word(16 bits)为最小处理单位,所以用ARM处理器处理比特流信号会造成处理器资源的浪费,为此针对比特流信号的处理采用专用逻辑电路实现,在测试接收机中用FPGA实现。这样,两种处理器的特性可以形成互补,使硬件平台设计比较合理。

4.1 模块划分

DRM系统设计了多种模式,不同模式的码率是不同的,在正交解调后需要变码率输出;Viterbi译码器也是以比特流为处理单位;考虑到这两个模块的算法特点及数据输出形式,将这两个模块放在FPGA中实现。

图2中所示的其他处理模块,特别是同步和均衡模块是接收机的关键模块,其性能好坏直接影响接收效果,并且根据今后现场测试的情况,其算法存在调整的可能性.因此这些模块通过ARM实现。需要对算法进行调整时,只需修改软件程序,重新载入ARM即可,硬件部分无需改动。以实现测试接收机便于对各种算法的性能进行验证和比较的目的。

4.2 硬件平台结构

测试接收机硬件平台如图3所示。FPGA采用XILINX公司的VirtexⅡXC2V500型芯片;ARM采用三星公司的S3C4510B型ARM7 TDMI芯片;ADC模块采用了AD公司14-bit的AD9243。FPGA与ARM之间通过双口RAM进行数据交互,使用HC245芯片作为地址和数据总线的驱动。

A/D采样后的中频数据送入FPGA做正交解调;FPGA将解调后的数据写入双口RAM同时给ARM产生中断信号;ARM响应外部中断,将数据读入、进行后续处理。

如图2中的流程,ARM在处理完解交织后,将处理后的数据写入双口RAM,同时向特定的地址写控制字,FPGA检测到控制字后,将数据读入.进行Viterbi译码。FPGA将Viterbi译码结果写入双口RAM,向ARM发出中断信号,ARM响应中断,将数据读入,再进行后续处理。

4.3 主控制程序流程圈

根据图2所示的DRM信号处理时序,图4为ARM基带处理主控制程序流程图,依次进行码元同步、整数倍频偏估计、帧同步及后续信道解码处理。上述过程实现了DRM接收机基带信道解码过程。

4.4 测试结果

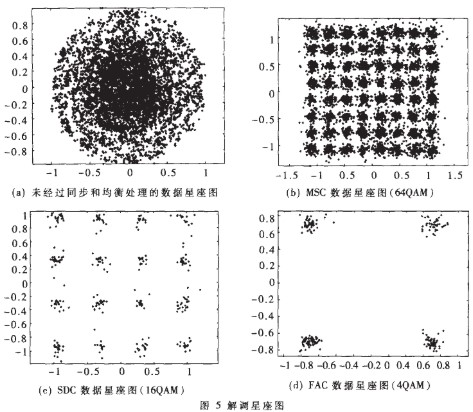

测试信号采用模式C、10kHz带宽的DRM信号,信道采用标准中提供的2号信道模型,SNR=23dB,频偏为2倍子载波间隔。

测试结果示于图5中,其中图5(a)为未经过同步和均衡处理的数据星座图;图5(b)“(d)为接收信号通过硬件正交解调、同步、均衡、信道解码等模块后输出数据的星座图。从图5中可以看出,经过同步、均衡处理后,星座图明显改善,处理器有效地解出了三个通道的数据。

数字广播产业有广泛的市场前景,而拥有自主知识产权的接收机对民族工业具有特殊意义。本文讨论的DRM测试接收机信号处理流程及硬件平台的结构是对硬件实现DRM接收机的一次有益尝试。上述结构、算法已经在ARM7和FPGA的硬件平台上联调通过,验证了本文提出的信号处理流程及硬件平台的可实现性,但所验证的主要是基带信号处理功能,还没有包括接收机的全部.整个测试接收机的设计工作仍然需要进一步完善。

责任编辑:gt

-

测试接收机的技术原理和应用场景2024-12-03 5213

-

怎么实现DRM测试接收机设计?2021-05-26 1597

-

基于PCI和LVDS的接收机测试源设计2010-01-20 670

-

基于独立DSP 平台的实时卫星导航接收机的设计实现2010-04-07 767

-

一种DRM数字广播接收机的同步算法2010-06-22 918

-

通信接收机测试、信号处理仿真系统2010-12-11 471

-

短波再生式AM和DRM接收机电路2009-12-03 3900

-

基于FPGA和DSP的卫星导航接收机测试平台2010-02-09 1960

-

各种干扰下接收机如何进行灵敏度测试2015-05-28 1879

-

全球定位系统信号接收机射频模块设计2017-12-07 864

-

EMI接收机与频谱仪的区别在哪里?EMI测试要选用接收机的目的2018-05-29 12359

-

EMI测试接收机的抗干扰设计2019-12-10 2837

-

频谱分析仪和EMI测试接收机之间有什么区别呢2022-11-25 2675

-

中频接收机硬件平台的设计方案2023-10-27 538

-

接收机的三大故障分析2024-02-05 2426

全部0条评论

快来发表一下你的评论吧 !