基于EP1C6芯片和DSP Builder工具实现行车道边缘检测系统的设计

描述

通过对摄像头读入的道路白线图像进行灰度变换,再检测出白线的边缘,这是实现智能车自动导航和辅助导航的基础。行车道检测系统可以应用于智能车的防撞预警和控制。该系统设计重点是边缘检测电路的设计。边缘检测电路包括图像输入缓冲电路、垂直方向的边缘检测电路、水平方向的边缘检测电路及对两部分检测的组合,最终通过阈值选择形成二值边缘图像。传统的方案大多采用单片机电路实现,设计流程和系统调试都比较繁琐,开发周期长。在实时图像处理中,由于处理速度要求较高,因此用以前的方法很难达到要求。实时图像处理常常需要对图像进行求和、卷积、边缘提取、图像分割及特征提取等不同种类、不同层次的处理。对于一些运算结构简单,但要处理大量数据的算法一般采用FPGA芯片来实现。通过FPGA实现信号处理可以取得出色的系统稳定性,提高控制精度,还可以大大减少开发周期,使设计人员的设计自由度加大。本文采用Altera公司的Cyclone EP1C6作为主控芯片,利用Altera公司推出的数字信号处理开发工具DSP Builder作为设计平台,通过DSP Builder SignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真,从而完成对整个道路边缘检测系统的设计。

1、系统构成及边缘检测原理

本系统中的主要模块是进行二维卷积操作的sobel边缘检测模块,它相当于硬件的协处理器。该系统从CF卡读入数据到边缘检测模块,使用Nios II控制数据流,采用DMA控制器在外部存储器(SDRAM和SRAM)之间传递数据,这些外部存储器相当于中间图像数据缓冲器。系统结构如图1所示。

边缘是指图像中像素灰度有阶跃变化或屋顶状变化的那些像素的集合。它对图像识别和分析十分有用,边缘能勾划出目标物体轮廓,使观察者一目了然。边缘包含了丰富的信息(如方向、阶跃性质 、形状等),是图像识别中抽取的重要属性。微分运算有加强高频分量的作用,从而使图像轮廓更清晰。对于数字图像,微分可用差分近似代替,沿x和y方向的一阶差分可分别表示如下:

一阶差分增强是有方向性的。为了增强图像中间任何方向伸展的边缘和轮廓,希望对图像的某种导数运算是各向同性的,而梯度运算恰具有各向同性特性。对于图像f(x,y)点上的梯度可定义为矢量:

梯度幅度具有各向同性或旋转不变性,而且给出了该像素点灰度的最大变化率。采用微分锐化图像,会使噪声、条纹等得到增强,这在图像处理中会造成伪边缘和伪轮廓,为此对锐化算子进行了各种改进。Sobel算子就是其中一例,它在一定程度上克服了上述问题。Sobel算子的基本思想是:以待增强图像的任意像素(i,j)为中心,截取一个3×3的像素窗口。分别计算窗口中心像素在x和y方向上的梯度。Sobel算子的表达式如下:

Sx=

增强后图像在(i,j)处的灰度值为:

2、基于FPGA的DSP Builder设计流程

Altera DSP Builder将The MathWorks MATLAB和Simulink系统级设计工具的算法开发、仿真和验证功能与VHDL综合、仿真和Altera开发工具整合在一起,实现了这些工具的集成。设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件,通过DSP Builder SignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。

此系统设计首先用MATLAB建立DSP电路模型。电路模型设计完成后,就开始进行系统功能的仿真,这是属于系统级并且基于算法的仿真,与目标器件无关。然后利用置于Simulink电路模型界面的DSP Builder中的Signal Complier将电路模型文件即Simulink模型文件(.mdl)转化为RTL级的VHDL代码表述和Tcl脚本。一旦获得了VHDL描述,就可以在Simulink中调用Quartus II中的综合器生成网表文件。下一步就是调用Quartus II中的编译器,根据网表文件及设置的优化条件进行布线布局和优化设计的适配操作,同时生成用于Moldelsim的时序仿真文件。将最后生成的Programmer Object File(.pof)对目标器件进行编程配置,即可在硬件上形成DSP系统。

3 、边缘检测系统的Simulink模型设计

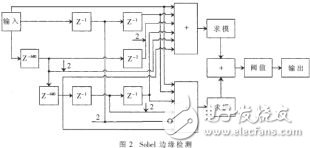

Sobel边缘检测模块包括独立且并行的水平检测和垂直检测两部分。输入缓冲通过一组延时线路转换输入的像素值。线路缓冲器的缓冲级数由图像的宽度决定。本设计采用的图像宽度是640。缓冲器的个数取决于卷积核的大小,本设计采用3×3的Sobel卷积核。垂直和水平方向的边缘检测几乎是相同的,两者之间的区别只在于从输入缓冲器流过的数据流。最后将两部分组合并通过阈值选择形成一幅经过边缘检测的二值图像。Sobel边缘检测是流水线操作,在每一个时钟周期都计算得到一个像素值,如图2所示。图中,Z-640是指本设计输入的图像像素宽度是640,右上角的加法模块实现的是垂直方向的边缘检测,右下角的加法模块实现的是水平方向的边缘检测。对于一般的灰度图像, 其像素的灰度值一般用8位表示,考虑到计算过程中可能出现负数和溢出问题。因此,数据在开始计算前先在最高位补零,使数据宽度变为10 位,计算完成后可再裁剪为8 位。

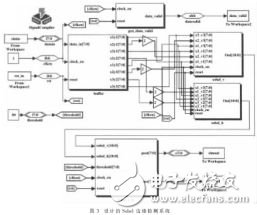

在DSP Builder中设计的Sobel边缘检测系统如图3所示。

4 、仿真结果

建立了.mdl文件之后,在Simulink中对其进行系统算法级仿真。设置Matlab各项参数和Simulink仿真参数,因为本设计采用图片的像素是640×480,所以设置仿真时间为307 201s(所有的像素数量加1)。

测试表明,仿真结果符合要求,整个系统算法级设计是正确的。图4为原始的彩色图像,图5为经过水平边缘检测和垂直边缘检测后没有经过阈值选取的图像,图6为经过阈值选取后的二值图像。Sobel算子不像普通梯度算子那样用两个像素的差值,而是采用两列或两行像素灰度加权和的差值来表示,因此有以下两个优点。

(1)由于引入了平均因素,因而对图像中的随机噪声有一定的平滑作用。

(2)由于它是相隔两行或两列之差分,故边缘两侧的元素得到了增强,边缘显得粗而亮。

使用Modelsim进行功能仿真,主要是调用.tcl 文件对RTL 级的VHDL 代码仿真。由于Simulink 的仿真是算法级的,而此仿真是针对硬件结构的,两者之间可能存在软件理解上的差异,所以对RTL 级VHDL 代码的仿真是必要的。仿真结果和系统级仿真一致。编译生成.pof 文件,下载到目标芯片中,从而完成整个边缘检测模块的设计。

-

基于EP1C6Q240C8的FPGA芯片实现电子测试系统的设计2020-08-04 2438

-

基于FPGA的实时边缘检测系统设计,Sobel图像边缘检测,FPGA图像处理2024-05-24 3427

-

请问,如何进行DSP编程(C语言)实现图像滤波处理,及边缘检测??2014-09-28 4245

-

基于FPGA的视频实时边缘检测系统该怎么设计?2019-09-24 2233

-

转辙机缺口检测怎么实现上传功能?2020-03-30 1875

-

基于DSP Builder的小波变换设计实现2021-05-13 7164

-

基于CY7C68013的USB数据采集系统2009-09-14 851

-

基于DSP Builder的Chirp信号源设计2009-10-04 1563

-

DSP Builder设计深入2011-02-28 636

-

基于DSP Builder的混沌保密通信研究2011-09-01 947

-

EP2C5T144开发板原理图2011-12-06 6299

-

基于Matlab/DSP Builder的系统实现2017-10-30 1068

-

基于DSP Builder的行车道检测设计实现2017-11-03 994

-

如何使用动态曲线进行车道检测算法的资料概述.2018-12-18 1760

-

空中自行车道三维建模钢结构测量2020-04-21 1518

全部0条评论

快来发表一下你的评论吧 !