利用PLB总线和FPGA技术对H.264整数变换量化软核实现优化设计

描述

H.264以其高复杂度为代价获得了优异的编码效率, 其中除部分控制流程的复杂模块外,H.264中的很多模块适合用硬件实现。应用中通常使用CPU+FPGA结构,将耗时较多的模块用FPGA实现,CPU仅负责一些低复杂度的算法和编码流程参数的设置。

介绍了整数变换量化的硬件实现,但没有考虑数据在处理过程中的宽度问题,因此会造成FPGA资源的浪费。本文充分考虑了数据在处理过程中的动态范围,使用更少的FPGA资源来实现H.264中的整数变换量化模块。

结合实际应用,文中对该软核在计算速度和硬件资源方面分别做了优化。经过速度优化的软核性能明显优于设计,经过消耗资源优化的软核也完全能够胜任高分辨率的实时编码。

1 整数变换

在完成帧内和帧间预测以后,需要对图像参差数据进行整数变换和量化,使图像数据的能量集中到一小部分系数上,进一步降低码流速率。

1.1 整数变换原理

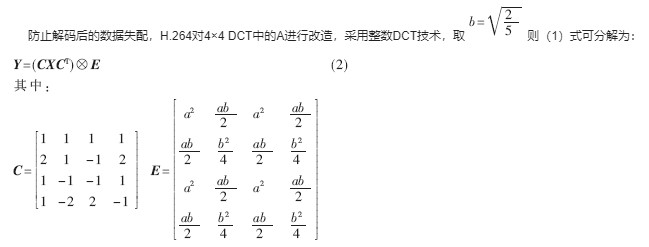

H.264中对图像参差进行二维DCT变换,表达式为:

其中:

X为输入数据,A为变换矩阵,Y为变换结果。H.264对4×4的图像块进行操作,则相应的4×4 DCT变换矩阵A为:

与E的乘法被归纳到量化运算中,这样(CXCT)中只剩下整数的加法、减法和移位运算,因此可以大大降低硬件实现的复杂度,变换结果最多只需要16位的数据。

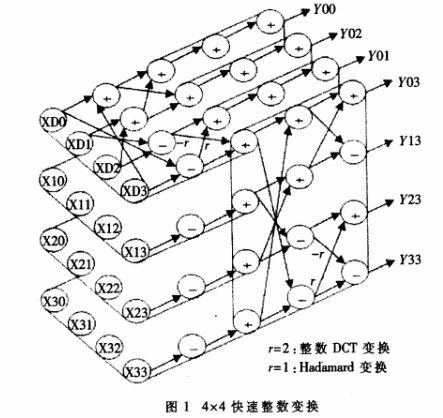

1.2 整数变换硬件结构

本设计H.264中的4×4整数变换采用蝶形快速算法,如图1所示。首先对4×4块的每一行做一维整数变换,然后再对行变换结果做列的一维整数变换,最终得到4×4的整数变换结果。图1模块需要32个加法器和32个减法器,这样在一个时钟周期内就可以完成一个4×4块的整数变换。

整数变换通常的做法是全部使用16位加法器和减法器,这样可以简化设计。然而在实际应用中,输入的像素点范围是[0,255],如果第一级变换就使用16位,则数据宽度无疑会占用更多的硬件资源。根据分析可知,计算一维行变换以后,数据输出范围为[-765,1020],只需使用11位二进制数表示。计算一维列变换以后,数据输出范围是[-3 060,4 080],需要使用13位二进制数表示。因此整数变换模块的数据宽度可以确定为:进行一维行变换时的加法器和减法器使用11位数据宽度,一维列变换的加法器和减法器使用13位数据宽度。

由于数据单向流动的特点,即没有反馈,可以使用流水线提高系统性能。使用流水线时需要注意前后模块处理速率的匹配。如本模块中在行变换与列变换插入缓存构成前后模块,前后模块用同一时钟,并且整个模块的工作频率以最低工作频率的模块来确定。本设计用1级流水线来提高工作频率。如果流水线级数过多会消耗大量FPGA资源,仿真实验证明,此模块使用1级流水线时,只增加极少FPGA资源。

2 量化

为了进一步降低图像传输码率,需要对图像进一步压缩,方法是使用变换编码及量化技术。

2.1 量化原理

H.264中采用标量量化器。标量量化器的原理是:

其中,y为输入样本点编码,Qstep为量化步长,FQ为y的量化值。H.264标准支持52个量化步长。量化的简化操作如下:

其中,Wij为输入样本点编码,MF是标准中定义的值,QP为量化系数,f为偏移量,对帧内预测图像块f取2qbits/3,对帧间预测图像块f取2qbits/6。

2.2 量化器实现

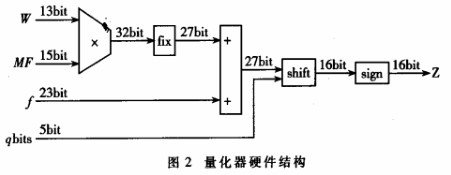

量化器硬件结构如图2所示,其结果是实现对式(4)和式(5)的组合电路。W是需要量化的数据,MF是根据QP和当前点位置在查找表中得到的值。f和qbits是根据QP查表的输出。

为了硬件资源消耗最少,需要分析数据在计算过程中的动态范围,使用最少的数据宽度来表示传输的数据,从而使用最少的硬件资源来实现组合运算逻辑。W是整数变换结果,根据整数变换部分的分析,其取值范围是[-3 060,4 080],MF最大取13 107,乘法器输出动态范围是[-40 107 420,53 476 560],至少用27位二进制数表示。本量化器的乘法器使用Vetex-Ⅱ中的18×18硬件乘法器,因此在输入加法器之前需要将数据宽度调整为27bit。加法器输出的27位数据通过移位模块调整为16位数据宽度。

综合考虑工作频率和资源占用率,设计中使用2级流水线来提高性能。

2.3 量化器优化

本量化器一次只能量化一个点,无法满足高质量图像编码的要求。针对高质量图像编码对此量化器进行速度优化,即将n个量化器并联,一个时钟周期计算n个点。n根据实际需要进行选择。考虑到与变换模块的速度匹配,选择16个量化器并联。

3 软核设计及测试

3.1 PLB总线的软核结构

PLB(Processor Local Bus)总线是IBM开发的一种高性能片上总线,主要应用于PowerPC405处理器系统中,它支持32位、64位和128位数据宽度。本设计使用64位总线宽度,最大速据传输速率达800Mb/s。

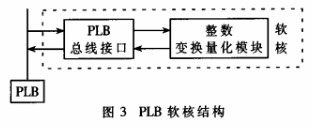

如图3,PLB的软核设计分为总线接口和H.264整数变换量化模块两部分。PLB总线接口是与硬件体系结构相关的部分,它是整数变换量化模块与PLB总线上其他设备进行交互的桥梁。整数变换量化模块与体系结构无关,它也可以被移植到ARM体系结构中。

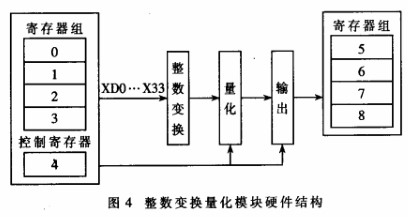

整数变换量化模块的硬件结构如图4。寄存器组包含9个32bit的寄存器,0、1、2、3为输入的4×4参差数据寄存器;5、6、7、8为输出数据寄存器;4为控制寄存器,包括go、done、reset、intra、DCT、ZSCAN、QP、datacount,分别对应启动、完成、复位、帧内/帧间、DCT/Hadamard变换、Z扫描输出、量化级数、数据输出计数器。第二个模块对寄存器组中数据进行4×4整数变换,使用1级流水线。第三个模块对输入的整数变换结果按QP进行量化,量化模块中的MF、f、qbits使用FPGA中的查找表保存。数据输出模块受ZSCAN位控制,当ZSCAN=1时,输出数据寄存器中的数据按Z扫描排列;ZSCAN=0时,按矩阵排列。

3.2 软核的测试

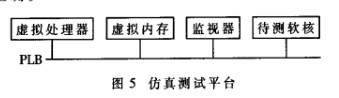

首先使用IBM的CoreConnect工具和Modelsim6.0a来仿真设计的软核并使用虚拟平台进行测试,仿真的目的是保证PLB总线接口能被处理器正确访问。仿真测试平台结构如图5所示。通过虚拟处理器将虚拟内存中的数据写入待测软核,然后读取待测软核中的数据并判断是否正确。

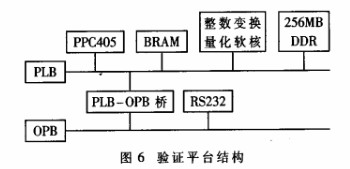

仿真通过以后,再将软核集成到系统中,以便验证软核在实际系统中的工作是否符合要求。验证平台系统结构如图6,软核验证使用PC机和目标板相结合的方法,目标板使用Xilinx公司XUP Virtex-II PRO开发板,内部含有两个PowerPC内核。

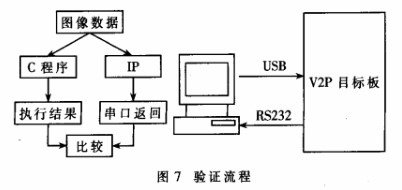

验证流程如图7。首先通过USB口下载目标板程序,程序开始运行以后通过RS232从上位机下载待编码的图像参差数据,下载的数据保存在目标板上的256MB DDR SDRAM中。数据下载完毕后,程序将待编码数据依次写入软核并启动转换,并将计算完的数据写入DDR SDRAM,待全部数据编码完毕,PowerPC将处理结果一起发送给上位机。上位机将结果与本机C代码执行结果相比较,最终确认软核是否正确工作。

4 综合结果分析

本设计中的整数变化量化模块在Xilinx的XC2VP30 FPGA中进行综合。XC2P30含有13 696个Slices和136个18×18乘法器。综合工具使用Xilinx的ISE9.1。

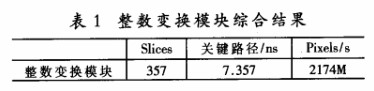

整数变换模块综合结果如表1。

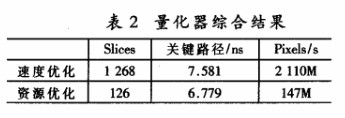

对量化器在速度和硬件资源上分别做了优化,表2给出了两种优化的综合结果。

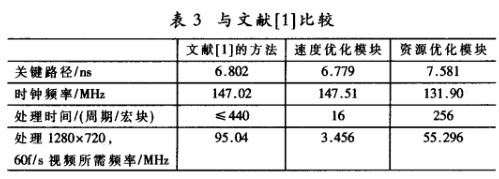

表3给出本设计整数变换量化模块与文献[1]的比较结果。对照发现速度优化软核编码性能远远高于文献[1]的设计,资源优化的软核性能也略高于文献[1]的设计。

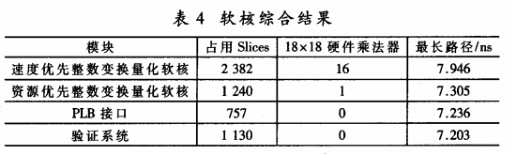

软核综合结果如表4。目前该软核中的PLB接口部分资源占用较大,后续工作对这部分进一步优化。

本文将H.264中的整数变换量化与微处理器系统相结合,针对不同的应用场合实现了两个基于PLB总线的H.264 整数变换量化软核,并在Xilinx XUP Virtex-II PRO开发板中做了验证。实验结果表明,两个软核均能在系统中稳定工作,并能满足不同分辨率的实时应用。

-

基于Blackfin533的H.264编码2011-07-13 3119

-

如何利用PLB总线和FPGA技术对H.264整数变换量化软核实现优化设计?2021-04-08 1111

-

请问怎样实现H.264的量化?2021-04-28 2131

-

分享一款不错的一种基于FPGA高性能H.264变换量化结构设计2021-05-08 1682

-

基于FPGA的H.264去块滤波系统的优化设计2009-04-21 588

-

H.264视频编码在DM642上的实现与优化2009-09-03 778

-

基于TMS320DM642平台的H.264编码器优化2009-12-18 951

-

基于H.264逆量化IP的硬件实现2010-02-24 751

-

H.264/AVC中量化的Verilog方法介绍及实现2009-11-12 1361

-

H.264_AVC视频编码变换量化核实现2012-02-08 2302

-

H.264视频编码器在DM6437上的优化实现2012-05-22 1394

-

基于FPGA的H.264 DCT算法的硬件实现2012-07-31 6784

-

基于DM642的H.264编码算法优化与实现2017-05-18 1752

-

基于FPGA硬件实现H.264变换量化整体结构的设计方案2019-08-01 3227

-

如何在Linux下实现H.264解码器的优化2021-02-25 1097

全部0条评论

快来发表一下你的评论吧 !