CPF低功耗解决方案在在低功耗验证过程中应用分析

描述

为了延长电子便携式产品的电池使用时间,降低设计功耗变得越来越重要。在IC设计流程中,多种电源管理技术逐渐被应用,如clockgating,MSV(Multiple Supply Voltage),PSO(Power ShutOff)。然而这些低功耗技术的引入,对验证工作带来了很大的挑战性。

CPF(Common Power Format)是Cadence公司提出的一套完整的低功耗解决方案。本文根据CPF在低功耗验证过程中的实际使用情况,阐述了如何使用CPF来查找低功耗设计问题以及简化验证工作。

VIA芯片的低功耗设计和验证的挑战

在目前负责的芯片中,用到的主要的低功耗设计技术包括clock gating,MSV(Multiple Supply Voltage)和PSO(Power Shut Off)。CPF主要被用于进行PSO的验证。

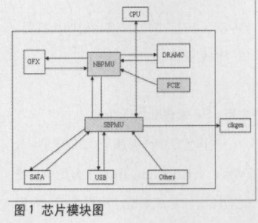

图1是一个芯片结构示意图:黄色区域表示电源always-on的电源域。电源关断的控制信号来自外部。

低功耗芯片设计的验证方式评估

由于RTL代码没有电源信息,因此在RTL通常很难验证到和低功耗设计相关的bug。

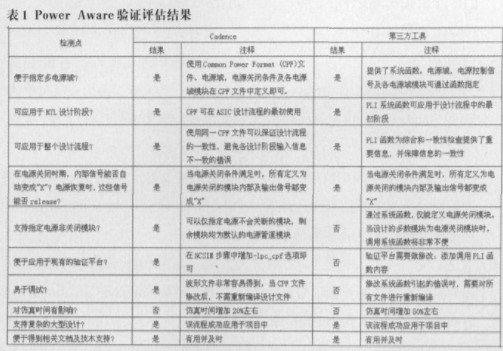

为了实现RTL级代码的power aware验证,我们在2007年第四季度针对支持低功耗设计的验证方式进行了评估,选择了基于CPF的Cadence的流程和另外一家基于PLI方式的低功耗验证方式进行了评估。

表1是评估结果。

应用CPF验证低功耗设计流程

1 将低功耗设计规范写成cpf文件

此步骤在我们的设计中非常简单,下面是一个简单的cpf文件的示意。

# Define the top domain

set_design TOP

# Define the default domain

create_power_domain

-name pdTop -default

# Define Power-Domain A

create_power_domain

-name pdA

-instances {uA uC}

-shutoff_condition {!uPCM/pso[0]}

2 在验证流程中读入cpf文件

应用IDTS进行仿真包括3个步骤:

Ncvlog:编译文件

Ncelab:扩展和链接

Ncsim:进行仿真

进行power aware simulation时,只需要在第二步ncelab增加一个option“-nclps_cpf design.cpf”把第一部产生的cpf读入就可以了。

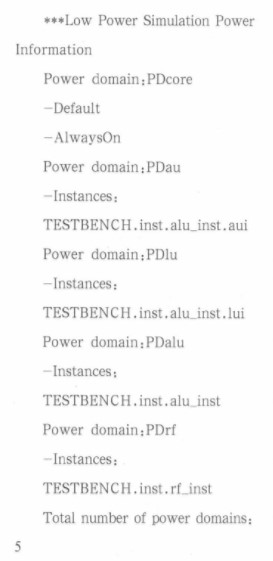

以下是进行仿真之前关于低功耗设计的相关信息:

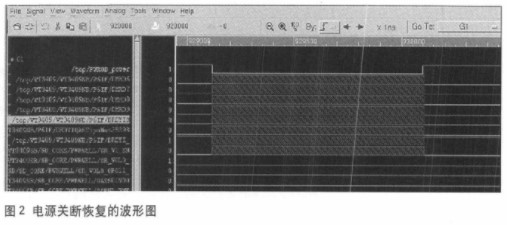

图2是电源关断恢复的波形图。

当对应的电源关断控制信号有效时,对应的power domain中的信号被置为X值。

当对应的电源关断控制信号有效时,对应的power domain中的信号依然为X,当对应的信号恢复程序执行后,信号恢复正常。

应用CPF验证低功耗设计

在选定Cadence基于CPF的power aware verification flow作为此项目的低功耗设计芯片的设计流程之后,我们在其他设计中也应用了此流程,如门级网表设计等。

在应用此流程之后,设计人员得以发现了一些与低功耗设计相关的设计bug,避免了芯片的失败。

由于设计和验证环境都非常复杂,Cadence flow中显现出一些问题:

① default power domain shut-off:

最初CPF文件不支持default power domain可以被关断,导致cpf文件写起来比较麻烦,因为此项目中的design是大部分电路可以被关断,只有部分电路是always-on。

经功能改进后,现在的Cadence在IUS611S011之后的版本中增加了此项功能。

② pass-through信号的处理:

当一个来在always-on domain的信号值通过一个shut-off domain到达一个always-on domain时,此信号被置为X值。

此功能后未被实现在新版本软件中。目前可以有一个选项控制,对于这类信号是保持或者被置为X值。

③force信号的处理:

为实现某些特定功能,在验证环境中增加了一系列force语句。当这些force应用到可以被关断的power domain中的信号时,一旦此模块被关断,又恢复供电之后,这些force将丢失。

目前此功能增强申请正在处理中。

目前我们的低功耗设计技术还比较简单,只应用了电源关断技术。CPF还可以支持信号隔离(isolation),状态保留寄存器(SRPG)等,这在将来的设计中可能使用到。

结束语

通过应用Cadence的基于CPF的power aware验证流程,实现了针对低功耗设计的流程。应用此流程,我们无须对现有流程做修改,并帮助发现设计中如果不应用此流程无法发现的bug,使得开发人员在进行后端设计之前就可以及时发现和低功耗相关的bug。

-

为什么选择 Nordic 的低功耗蓝牙解决方案?2026-04-16 103

-

LEC低功耗检查时,这个错误是什么原因?2024-04-15 1269

-

数据采集系统中降低功耗的解决方案2019-06-10 4293

-

低功耗ADC的低功耗参考和双极电压调节电路精密验证设计2018-11-15 3300

-

关于EDA工具整合低功耗设计、验证和提高生产力的设计2018-11-13 1870

-

基于FRAM的低功耗LED照明解决方案2018-09-10 1787

-

蓝牙低功耗应用的SimpleLink解决方案(4)2018-08-20 3670

-

超低功耗FPGA解决方案助力机器学习2018-05-23 6772

-

小尺寸、超低功耗的智能穿戴定位解决方案2017-09-28 4613

-

低功耗测试解决方案2016-12-29 953

-

Nordic 低功耗蓝牙键盘解决方案2013-11-04 4213

-

提供硬件加密解决方案,待机低功耗解决方案2011-02-15 2154

-

SpringSoft运用先进的低功耗设计侦错解决方案简化低功2010-02-08 1072

全部0条评论

快来发表一下你的评论吧 !