触摸感应电路中的ESD保护结构设计方案

描述

电容式触摸感应检测按键电路是一类对静电特别敏感的电路,因此静电放电(ESD)保护结构的选择问题对这一类电路显得特别重要。一方面要确保所选择的ESD保护结构有足够的抗静电能力,另一方面这种ESD保护结构又不能使芯片的面积和成本增加太多,基于此要求,介绍了3种应用在电容式触摸感应检测按键电路中的ESD保护结构。主要描述了这3种结构的电路形式和版图布局,着重阐述了为满足电容式触摸感应检测按键电路的具体要求而对这3种结构所作的改进。列出了这3种改进过后的ESD保护结构的特点、所占用芯片面积以及抗静电能力测试结果的比较。结果表明,经过改进后的3种ESD保护结构在保护能力、芯片面积利用率以及可靠性等方面都有了非常好的提升。

电容式触摸感应检测按键电路是近年来行业内较高的集成电路产品,这类电路通常设有一路或者多路高灵敏度的感应输入端,实际应用时通过人体手指靠近芯片检测电荷的移动,产生额外电容而改变频率或占空比,从而判断人体手指触摸动作,实现按键功能。众所周知人体是最大的静电携带者,因此在人体手指靠近芯片时会有大量静电向芯片传送,将产生潜在的破坏电压、电流以及电磁场,从而将芯片击毁,这就是静电保护(electronic staticdischarge,ESD)问题。ESD是金属-氧化物-半导体(metal-oxide-semiconductor,MOS)集成电路中最重要的可靠性问题之一,尤其是针对本文所讨论的电容式触摸感应检测按键电路。为了保证高可靠性,这类电路的ESD保护能力通常要求达到8000 V,甚至要达到10 000 V,因此必须通过在电路中加入有效的ESD保护结构才能满足设计要求。此外,这种保护结构又不能占用太多的芯片面积,否则将明显增加芯片成本,从而限制芯片的推广应用。因此如何选择合适的ESD保护结构,既能保护这一类触摸感应按键检测电路,又不至于太多增加芯片成本是这类电路设计中至关重要的问题。

本文介绍了3种应用于笔者所开发的电容式触摸感应检测按键电路中的ESD保护结构。这3种保护结构在传统ESD结构基础上结合电容式触摸感应检测按键电路的具体特点进行全面改进,以达到保护电路且尽量少地增加芯片面积的要求。这些结构也适用于其他类似的电路,希望能够给广大从事集成电路设计的工程师在考虑ESD问题时提供一些参考设计。

1、3种ESD保护结构

1.1、二极管加电阻ESD保护结构

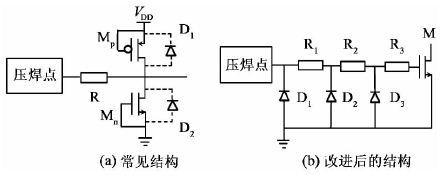

图1(a)是MOS集成电路中最常见的一种ESD保护结构。需要在电路的每一个压焊点都插入该结构,保护图中的Mp和Mn两个MOS管。这种结构包括与压焊点直接相连的栅极和源极短接的PMOS管Mp以及栅极和源极短接的NMOS管Mn.其中Mp和Mn这两个管子可以等效成两个二极管D1和D2.实际应用时在压焊点上会引入较大的静电,根据晶体管原理,这个较大的静电会引起Mp和Mn两个管子被雪崩击穿。通过插入图1(a)中的ESD保护结构,在这个大静电还没有到达Mp和Mn之前首先引起两个二极管D1和D2反向击穿,形成到电源和地的电流通路,把大电流泄放掉;另外电阻R起限流作用。这两个措施就起到了保护Mp和Mn的作用。这种ESD保护结构的ESD保护能力通常在2000~3000V.为了进一步提高ESD保护能力,在电容式触摸感应检测按键电路中对这种结构进行改进,如图1(b)所示。图1(b)显示了一种针对NMOS管的三级二极管加电阻网络的ESD保护结构,针对PMOS管的保护结构与此类似。每一级的原理与图1(a)类似,但这种结构能够利用三级电阻和二极管网络的限流和分压作用提供多个泄放通路,从而逐级泄放大电流,提高ESD保护能力。以图1(b)中的MOS管Mn为例来说明这种改进的ESD保护结构的电路结构参数应该如何选择。Mn的栅击穿电压是12.5V,按照ESD保护原理,经过多级限流电阻之后落在Mn栅极的电压须小于这个管子的栅击穿电压,保护电路才能起到保护作用,通过计算,采用三级二极管加电阻网络结构可以达到保护Mn的目的,其中每一级限流电阻值为100Ω,而D1,D2和D3 3个二极管也可以采用图1(a)中所示的栅极和源极短接的MOS管。

1.2、可控硅整流器的ESD保护结构

图2(a)是可控硅整流器(silicon controlledrectifiers,SCR)ESD保护结构的纵向剖面图,图2(b)是这种结构的等效电路图。

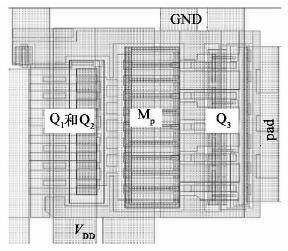

图2(b)中Mp是一个栅极和源极短接的PMOS管,起到ESD保护作用;Q1是一个pnp型三极管,其发射区是由n阱内的p+扩散区构成,n阱是它的基区,p衬底作为集电区;另一个Q2是npn型三极管,阱外的n+是其发射区,p衬底是它的基区,n阱是集电区。以上两个管子组成一个称之为可控硅整流器的4层半导体器件。这4层依次是p+扩散区、n阱、p衬底和n+扩散区,此种pnpn结构内有npn和pnp之间的正反馈,提供了良好的ESD泄放通路,具有非常明显的ESD保护性能。因此在芯片的每一个压焊点上都插入这样一个结构,就能在最小的布局面积下提供最高的ESD防护能力。图2(b)中R1是n阱接触电阻,R2是p衬底接触电阻。

据半导体器件原理,上述的4层结构作为ESD保护器件来说,其起始导通电压等效于MOS工艺下n阱与p衬底之间的击穿电压。由于n阱具有较低的掺杂浓度,这是由半导体工艺所决定的,因此其与p衬底之间的击穿电压高达30~50V,如此高的击穿电压使SCR结构在ESD防护设计上需要再加上额外的二级保护结构,在图2(b)中已经标注出来。这是因为图2(b)中需要保护的MOS管M的栅击穿电压只有12.5V左右,而SCR要到30V以上才导通,在ESD电压尚未升到30V之前,这个SCR结构是关闭的,这时SCR器件所要保护的M管早就被ESD电压破坏了,因此必须加入二级保护结构。利用这个二级保护结构,在其被ESD破坏之前,SCR结构能够被触发导通,从而泄放ESD电流,只要SCR结构一导通,其低的保持电压便会钳制住ESD电压在很低的值,因此这个SCR结构可以有效地保护M管。但这种额外增加的二级保护结构必然会造成芯片面积的增加,导致芯片成本的上升。

为解决这个问题,在电容式触摸感应检测按键电路中采用了一种改进的SCR ESD保护结构。在该结构中增加一个图2(b)虚线框中所示的薄栅氧NMOS管Q3.依据晶体管原理,击穿电压与栅氧是直接相关的。这个NMOS管以橫跨的方式在n阱与p衬底的界面上,可以使SCR结构的起始导通电压下降到10~15V,这就使SCR结构不需要额外的二级保护结构便可以有效地保护电路内部M管,从而减小了芯片面积。SCR结构的导通过程描述如下:其内嵌的薄栅NMOS管Q3发生回流击穿时,引发电流自其栅极流向p衬底,这会引起电流自n阱流向p衬底,也因而触发了SCR结构的导通。为了防止SCR结构在普通MOS管正常工作情形下会被导通,其内嵌的薄栅NMOS管Q3的栅极必须要连接到地,以保持该NMOS管关闭,如图2(b)所示。

图3显示了改进的SCR ESD保护结构的版图,包括作为ESD保护器件的Q1,Q2和宽长比为180/1的PMOS管Mp,还有就是作为ESD二级保护器件的薄栅管Q3.图中VDD是管子所接的电源端,GND是管子所接的地端。

1.3、全芯片ESD保护结构、

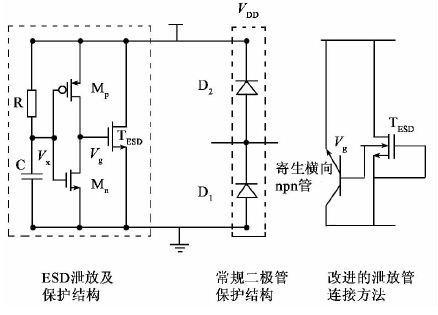

图4显示了一种全芯片的ESD保护电路结构。这种保护结构由ESD泄放及保护结构和常规二极管保护结构两部分组成。其中ESD泄放及保护结构由RC网络、Mp和Mn两个逻辑控制管以及ESD电流泄放管TESD等组成。这部分原理简述如下:ESD对电路的损伤主要是电路的pn逆向击穿造成的不可逆而导致电路漏电。当VDD网络上出现ESD电压时,图中Vx点的初始电压为零,由于电容的“惰性”,其两端电压不能突变,因此Mp管导通,Vg端电压将随着ESD电压上升,TESD管导通,为ESD电流提供了一条到地的泄放通路。TESD的薄栅氧决定了图中Vg点的电压不能上升太高,否则会击穿栅氧从而损坏器件。因此RC网络充电抬高Vx端电压,限制Vg升高,RC充电时间一定要能够保证ESD能泄放完才关断Mn管,一般要求在200ns左右,要求TESD管的设计能够承载大电流,因此要设计足够的栅宽长比。正常情况下,TESD管的栅压为0V,其实是关闭的,因此不影响芯片的正常工作。

这种全芯片的ESD保护结构能够很好地提高电路的ESD保护能力,但当半导体工艺到深亚微米阶段,为了防止热载流子效应,都会在MOS的源漏端采用浅掺杂( lightly doped drain,LDD)结构。图4中的TESD管就采用了LDD结构。当TESD管导通泄放ESD电流时,大电流从这个管子的表面通过,这样结深很浅的浅掺杂处很容易损坏,从而限制了这种全芯片ESD保护结构的防护能力。

在电容式触摸感应检测按键电路中采用了一种改进的全芯片ESD保护结构,改进的是ESD电流泄放管TESD的连接方式,如图4所示。经过改进后,TESD管的栅接地,而Vg输出接TESD管的衬底,其余器件结构和参数保持不变。与通常的全芯片ESD保护结构相比,这种改进的全芯片ESD保护结构引入了寄生的横向npn管,如图4所示。

在这种改进的全芯片ESD结构中,当VDD网络上出现ESD电压时,会引起Vg电压变化,由于电压的存在,会引起衬底上电子的迁移而形成电流,电流流过衬底电阻后会抬高寄生npn管的基极电压,最终会触发这个npn管的导通,这时ESD电流是通过npn管在衬底上流过而不是在MOS管表面流过,TESD管并没有开启而是用其寄生的横向npn管来泄放ESD电流,而LDD结构不会受到ESD电流的损害,这样就能大幅提高这种保护电路ESD防护能力。

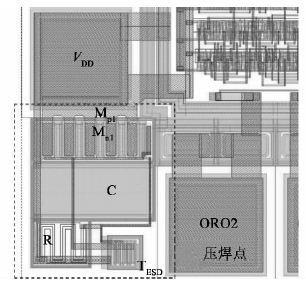

图5中虚线框部分是这种改进的全芯片ESD保护结构的版图,该图显示了逻辑控制管Mp,Mn和RC网络以及最重要的薄栅管TESD的位置,其中电容与其下的阱电阻组成ESD探测器。从图5可以看出,一个全芯片的ESD保护结构所占的芯片面积只比一个压焊点的面积略大,也就是说在某一个芯片中插入这种全芯片的ESD保护结构后,不会引起该芯片的面积增加太多,但可以大大提高该芯片的ESD保护能力。

2、3种ESD保护结构比较和测试结果

2.1、3种结构在不同ESD测试模式下的优劣性比较

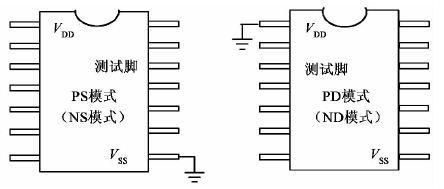

对于芯片的每个端口,都有4种ESD的测试模式,针对±VDD和±VSS模式进行测试,分别称为所有测试脚对+VDD的PS模式,所有测试脚对-VDD的NS模式,所有测试脚对+VSS的PD模式和所有测试脚对-VSS的ND模式。如图6所示,针对其中某一个测试脚,施加正的或负的ESD电压,其余不测的端口全部悬空,只有当4种模式全部成功通过某一电压(如4000V)测试,才能认为此端口的ESD保护能力达到了4000V.

对于二极管加电阻的ESD保护结构,其中二极管通常采用栅极接地的NMOS管和栅极接电源的PMOS管来实现。采用这种ESD保护结构的电路一般对NS和PD两种测试模式的ESD能力保护比较高,而针对ND和PS两种测试模式的ESD保护能力则要差许多。这是因为在NS测试模式下某一个测试脚上接入负的ESD电压,NMOS管寄生的二极管正向导通,同理PD模式下VDD端接地,某一个测试脚上接入正ESD电压,PMOS寄生的二极管正向导通,如图1(b)所示。在ND和PS模式下,寄生二极管需要反向击穿来泄放ESD电流。对于某一特定器件所能承受的ESD能量是固定的,二极管的正向导通电压为0.7V左右,远小于其反向击穿电压,因此二极管正向导通时能承受的ESD泄放电流也远远大于其反向击穿时,即ESD电压远高于反向击穿时的ESD电压。因此ND和PS模式下ESD保护能力差是这种保护结构的缺点。

同样,可控硅整流器ESD保护结构也有同样的问题。全芯片ESD保护电路正好可以解决这个问题,从而显示出这种结构较前两种结构的优越性。原理简述如下:以PS模式为例,电源脚悬空,地脚接低电平,在没有全芯片ESD保护电路时,D1寄生二极管将反向击穿泄放ESD电流,而现在ESD电压则会通过D2充到VDD网络上,如图4所示,再通过ESD保护电路泄放到地。以上ESD泄露方式避免了D1反向击穿情况的出现,同理ND模式也可以用这种思路分析。

2.2、3种结构所占用的芯片面积以及ESD耐压测试结果比较

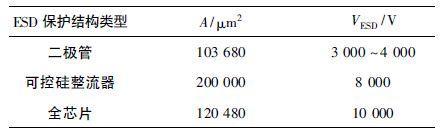

将以上3种结构应用到电容式触摸感应按键检测电路的设计中,芯片采用的是0.35μm MOS工艺,共有10个压焊点。3种结构所占用的芯片面积如表1所示。表中A为ESD结构所占用的芯片面积,VESD为ESD耐压测试的电压。

对采用3种改进的ESD保护结构的芯片进行ESD耐压测试,结果如表1所示。从表1比较结果可以看出,全芯片ESD保护结构比二极管ESD保护结构所占用的芯片面积增加了16800μm2,面积增加的比例为16%,但ESD保护能力提高了2倍多;而跟可控硅整流器ESD保护结构相比,全芯片ESD保护结构所占的芯片面积只有可控硅整流器ESD保护结构的60%,但ESD保护能力却提高了2000V,表明全芯片ESD保护结构具有最好的ESD保护能力。

2.3、3种结构的ESD保护能力测试结果

用ESD模型之一的人体模型工业测试标准HBMMIL—STD—883F3.15.7对采用以上3种改进后的ESD保护结构的电容式触摸感应检测按键电路进行ESD保护能力测试。以PS模式为例具体说明测试方法如下:每种电路准备3个样品,这3个样品首先必须通过功能的测试;电源脚悬空,地脚接低电平,其他所有管脚也都浮悬空,在某一个测试脚上施加正电压来等效实际电路使用时所承受的正的ESD电压,起始电压为500V,以后每做一次测试电压往上增加500V,也就是说步进电压为500V;然后监控该测试脚在施加ESD电压前后的电流-电压曲线,通常采用包络线法来判断施加ESD电压前后测试脚的电流-电压曲线的变化。当相对包络线小于15%判断为施加ESD电压前后的电流-电压曲线没有变化,该管脚还可以承受更高的ESD电压。继续往上增加电压,直到超出15%这个范围,比如加到4500V,相对包络线超出了15%,就表明该测试管脚已经超过了ESD承受范围,而这时所加的ESD电压4500V的前一档,也就是说4000V就是该测试脚所能承受的最高ESD电压;再对该测试脚进行NS,PD和ND等其他3种模式的测试,如果4种模式都能通过4000V,并且经过ESD打击后电路的功能没有改变,还要3个样品都能重复该试验,这才表示这个管脚的ESD耐压为4000V.

通常ESD水平分为三级:一级为0~1999V;二级为2000~3999V;三级为4000~8000V.对于一些特殊的应用,ESD耐压要求超过10000V,那就是在三级的基础上继续往上增加ESD电压,直到所加电压超过10000V,并且测试脚的电流-电压曲线没有变化,表明该芯片的ESD耐压可以高达10000V.

3、结语

电容式触摸感应检测按键电路要求具有特别高的ESD保护能力,因此必须采用有效的ESD保护结构。本文列举了二极管加电阻、可控硅整流器和全芯片等3种ESD保护结构,并重点针对电容式触摸感应检测按键电路的结构和工艺特点,提出了对这3种保护结构的改进措施。结果表明经过改进后的3种ESD保护结构在保护能力、芯片面积的利用率以及可靠性等方面都有了非常好的提升,其中全芯片ESD保护结构占用的芯片面积最小,且针对所有ESD测试模式都有最好的ESD保护能力,这种结构可以推广到其他类型集成电路的ESD保护结构设计中。

-

操作系统结构设计2011-09-13 2505

-

求助触摸感应电路的问题2013-05-22 2661

-

招聘--结构设计师2015-09-25 2920

-

浅谈产品结构设计特点2016-02-25 5899

-

软件结构设计2016-09-26 2514

-

常见的ESD保护结构有哪几种?对比分析哪个好?2021-04-13 3876

-

CMOS电路中ESD保护结构的设计2009-12-14 960

-

结构设计中的钢筋混凝土构造2010-04-26 1026

-

轴系结构设计实验2009-03-13 59206

-

亚微米CMOS电路中VDD-VSSESD保护结构设计2012-04-23 4705

-

CMOS电路的ESD保护结构设计2019-04-08 2992

-

电容式触摸感应电路中的3种ESD保护结构资料下载2021-04-18 1225

-

CMOS电路的ESD保护结构设计资料下载2021-04-21 1091

-

机械结构设计解决方案2023-09-21 3180

-

SoC系统中的软件结构设计2023-09-25 1871

全部0条评论

快来发表一下你的评论吧 !