D类音频功率放大器设计基础,D类功放设计

描述

D类音频功率放大器设计基础,D类功放设计

关键字:D类功放设计

D功放是基于脉冲宽度调制技术的开关放大器,包括脉冲宽度调制器(几百千赫兹开关频率),功率桥电路,低通滤波器。本文从构成、拓扑结构对比、MOSFET的选择与功率损耗、失真和噪音产生、音频性能等D类音频功率放大器设计有关的基础问题作分析,并例举D类功率放大器参考设计。

1、 D类功放基本构成

目前有很多种不同种类的功放,如:A类、B类、AB类等。但D类功放与其不同的是基本是一个开关功放或者是脉宽调制功放。为此,主要将对说明这类D类功放作以说明。

在这种D类功放中,器件要么完全导通,要么完全关闭,大幅度减少了输出器件的功耗,效率达90-95%都是可能的。音频信号是用来调制PWM载波信号,其载波信号可以驱动输出器件,用最后的低通滤波器去除高频PWM载波频率。

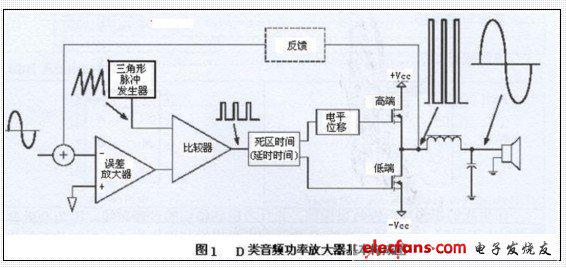

众所周知, A类、B类和AB类功放均是线形功放,那么D类功放与它们究竟有什么不同?我们首先应作讨论。图1是D功放原理框图,在一个线性功放中信号总是停留在模拟区,输出晶体管(器件)担当线性调整器来调整输出电压。这样在输出器件上存在着电压降,其结果降低了效率。

而D类功放采用了很多种不同的形式,一些是数字输入,还有一些是模拟输入,在这里我们将集中讨论一下模拟输入。

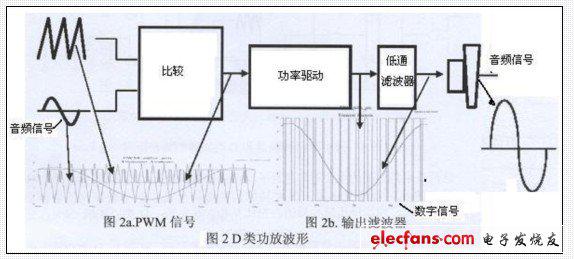

上面图1显示的是半桥D类功放的基本功能图,其中给出了每级的波形。电路运用从半桥输出的反馈来补偿母线电压的变化。那末D类功放是如何工作的呢?D类功放的工作原理和PWM的电源是相同的,我们假设输入信号是一个标准的音频信号,而这个音频信号是正弦波,典型频率从20Hz到20kHz范围。这个信号和高频三角或锯齿波形相比可以产生PWM信号,见图2a中所示。这个PWM信号被用来驱动功率级,产生放大的数字信号,最后一个低通过滤波器被用在这个信号上来滤掉PWM载波频率,重新得到正弦波音频信号,见图2b中所示。

2、 从拓扑结构对比-看线性和D类不同

值此将讨论线性功放(A类和AB类)和D类数字功放的不同之处。这两者之间主要的不同是效率,这也是为什么要发明D类功放的原因。线性功放就其性能而言具有固有的线性,但是即使是AB功放其效率也只有50%,而D类功放的效率很高,在实际的设计中达90%。

增益-线性功放增益不受母线电压影响而变化,然而D类功放的增益是和母线电压成比例的。这就意味着D类功放的电源抗扰比率是0dB,而线性的PSRR(电源供应抑制比率)就很好。在D类功放中普遍用反馈来补偿母线电压变化。

能量流向-在线性功放中,能量是从电源到负载,虽然在全桥D类功放中也是这样,但半桥D类功放还是不同的,因为能量可以双向流动而导致“母线电压提升”现象产生,这样会造成母线电容被从加载来的能量充电。这个主要发生在低频上,如低于100Hz是这样。

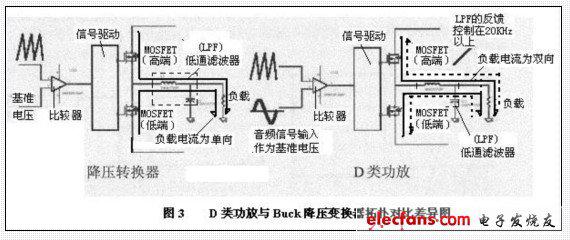

3、 D类功放与Buck降压转换器类拓扑差异

在D类功放和同步降压转换器拓扑原理作如图3所示。这两个电路之间的主要不同有三:其一、对于同步降压转换器,其基准电压来自反馈电路的慢慢变化的稳定电压;而D类功放的参考信号是一个不断变化的音频信号。也就是说,同步降压转换器的占空比是相对稳定的,而D类以围绕50%占空比不断地改变。其二、在同步降压转换器中负载电流的方向总是朝着负载,即电感电流为单向,见图3左所示。但是在D类功放中电流是朝着两个方向的,即电感电流为双向,见图3右所示。最后的不同是MOSFET的优化方式。同步降压转换器对于高低端的晶体管有着不同的优化,较长的周期需要较低的Rds(on),而较短的周期需要低的Qg(栅极电荷),即两个开关作用不同。但D类功放对两个MOSFET有着相同的优化方式。高低端器件有相同的Ras(on),即两个开关作用相同。

4、 D类功放中MOSFET的选择

在功放中要达到高性能的关键因素是功率桥电路中的开关。在开关过程中产生的功率损耗、死区时间和电压、电流瞬时毛刺等都应该尽可能的最小化来改善功放的性能。因此,在这种功放中开关要做到低的电压降,快速的开关时间和低杂散电感。

由于MOSFET开关速度很快,对于这种功放它是你最好的选择。它是一个多数载流子器件,相对于IGBT和BJT它的开关时间比较快,因而在功放中有比较好的效率和线性度。而MOSFET的选择是基于功放规格而定。因而在选择器件以前要知道输出功率和负载阻抗(如100W 8Ω),功率电路拓扑(如半桥梁或全桥),调制度(如89%—90%)。

5、 MOSFET中的功率损耗

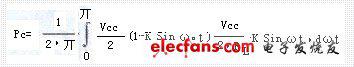

功率开关中的损失在AB线性功放和D类功放之间是截然不同的。首先看一下在线性AB功放中的损耗,其损耗可以定义如下:

K是母线电压与输出电压的比率。

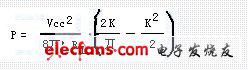

对于线性功放功率器件损耗,可以简化成下面的公式:

需要说明的是AB功放功率损耗与输出器件参数无关。

现在一起看一下D类功放的损失,在输出器件中的全部损耗如下:

Ptotal=Psw+Pcond+Pgd

Psw是开关损耗

Pcond是导通损耗,

Pgd是栅极驱动损耗

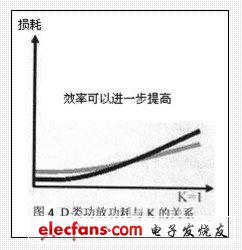

从上式可看于D类功放的输出损耗是根据器件的参数来定的,即基于Qg(栅极电荷)、Rds(on)(静态漏源通态电阻)、Coss(MOSFET的输出电容)和tf(MOSFET下降时间),所以减少D类功放损耗应有效选择器件,图4是D类功放的功率损耗和K的函数关系。

6、 半桥和全桥结构拓扑的对比

和普通的AB类功放相似,D类功放可以归类成两种拓扑,分别是半桥和全桥结构。每种拓扑都各有利弊。简而言之,半桥简单,而全桥在音频性能上更好一些,全桥拓扑需要两个半桥功放,这样就需要更多的元器件。尽管如此,桥拓扑的固有差分输出结构可以消除谐波失真和直流偏置,就像在AB功放中一样。一个全桥拓扑允许用更好的PWM调制方案,比如量化几乎没有错误的三水平PWM方案。

在半桥拓扑中,电源面临从功放返回来的能量而导致严重的母线电压波动,特别是当功放输出低频信号到负载时。能量回流到电源是D类功放的一个基本特性。在全桥中的一个臂倾向于消耗另一个臂的能量。所以就没有可以回流的能量。

7、 不完美失真和噪音产生

一个理想的D类功放没有失真,在可听波段没有噪音且效率足100%。然而,实际的D类功放并不完美并且会有失真和噪音。其不完美是由于D类功放产生的失真开关波形造成的。原因是:

*从调制器到开关级由于分辨率限制和时间抖动而导致的PWM信号中的非线性。

*加在栅极驱动上的时间误差,如死区时间,开通关断时间,上升下降时间。

*开关器件上的不必要特征,比如限定电阻,限定开关速度或体二极管特征。

*杂散参数导致过度边缘的震荡。

*由于限定的输出电阻和通过直流母线的能量的反作用而引起得电源电压波动

*输出LPF中的非线性。

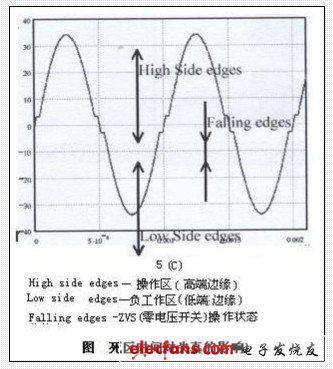

一般来讲,在栅极信号中的开关时间误差是导致非线性的主要原因。特别是死区时间严重影响了D类功放的线性。几十纳秒少量的死区时间很容易就产生1%以上的THD(总谐波失真),见图5(c)所示。

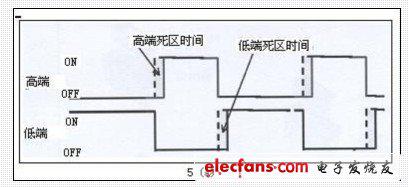

8、 死区时间(见图5(a)所示是如何影响非线性的)

其图5(a)(b)(c)为死区时间(或称延时时间)对失真的影响示意图。D类输出级中的工作模式可以根据输出波形如何跟随输入时间可归类成三个不同的区域。在这三个不同的工作区,输出波形跟随高低端输入信号的不同边缘而变化的。

让我们检查一下第一个操作区(见图5c所示High side edges),在这里电流比电感器波纹电流还大时,输出电流就从D类功放流向负载。高端器件在低端器件开通之前关断,输出节点就会被转到负母线。这个过程与低端器件开通时间无关,它是通过从解调电感的换向电流自动造成的。因此输出波形与嵌入到低端器件开通前的死区时间无关。因此PWM波形只被嵌入到高端栅极信号的死区短路了,而造成所希望的输入占空比的轻微电压增益降低。

有个相似的情况发生在负工作区(见图5c所示Low side edges),输出电流从加载流向D类功放。电流高于电感波纹电流。在这种情况下,输出波形的时间并没有受嵌入高端开通沿的死区时间的影响,而总是允许低端输入时间。因此,PWM波形只被嵌入到低端器件栅极信号的死区时间短路。

在以前描述的两个操作模式中存在一个区域,在这个区域中输出时间与死区时间是独立的。当输出电流小于电感波纹电流时,输出时间跟随每个输入的关断沿。因为在这个区域,是ZVS(零电压开关)操作状态(见图5c所示Falling edges),因此在中间区域就不会有失真。

当输出电流随着音频输入信号的不同而变化时,D类功放将改变它的操作区,这样每个都会有细小的不同增益。在音频信号的周期中的这三个不同区域增议会歪曲输出波形。

图5(b)显示的是死区时间如何影响THD性能的。一个40nS死区时间可以产生2%的THD。这个可以通过减小死区时间到15nS提高到0.2%。这个标志着更好线性与高低端开关器件转换过程的重要性。

9、 音频性能测量

有着AESl7网络过滤器的音频测量仪器是很必需的。当然,像传统音频分析器HP8903B,加上合适的前级低通滤波器也可以使用。在这里需要重要考虑的是D类功放的输出信号在其波形上仍然含有大量的开关载波频率,这样就造成错误的读取。这些分析器也许很难防止D类功放的载波泄露。

10、防止直通

尽管如此,一个狭窄的死区时间在大量生产中是很危险的。因为一旦高低端晶体管被同时打开,那么直流母线的电压就会被晶体管短路,大量的直通电流将开始流动,这便会导致器件损坏。我们应该注意到有效的死区时间对每个功放是不同的,与元件参数和芯片温度有关。对于一个D类功放的可靠设计来讲确保死区时间总是正的而决不是负的来防止晶体管进入直通,这是非常重要的。

11、关于电源吸收能量

另外一个在D类功放中引起明显降额的原因是母线充电,当半桥拓扑在给负载输出低频时可以看到。要时刻记住,D类功放的增益与母线电压直接成比例关系。因此,母线电压波动产生失真,而D类功放中的电流流动是双向的,则就存在了从功放返回到电源时期。大量流回到电源的能量来自于输出LPF的电感存储的能量。通常,电源没有办法吸收从负载回流过来的能量。因此,母线电压上升,造成电压波动。母线电压上升并不是发生在全桥拓扑上,因为从开关桥臂同储到由源的能源熔会在另一个桥臂消耗掉。

12、对EMI(电磁辐射)的考虑

在D功放设计中的EMI(电磁辐射)是很麻烦的,像在其他开关应用中一样。EMI的主要来源之一是来自从高到低流动的MOSFET二极管的反向恢复电荷,和电流直通很相象。在嵌入到阻止直通电流的死区过程中,在输出LPF中的电感电流打开体二极管。在下一个阶段中,当另外一端的MOSFET在死区未打开时,体晶体管保持导通状态,除非储存的大量少数载波被完全复合。这个反向的恢复电流趋向于形成一个很尖的形状,和由于PCB板和封装杂散电感因起步希望的震荡。因此,PCB布线设计对减小EMI和系统可靠性至关重要的。

13、D类功放中MOSFET选择的其他考虑

*选择合适的封装和结构

*功放的THD、EMI和效率,还受FET的体二极管影响。缩短体二极管恢复时间(工R的并联肖特基二级管的FET);降低反向恢复电流和电荷,能改善THD;EMI和效率。

*FET结壳热阻要尽可能小,以保证结温低于限制。

*保证较好可靠性和低的成本条件下,工作在最大结温。用绝缘包封的器件是直接安装还是用裸底板结构垫绝缘材料,依赖于它的成本和尺寸。

14、D类功放参考设计见图6所示

*拓扑:半桥

*选用IR2011S(栅极驱动IC,最高工作电压200V,Io+/-为1.0A/1.0A,Vout为10-20V,ton/off为80&60ns,延时匹配时间为20ns);IRFB23N15D (MOSFET功率管ID=23A,R DS=90mΩ,Qg=37nC Bv=150V To-220封装)

*开关频率:400KHz(可调)

*额定输出:200W+200W/4欧

*THD:0.03%-1mhz半功率

*频率响应:5Hz-40KHz(-3dB)

*电源:~220v±50V

*尺寸:4.0“×5.5”

15、结论

如果我们在选择器件时很谨慎,并且考虑到精细的设计布线,因为杂散参数有很大的影响,那么目前高效D类功放可以提供和传统的AB类功放类似的性能。

-

什么是 D类音频功率放大器2022-10-09 7938

-

D类音频功率放大器设计基础2012-03-07 26615

-

d类音频功率放大器pdf2008-06-23 9652

-

D类音频功率放大器控制方式综述2011-03-06 6655

-

浅析D类音频功率放大器2019-05-23 2262

-

D类音频功率放大器HXT2603资料分享2021-04-06 1687

-

D类音频功率放大器HXT8403电子资料2021-04-09 1390

-

D类数字音频功率放大器有什么优势?面临哪些挑战?2021-06-07 2061

-

D类音频功率放大器的环路设计2009-12-14 955

-

基于PWM的D类音频功率放大器设计2009-12-15 1566

-

D类音频功率放大器的关键技术2011-08-16 2044

-

D类音频功率放大器的研究与设计2016-08-30 1734

-

D类音频功率放大器的应用优势分析2019-08-01 8163

-

D类和E类功率放大器的应用2021-05-27 1420

-

D类音频功率放大器概述2021-05-28 1685

全部0条评论

快来发表一下你的评论吧 !