浅析音响各种pop音及功放的阻抗匹配

电子说

描述

启动和关闭时序

为了优化开关机的POP 声和避免DC Detect 功能的误触发,在系统设计时需要注意主芯片和功放 器件的启动时序。启动时序分为电源时序和使能时序两种,电源时序是指系统中各种芯片电源供电或断电的时序。而使能时序可理解为系统供电稳定后由系统主控决定的器件功能使能的先后次序。

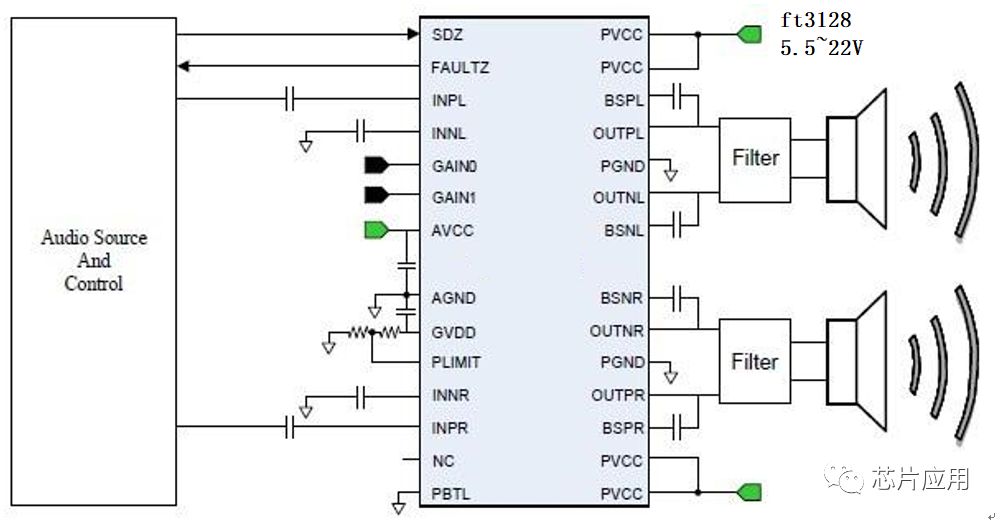

对于电源时序来说,由于多数主芯片的音频输出在上电和断电过程中不太稳定,理想的上电次序是系统主芯片先于功放 上电。然后功放 的PVCC 再供电。断电的理想时序正好相反,为功放 的电源先切断,然后再切断主控芯片的供电。

但是通常功放 的PVCC 取自于系统的主电源,该电源一般在开机后最先输出。随后再通过DC/DC 或LDO 降压给主芯片供电。所以功放 一般在主芯片稳定前已经供电并启动。这种设计中,上电时必须保证TPA311x 的/SD 脚处于拉低状态,避免主芯片上电过程中的POP 声输出。掉电时,也需要将功放 置于standby 状态,避免主芯片掉电时的POP 声输出。通常上电过程的POP 声较容易解决,但系统掉电时需要使用掉电检测电路来强制将功放 的/SD 快速拉低来解决掉电POP 声的问题。

使能时序:由于主芯片音频模拟输出的偏置电压一般在输出使能后建立,此时需要保持功放 的/SD 拉低,等待主芯片模拟输出的偏置电压稳定后才可以将/SD 置高开启功放。相反,需要关闭主芯片音频模拟输出功能时,需要先拉低/SD 将功放关闭后,再关闭主芯片的模拟输出信号。这样的时序是为了保证主芯片模拟输出的偏置电压掉电时不会引起POP 声。

输入级模型

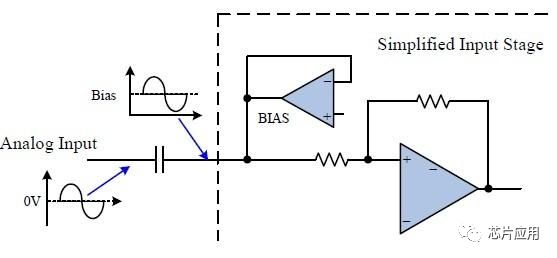

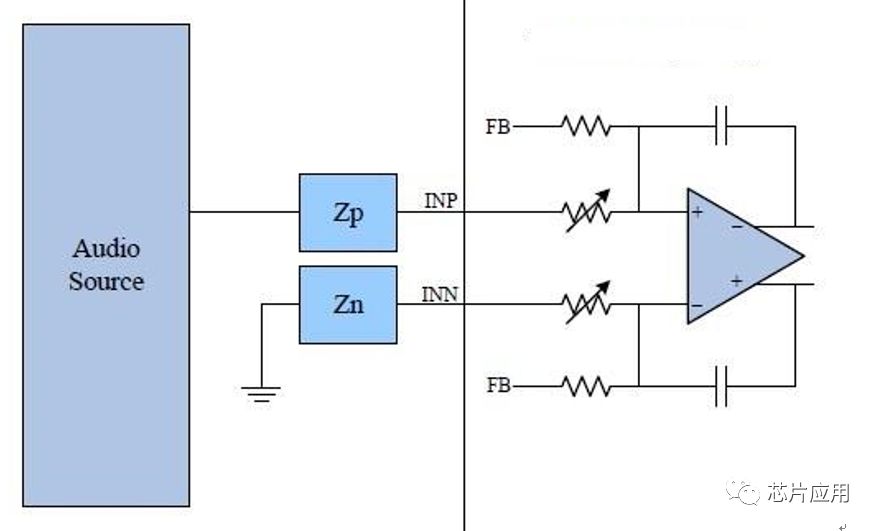

功放 是单电源供电的模拟输入Class D 功放,这类功放的模拟输入必须工作在直流偏置(DC BIAS)点上才可以正常传输交流音频信号,简化的输入级模型如图1 所示。功放 的直流偏置电压设定在3V。

图 1. 模拟输入级等效模型

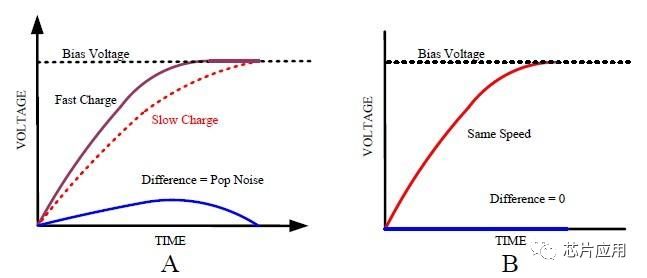

功放在启动时,偏置电压会从0V 上升到额定的偏置电压,该过程的时间长短取决于内部偏置电压源对外部阻抗网络的充电速度。

图 2. 差分输入偏置电压建立过程

功放 差分输入INN 和INP 的输入偏置电压建立的过程如图2所示,若差分输入N 和P 端的输入偏置电压建立速度不一样则两者之差会形成差分信号输入功放并被放大输出,形成启动时的POP 声。差分输入端偏置电压建立过程的不平衡通常是因为输入级INN 和INP外部的阻抗不匹配所致。这种情况最容易出现在差分输入用作单端输入状态。

功放 的单端输入方式

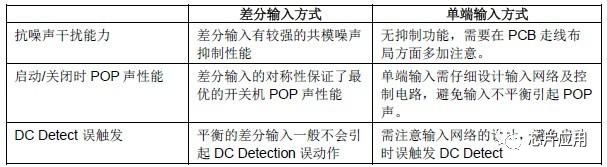

功放 器件的模拟输入是标准的差分输入接口。在系统设计中,推荐使用差分输入方式来接驳主芯片的音频输出。使用差分输入方式可以不仅POP 声的控制相对简单、信号抗干扰能力强,而且不会引起DC Detection 功能的误动作。差分输入方式和单端输入方式的对比如下表所示:

表 1. 差分、单端输入方式对比表

不过在实际应用中,由于多数主芯片的音频模拟输出是单端模式, 功放 的差分输入必须配置为单端接法才能使用。如图3 所示,单端输入时,主芯片输出通过耦合电容连接功放INP(INN) 脚。INN (INP)输入通过电容耦合到地即可。

图 3. 功放 单端输入接法

使用单端输入模式时需注意以下几点:

1. 单端输入模式应用时需要更加注意音频信号的走线和地平面的分布,因为单端输入模式没有能力抑制系统中的公模干扰信号。

2. 相比差分信号输入模式下,单端输入,需要输入两倍的输入信号电平来达到相同的输出功率。

3. 单端输入模式必须注意P/N 脚电路网络的阻抗匹配,尽量不要在输入级使用复杂的滤波网络。不合适的阻抗网络不仅会引起开关机的POP 声,也有可能引起DC Detection 功能的误触发,导致功放锁死。若必须在输入级进行滤波或增益设置,请参考使用运放来进行滤波及增益的调节。

输入阻抗网络的匹配

若使用单端输入的方式连接功放 ,则必须注意输入阻抗网络的匹配问题。如图5 所示,功放的INN 输入端外部阻抗为Zn,通常Zn 为耦合电容。主芯片输出阻抗一般很小,可认为输出阻抗为零,则INP 输入端外部阻抗约为Zp。功放启动时内部的偏置电压会逐步建立,其过程即为向Zn 和Zp 阻抗网络充电的过程。若Zn 和Zp 阻抗相差太大,INN 和INP 之间就会形成较大的差分信号,该差分信号被功放放大之后则形成POP 声。

功放设计的启动时间举例30ms,该时间是从/SD 被拉高到功放输出声音的时间。若上述启动时对输入阻抗网络的充电稳定时间少于30mS,则因阻抗不匹配引起的差分输入也不会被放大而带来POP 声的问题。减小Zn 和Zp 中的电容参数可以缩短输入级稳定时间,但减小电容会使得低频增益降低,用户需酌情考虑。

图 4. 匹配输入阻抗

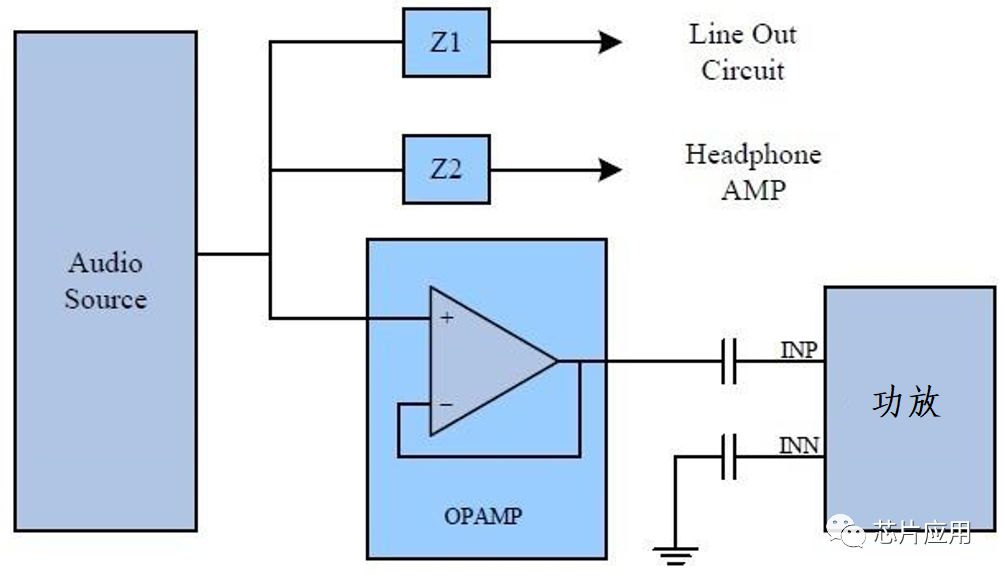

使用运放建立隔离系统

在某些系统中,主芯片的音频信号输出不仅需要连接到功放输入,还要输出到Line Out(线路输出),或者其他的芯片进行处理。该种情况下输入级的网络比较复杂,单端输入模式的阻抗匹配不容易实现。为了解决这个问题,可以使用运放接成一个简单的跟随器来建立一个隔离的阻抗输入系统。跟随器的输入阻抗很高,对源信号没有影响。其输出阻抗非常低,可良好匹配功放 的输入阻抗网络。图 5 给出了使用跟随器来建立一个隔离的输入阻抗网络的电路。需要时,还可将运放用来调节信号增益及滤波。

图 5. 使用运放建立隔离的阻抗网络

功放 Pop 声分析及解决方案

1 POP 的原因及调试方法

功放 的Pop 声有两种可能的原因:输入阻抗不匹配及不合理的系统时序

输入阻抗不匹配:

输入阻抗不匹配会引起器件启动和关闭时差分输入端产生电压差,这种POP 声是在/SD 电压变化时产生的,发生在功放 输入端的Bias(偏置电压)的建立过程中。遵从匹配输入级阻抗网络的方法即可解决该种POP 声。

不合理的系统时序

如 1 节所述,主芯片启动或关闭时,模拟输出的偏置电压也需要一个建立的过程,而且主芯片上电过程中也有可能输出不可控的POP 声。所以在上电过程中,必须保证功放处于Standby 状态下。避免将前级芯片产生的POP 声放大输出到喇叭。

POP 声的最终表现一样,但根本原因可能有不同,以下是推荐的查找POP 声原因的调试方法:

1. 隔离功放输入和主芯片输出;出现POP 声后,首先要将主芯片的输出断开,并将功放输入电路部分通过电容交流短路到地。此时可以控制/SD 脚电平模拟开关机过程。若POP 声仍然存在,则说明功放启动时P/N 脚对外部网络的充电速度不一致,导致差分输入存在压差所致。若POP 消失,则可进行下一步验证。

2. 确认功放无输入情况下开关无POP 声之后,可使用外部电源给主芯片供电。保持主芯片电源不切断是为了排除主芯片输出在掉电时产生POP 声的影响。此时进行整个系统正常的开关机验证POP 声。若POP 声消除,则可判断主芯片掉电时序和功放的掉电时序不匹配,导致主芯片掉电时产生的POP 声被功放放大输出。部分系统中电源并未完全关闭,系统有待机模式时可用待机芯片的I/O 口进行时序的控制,若系统的开关机是电源硬关断模式则需要进行系统电源时序的优化。部分情况下,需要添加上电/掉电检测电路来控制POP声。

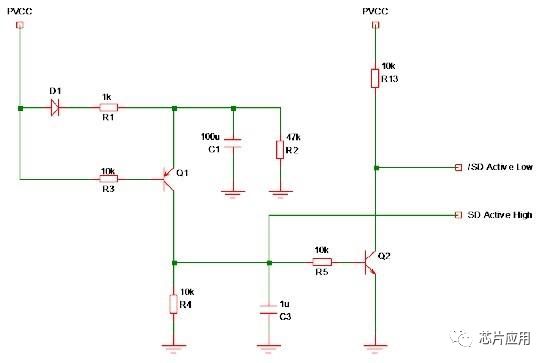

2 掉电检测电路

在使用硬件开关直接关闭主电源的系统中,掉电时的POP 声控制较为困难。因为该类系统无法提前预知系统掉电,无法在掉电之前使用控制器I/O 口静音或关闭功放。这时就必须使用如图76所示的掉电检测电路来解决该问题。该电路可在系统电压跌落初期提供控制信号,使用该控制信号拉低/SD 脚即可在掉电初期快速关闭功放。

掉电检测电路在正常供电时PVCC 会通过二极管D1 和电阻R1 向C1 大电容充电。掉电初期,Q1 的基极电压将随着PVCC 的跌落降低,直到跌落到Q1 三极管打开后,C1 的电压将通过Q1送给Q2 的基极,Q2 导通,/SD 被拉低。根据上述原理,可由以下计算出电压跌落的位置Vdrop:

该例中,PVCC 为12V, Vf 和Veb 为0.7V, 则掉电保护点约在10.3V 左右,与波形图8 吻合。

图 6. 掉电检测电路

图 7. 掉电检测电路示例波形

掉电检测电路在应用时需要注意调整R1 和R2 的数值,选择合适的掉电保护点。避免电源的纹波触发掉电保护电路导致误触发静音。电路中给出了Active High 和Active Low 两种逻辑供用户选择。可以根据功放所需的逻辑自行选用。

-

浅析阻抗匹配及其应用2015-05-05 3069

-

TPA3110D2正常工作过程中产生的POP音,是不是输入阻抗匹配的问题,输入阻抗应该怎么改呢?2024-10-22 561

-

音频输入和功放之间的阻抗匹配2017-10-02 34347

-

电路阻抗匹配设计2010-08-12 1309

-

什么是阻抗匹配2006-09-25 5034

-

基于Ansoft Designer的射频功放电路阻抗匹配优化2009-05-14 3229

-

怎样理解阻抗匹配?2009-11-30 1839

-

什么是阻抗匹配以及为什么要阻抗匹配2015-10-28 1388

-

了解什么是阻抗匹配与阻抗不匹配?2019-03-14 11408

-

怎样理解阻抗匹配_pcb阻抗匹配如何计算2018-05-02 45407

-

阻抗匹配是什么意思_阻抗匹配原理详解2018-05-03 53903

-

阻抗匹配在RFID系统中有什么作用2019-12-20 2640

-

阻抗匹配的原理及应用2022-08-22 5083

-

为什么高频小信号谐振放大器中要考虑阻抗匹配?如何实现阻抗匹配?2023-10-11 3857

-

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?2023-10-30 4203

全部0条评论

快来发表一下你的评论吧 !