同步时序电路原理图图解 同步时序路径约束要求

电子说

描述

基本的同步时序路径约束

先读文章:《时序逻辑电路的建立,保持时间裕量分析》

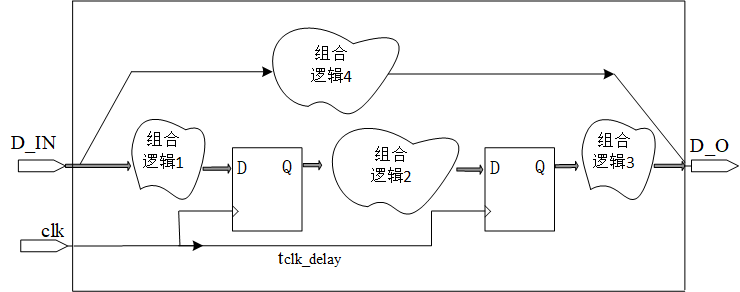

我们设计的同步时序电路示意图如下。

从上面的示意图可知,一个同步时序电路的时序路径无非就是四种:

(1)从输入端口到内部寄存器(从D_IN经过组合逻辑1,到第一个寄存器数据端口D)。

(2)从内部寄存器到内部寄存器(从第一个寄存器的Q端,经过组合逻辑2,到第二个寄存器的D端)。

(3)从内部寄存器到输出端口( 从第二个寄存器的Q端,经过组合逻辑3,到输出端口 D_O端)。

(4)从输入端口到输出端口(从D_IN经过组合逻辑4到达输出端口D_O)。

先看路径(2),从内部寄存器到内部寄存器。如文章《时序逻辑电路的建立,保持时间裕量分析》中的详细描述,要满足如下建立保持时间要求。

建立时间裕量:

tsetup_slack = tcycle-(tcq+tlogic) - tsetup+tclk_delay-tjitter>0

保持时间裕量 :

thold_slack = tcq+tlogic-thold-tclk_delay-tjitter>0

对于EDA来说,tsetup(寄存器建立时间要求),tcq(寄存器输出延时),thold(寄存器保持时间要求)它都是知道的。在忽略tjitter(时钟抖动)的情况下,我们需要告诉EDA我们的时钟周期,tcycle。如此EDA工具就会根据我们的给出的tcycle,去优化寄存器到寄存器之间的组合逻辑2的延时(tlogic)和tclk_delay,去满足建立保持时间裕量要求。EDA也会根据我们给出的tcycle,去计算建立保持时间裕量。

因此此时我们只需要对时钟进行约束,约束示例语句如下(在端口clk上创建的时钟,周期为10ns)。

create_clock -period 10 [get_ports clk]

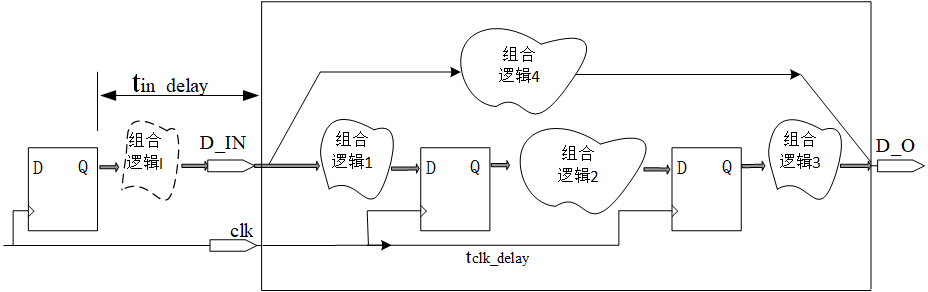

对于路径(1),从输入端口到内部寄存器(从D_IN经过组合逻辑1,到达第一个寄存器的数据端口D),我们需要把上一级的电路示意图也画出来。大家就明白了。如下图所示,上一级的电路模型也可以等效为一个寄存器再通过一个组合逻辑电路。因此时序约束其实也就是变成了,从外部寄存器到内部寄存器之间的时序约束。

从图中可以看到tin_delay(既数据到输入端口的延时)其实等于上一级电路寄存器的输出延时(tcq)加上一级组合逻辑的延时。

此时我们需要满足的建立保持时间要求如下(tlogic1为组合逻辑1的延时)。

建立时间裕量

tsetup_slack = tcycle-tin_delay-tlogic1- tsetup+tclk_delay-tjitter>0

保持时间裕量

thold_slack = tin_delay+tlogic1-thold-tclk_delay-tjitter>0

同样在忽略tjitter的情况下,我们只需要告诉EDA工具tcycle,tin_delay,如此EDA就会根据我们的条件去约束组合逻辑1的延时以及tclk_delay,从而使得电路满足建立保持时间要求。

设置tcycle的方式,上面已经说过。设置输入延时(tin_delay)的约束命令示例如下(-clock用于指定时钟域,2表示设置输入延时为2ns):

set_input_delay -clock clk 2 [get_ports D_IN]

对于输入端口的完整约束示例如下:

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk 2 [get_ports D_IN]

当然对于输入延时的定义也可以用 -max -min去分别定义一个最大值和最小值。在分析建立时间裕量时,EDA工具会用最大值去分析;在分析保持时间裕量时,EDA工具会用最小值去分析。定义示例如下:

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk -max 4 [get_ports D_IN]

set_input_delay -clock clk -min 1 [get_ports D_IN]

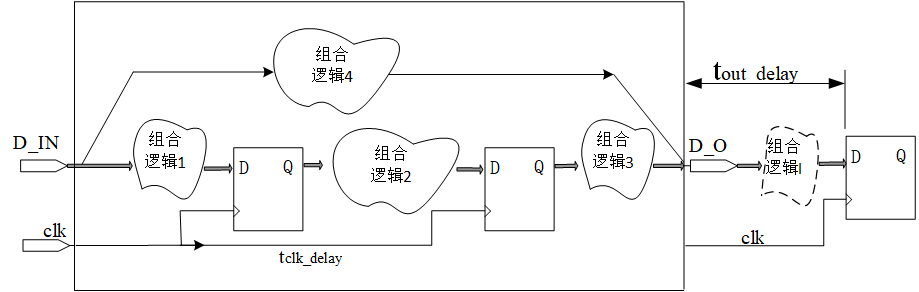

对于路径(3),从内部寄存器到输出端口(从第二个寄存器的Q端经过组合逻辑3到输出端口D_O),同样我们把它的下一级电路示意图也画出来。其下一级电路也是通过组合逻辑送到寄存器这种结构。问题也就可以等效为寄存器到寄存器之间的时序约束。

同样在忽略时钟抖动的情况下,我们需要告诉EDA工具数据从输出端口到下一级电路寄存器的延时tout_delay和tcycle。此时EDA工具就会根据如下要求去优化组合逻辑3的延时tlogic3以及tclk_delay,以及计算静态时序裕量。

建立时间裕量

tsetup_slack = tcycle-tout_delay-tlogic3- tsetup+tclk_delay-tjitter>0

保持时间裕量

thold_slack = tout_delay+tlogic3-thold-tclk_delay-tjitter>0

约束输出延时(tout_delay)的示例如下(-clock 指定时钟域)。

create_clock -name clk -period 10 [get_ports clk]

set_output_delay -clock clk 6 [get_ports D_O]

同样,输出延时也可以用 -max -min指定一个最大值和一个最小值。

create_clock -name clk -period 10 [get_ports clk]

set_output_delay -clock clk -max 6 [get_ports D_O]

set_output_delay -clock clk -min 2 [get_ports D_O]

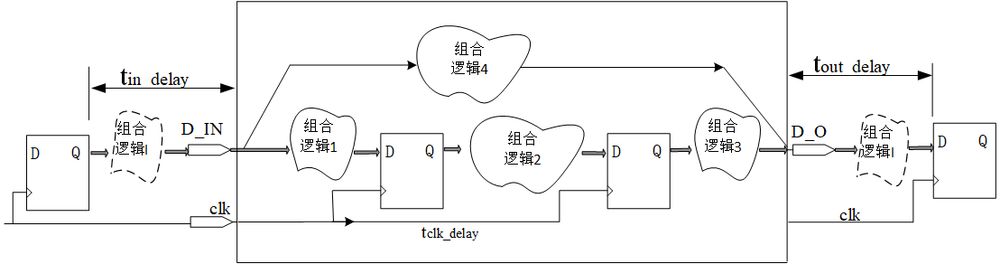

对于路径(4)(从输入端口经过组合逻辑4再到输出端口),这时候我们必须联合上下两级电路来考虑。我们要先明确从上一级电路获取数据的输入延时tin_delay,以及其送到下一级电路的tout_delay。如此EDA工具才知道如何去做组合逻辑4的时序优化与做静态时序计算。

此时需要满足的时序要求如下:

建立时间裕量

tsetup_slack = tcycle-tin_delay-tout_delay -tlogic4- tsetup+tclk_delay-tjitter

保持时间裕量

thold_slack = tin_delay+tout_delay+tlogic4-thold-tclk_delay-tjitter

在忽略时钟抖动的情况下,我们需要约束输入延时,输出延时。示例约束语句如下。

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk 4 [get_ports D_IN]

set_output_delay -clock clk 1 [get_ports D_O]

-

时序电路包括两种类型 时序电路必然存在状态循环对不对2024-02-06 3099

-

FPGA时序约束之时序路径和时序模型2023-08-14 1704

-

同步电路设计中静态时序分析的时序约束和时序路径2023-06-28 2342

-

时序逻辑电路设计之同步计数器2023-05-22 5657

-

什么是同步时序电路和异步时序电路,同步和异步电路的区别?2023-03-25 29896

-

计数器及时序电路2022-07-10 838

-

同步时序电路需要考虑的三个重要的时序参数2020-12-07 8560

-

FPGA案例解析:针对源同步的时序约束2020-11-20 9499

-

同步时序电路设计2018-10-31 1731

-

时序电路的分析与设计方法2018-08-23 3689

-

设计一个同步时序电路2013-03-22 2676

-

基于粒子群算法的同步时序电路初始化2010-05-13 690

-

同步时序电路2010-01-12 5840

-

同步时序逻辑电路2009-09-01 1143

全部0条评论

快来发表一下你的评论吧 !