如何区分FPGA和CPLD?

电子说

描述

如何区分CPLD或FPGA和哪一个更适合自己?这是一个老生常谈的问题,尤其是学生和初学者。如果您也在这个问题上很迷茫,那么就请听小编为您区分FPGA与CPLD。

CPLD

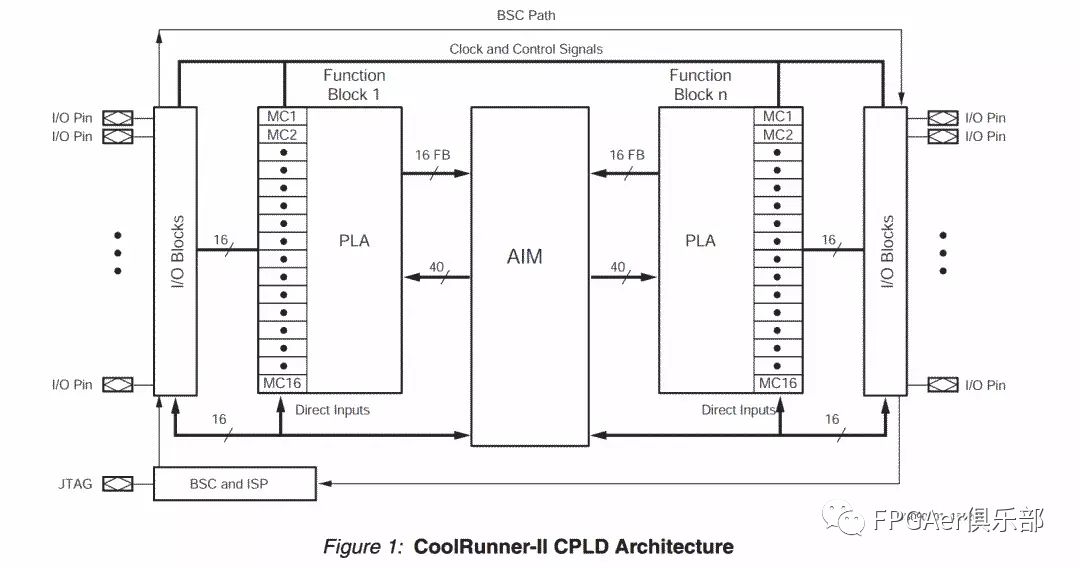

我们先来看看CPLD,在此以Xilinx CoolRunner-II为例。下图是Xilinx CoolRunner-II的架构图。

现在小编为您解释一下上图的内容。

1.该CPLD具有从“功能块1”到“功能块n”开始的功能块很少(在CoolRunner-II CPLD的情况下,此编号范围为2到32)

2.每个功能块的16行输出进入AIM(高级互连矩阵),而40行信号从AIM输入功能块。

3.每个功能块都有16个MacroCell(MC1到MC16)。

4.每个MacroCell都可以访问来自I / O块的16个信号

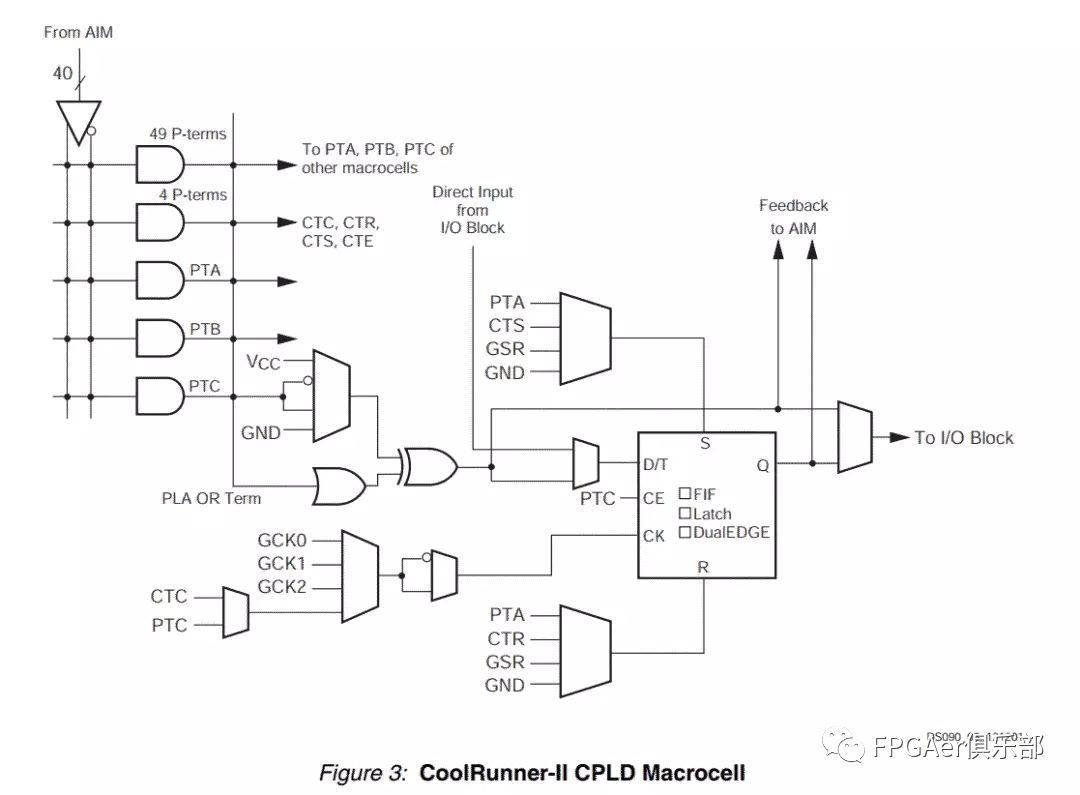

5.MacroCell的结构如下所示。每个宏单元包含1个触发器和PLA阵列的产品和,用户可以利用它来创建组合或顺序逻辑。因此,CoolRunner-II CLPD(XC2C512)中可用的最大触发器数量为512!(记住这个数字,我们将它与FPGA中的触发器数量进行比较)

6.可以对AIM进行编程,以便根据需要互连信号。但正如我们在上面的第二个要点中看到的那样,每个功能块的信号数量都是有限的。

与PLA(programmable Logic Array,可编程逻辑阵列)相同,CPLD在每个宏单元中的逻辑功能通过JTAG上的系统编程(ISP)接口进行电气编程。编程后,这些基于闪存的连接多年来一直保持不变。这为CPLD提供了“即时启动”工作的独特优势。也就是说,CPLD一上电就开始工作,因为程序通过ISP闪存烧入。但FPGA的情况不尽相同,我们后文再讨论。

总结一下,我们可以说,在CPLD中,有几百个功能块(或逻辑块),通常少于1000个,可由单个大型逻辑单元互连访问。

FPGA

虽然制造商没有公开发布确切的FPGA架构,但我们仍然可以获得更高级别的架构,这将有助于理解FPGA及其工作原理。让我们先来看一下Xilinx的的高级示例。

在FPGA中,有许多可配置逻辑块(Configurable Logic Block,CLB )嵌入在可编程互连的“海洋”中。与CPLD的宏单元相比,这些CLB非常复杂,并且可以实现更复杂的逻辑功能。它们主要由查找表(LUT),多路复用器和触发器组成。FPGA可以在单个器件中包含数百万个CLB!数以百万计的触发器(Xilinx VU13P中约为345.6万个触发器),与Xilinx同厂性能最好的CPLD中的512个触发器相比显得非常庞大。逻辑门数量的巨大差异也决定了FPGA的用途。

如上图所示,FPGA还具有用于各种功能的专用硬件,如RAM,高速串行收发器,数字信号处理(DSP)模块,外部存储器控制器,PLL和MMCM,PCIe等!就多种选择和灵活性而言,CPLD与FPGA无法匹敌。

如前文所述,FPGA基于LUT。当FPGA上电时,器件始终为空白。存在称为配置电路的特殊电路,其从外部ROM读取配置数据,并根据外部ROM中存在的用户设计来配置LUT。FPGA配置需要一些时间,FPGA将在配置加载完成后才开始工作。当然也有例外。一些制造商已经提出内置配置闪存的FPGA。即使在这种情况下,配置数据也没有嵌入到结构中,并且仍然适用一些对时间的设置与配置。

CPLD与FPGA比较汇总

小编总结了一个表格,可以概括一下两者的异同。

FPGA即使在运行时也可以改变电路结构!(因为它只是更新具有不同内容的LUT的问题)这称为部分重配置,当FPGA需要继续运行设计并同时根据需要使用不同的设计更新它时非常有用。此功能广泛用于加速计算。

CPLD和FPGA的用途区分

如果设计需要简单的组合逻辑电路,无需进行太多更改,或者需要瞬时接通电路,那么CPLD是不错的选择。否则,对于大多数其他应用,FPGA通常是首选。有时您可以在设计案例中看到CPLD + FPGA的组合设计。在这些案例中,CPLD通常用于实现前面提到的简单组合逻辑功能,并负责“引导”FPGA以及控制整个电路板的复位和引导顺序。因此,根据应用程序,您可能需要在设计中使用它们。

随着AI技术的发展,FPGA又一次站在了风口上——它以内置庞大的逻辑门电路,合理的功耗,在GPU、ASIC之后,为AI从业者提供了一种更为灵活的算法实现方案。在此业态下,FPGA的发展也会给它的传统应用领域——以高速通信为主的通信领域和以驱动组合逻辑芯片为主的LED显示行业注入新的发展契机。

-

CPLD和FPGA的区别是什么2023-07-03 11367

-

常用FPGA/CPLD设计思想与技巧2023-05-18 1153

-

Altera FPGA CPLD学习笔记2021-09-18 1692

-

如何区分CPLD与FPGA,怎么选择?2020-10-30 1506

-

CPLD和FPGA这两者到底有什么区别呢2019-09-13 6151

-

FPGA与CPLD该怎么区分?2019-08-08 2047

-

FPGA与CPLD怎么区分2019-07-01 2614

-

FPGA教程之CPLD与FPGA的基础知识说明2019-02-27 1720

-

如何区分FPGA与CPLD?本文告诉你答案!2018-09-04 2960

-

CPLD和FPGA两者的区别2018-05-24 51124

-

关于CPLD和FPGA的区别2017-09-18 1169

-

FPGA/CPLD的设计思想2016-02-17 836

-

altera fpga/cpld设计2009-07-10 880

-

Altera FPGA/CPLD设计(高级篇)2009-02-12 4621

全部0条评论

快来发表一下你的评论吧 !